UVM实战 汇总与附录

时间:2022-11-21

第一章

主要介绍uvm发展史,验证内容

第二章

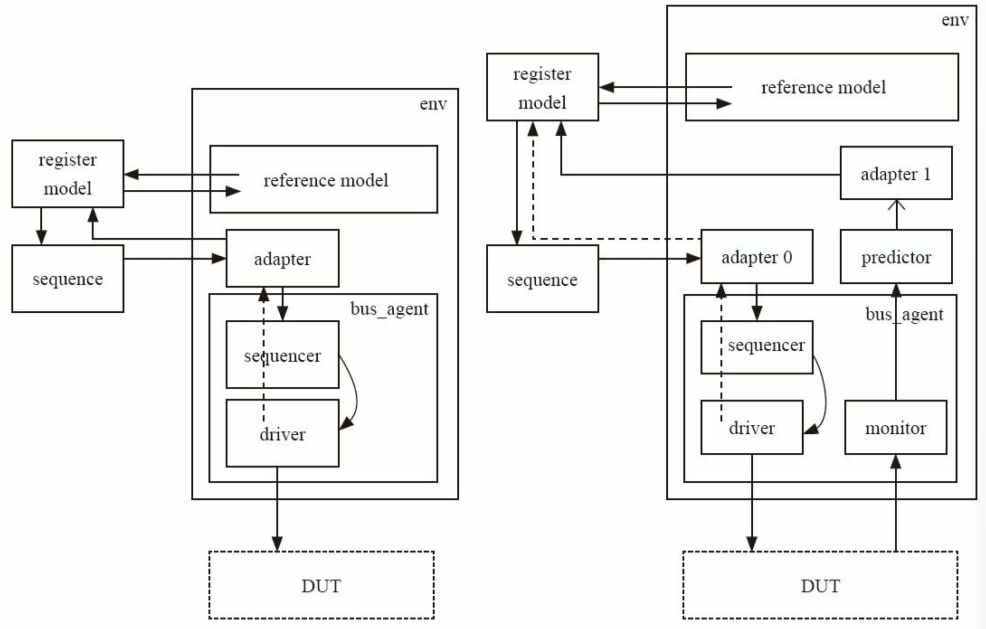

- autp predict验证平台组成

- 最简单的验证平台:my_driver与top_tb组成

第一章

1.2 学了UVM之后能做什么

- 使用sequence机制、factory机制、callback机制、寄存器模型(register model)等

- 验证基本常识

- 如何实现代码可重复性

机制索引

- phase机制(5.1)

- objection机制(5.2)

- sequence机制(2.4, 6)

- facory机制(8)

- file automation机制

- config_db机制

- callback机制(9)

特性检索

- TLM

- drain_time,撤销objection的延时(5.2.4)

- domain(5.3)

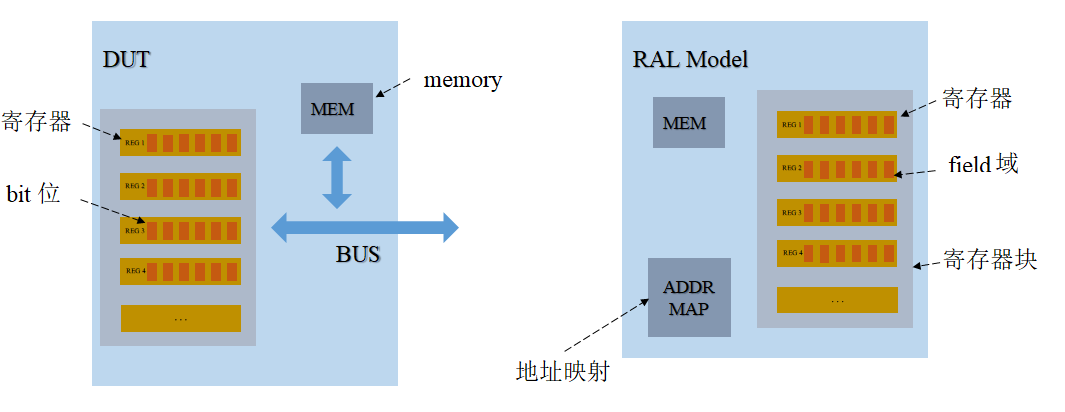

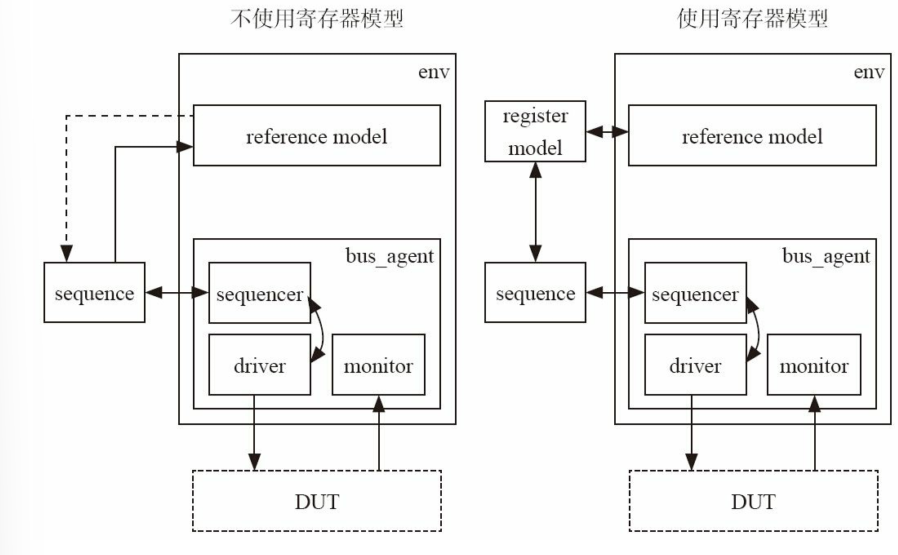

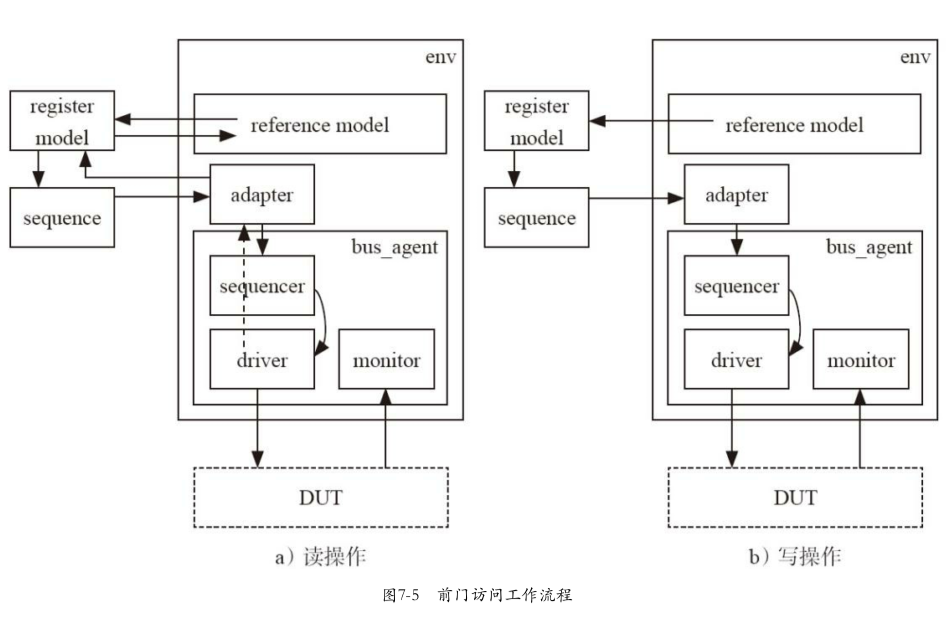

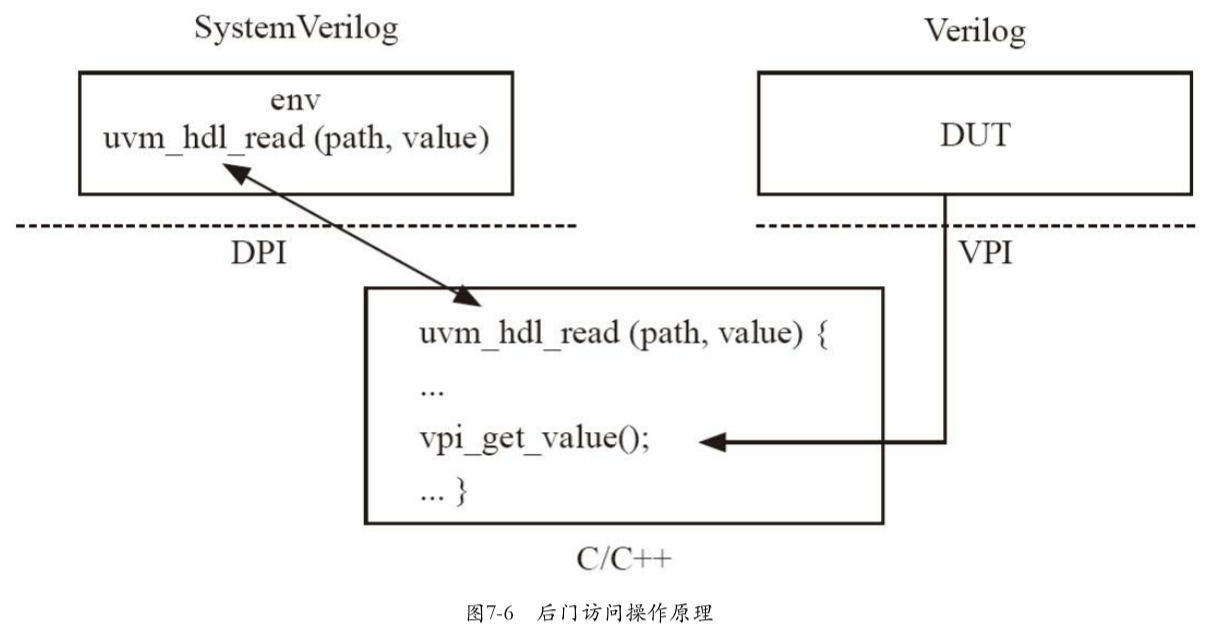

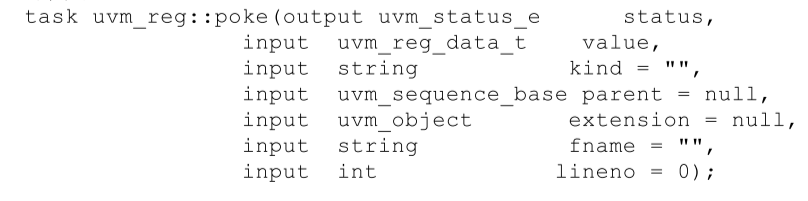

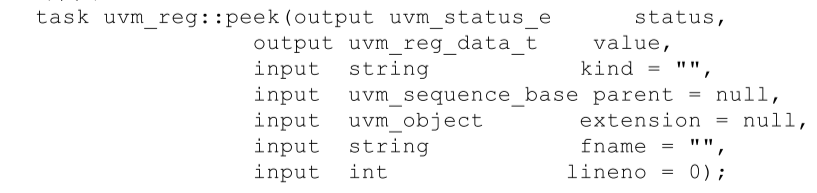

- register model

第二章

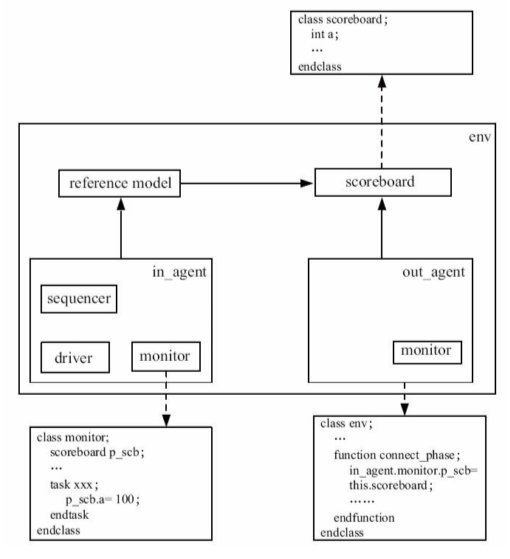

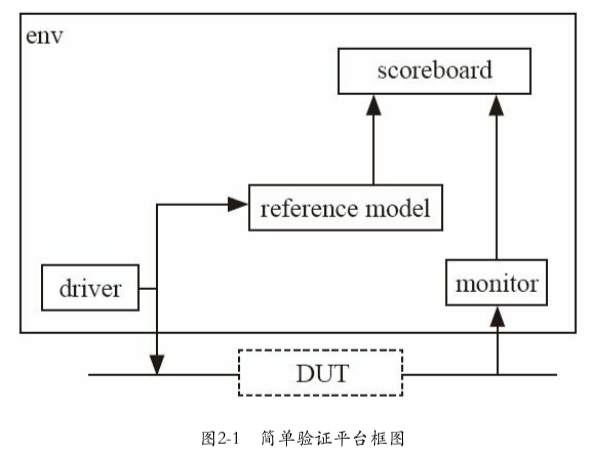

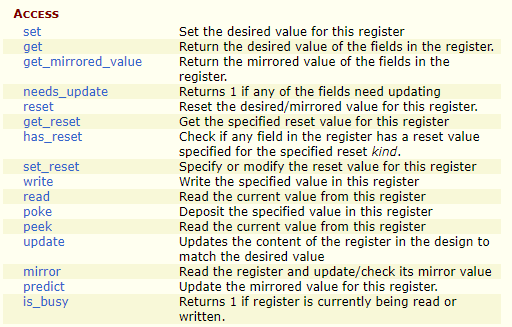

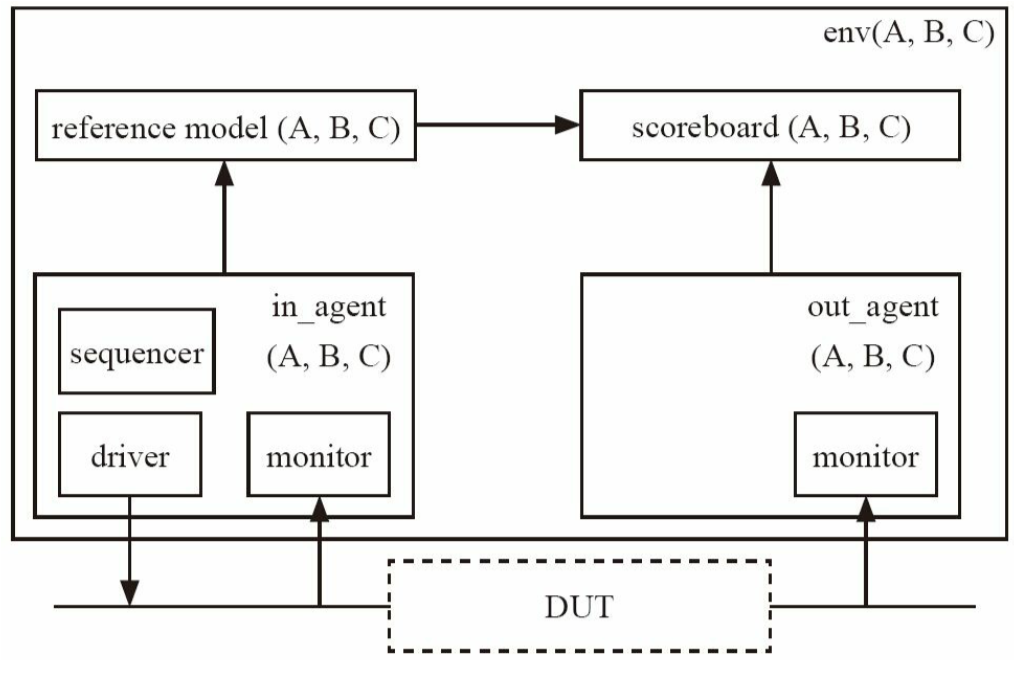

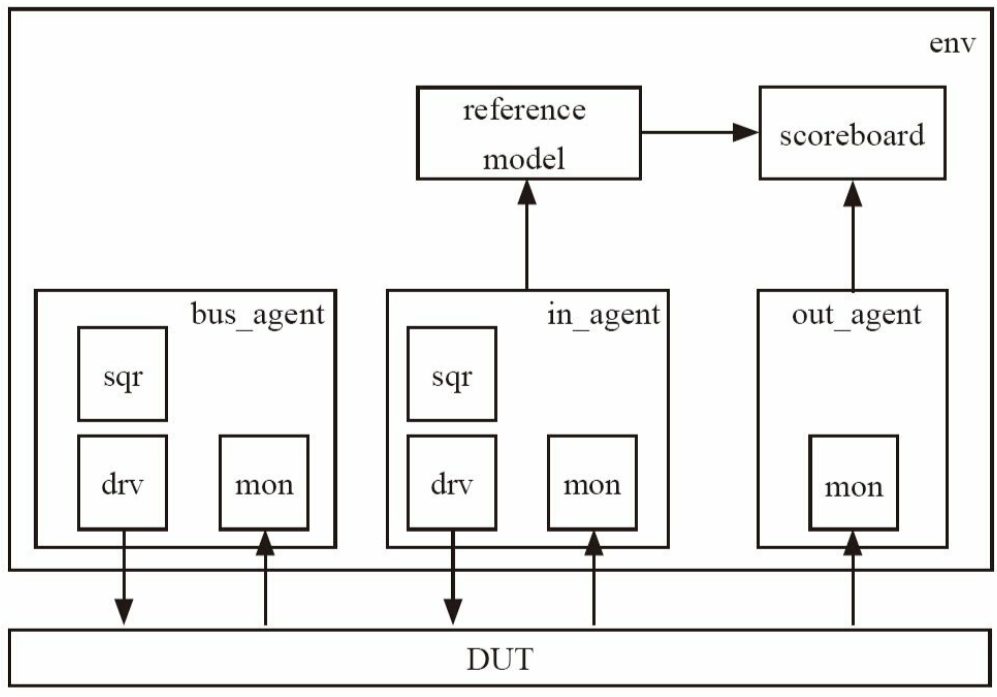

2.1 验证平台组成

验证用于找出DUT中的bug,这个过程通常是把DUT放入一个验证平台中来实现的

一个验证平台要实现如下基本功能:

- 激励的功能:driver

- 各种激励:正常激励、异常激励

- 判断是否符合预期:scoreboard/checker

- 收集DUT输出并传递给sb:monitor

- reference model

2.2 只有driver的验证平台

2.2.1 最简单的验证平台

1. driver是验证平台最基本的组件

如何搭建driver?

- UVM是一个库,在这个库中,几乎所有的东西都是使用类(class)来实现的,如:driver、 monitor、reference model、scoreboard等组成部分都是类

- 类有函数(function)和任务(task),通过这些函数和任务可以完成driver的输出激励功能

- 使用UVM的第一条原则是:验证平台中所有的组件应该派生自UVM中的类

2. 定义一个my_driver类

1 | |

new参数

- uvm_driver的类的new函数有两个参数(这两个参数是由uvm_component要求的),一个是string类型的name,一个是uvm_component类型的parent

- 每一个派生自uvm_component或其派生类的类在其new函数中要指明两个参数:name和parent

phase

- driver所做的事情几乎都在main_phase中完成

UVM由phase来管理验证平台的运行,这些phase统一以xxxx_phase来命名,且都有一个类型为uvm_phase、名字为phase的参数

可以简单地认为, 实现一个driver等于实现其main_phase

`uvm_info宏:与Verilog中display语句的功能类似,比display语句更加强大

- 三个参数,第一个参数是字符串,用于把打印的信息归类;第二个参数也是字符串,是具体需要打印的信息;第三个参数则是冗余级别

- 非常关键可设置为UVM_LOW,可有可无可设置为UVM_HIGH,介于两者之间是UVM_MEDIUM。UVM默认只显示UVM_MEDIUM或者UVM_LOW的信息,本书3.4.1节会讲

uvm_info打印内容

UVM_INFO my_driver.sv(20)@48500000:drv[my_driver]data is drived

- my_driver.sv(20):指明此条打印信息的来源,其中括号里的数字表示原始的uvm_info打印语句在my_driver.sv中的行号

- 48500000:表明此条信息的打印时间

- drv:这是driver在UVM树中的路径索引

- UVM采用树形结构,对于树中任何一个结点,都有一个与其相应的字符串类型的 路径索引。路径索引可以通过

get_full_name函数来获取,把下列代码加入任何UVM树的结点中就可以得知当前结点的路径索引:$display("the full name of current component is: %s", get_full_name());

- [my_driver]:方括号中显示的信息即调用uvm_info宏时传递的第一个参数

- data is drived:表明宏最终打印的信息

3. 实例化一对象

1 | |

`include uvm_macros.svh包含了众多的宏定义,只需要包含一 次import uvm_pkg::*;导入uvm_pkg库- new的时候第二个参数一般不为null

- 显示调用

main_phase $finish();结束仿真

2.2.2 加入factory机制

上节的实例化及main_phase的显式调用,只使用简单的SystemVerilog也可完成

本节介绍:自动创建一个类的实例并调用其中的函数(function)和任务(task)

1. 使用factory机制重写my_driver

1 | |

factory机制之宏

`uvm_component_utils这个宏所做的事情非常多,其中之一就是将my_driver登记在 UVM内部的一张表中

所有派生自uvm_component及其派生类的类都应该使用uvm_component_utils宏注册

这张表是factory功能实现的基础。只要在定义一个新的类时使用这个宏,就相当于把这个类注册到了这张表中。有关内容深入解释在后面

2. 使用factory机制重写top_tb

1 | |

运行top_tb后输出:

1 | |

并没有输出:”data is drived”,关于这个问题,牵涉UVM的objection机制

run_test("注册的类名")使用

run_test("注册的类名")代替my_driver实例化与显式调用

- run_test创建一个my_driver的实例,并且会自动调用my_driver的main_phase

2.2.3 加入objection机制

上一节只输出了“main_phase is called”,但是“data is drived”并没有输出,因为main_phase被杀死了

1. objection机制

UVM中通过objection机制来控制验证平台的关闭,在每个phase中,UVM会检查是否有objection被提起 (

raise_objection)。如果有,则等待这个objection被撤销(drop_objection)后停止仿真;如果没有,则马上结束当前phase

raise_objection和drop_objection总是成对出raise_objection语句必须在main_phase中第一个消耗仿真时间 [1]的语句之前所谓仿真时间,是指$time函数打印出的时间。与之相对的还有实际仿真中所消耗的CPU时间,通常说一个测试用例的运行时间 即指CPU 时间,为了与仿真时间相区分,本书统一把这种时间称为运行时间。

如

$display语句是不消耗仿真时间的,这些语句可 以放在raise_objection之前,但是类似@(posedge top.clk)等语句是要消耗仿真时间的。按照如下的方式使用raise_objection是无法

起到作用的

- 使用objection机制的my_driver

1 | |

2.2.4 加入virtual interrface

1. 绝对路径遇到的问题:

driver中等待时钟事件(@posedge top.clk)、给DUT中输入端口赋值(top.rx_dv<=1‘b1)都是使用绝对路径,绝对路径的使用大大减弱了验证平台的可移植性。一个最简单的例子就是假如clk信号的层次从top.clk变成了top.clk_inst.clk,那么就需要对driver中的相关代码做大量修改。因此,从根本上来说,应该尽量杜绝在验证平台中使用绝对路径

2. 解决方案①使用宏

使用`TOP代替上文中的top,但是如果clk_inst变了照样解决不了,还要改

3. 解决方法②使用接口

定义接口

1 | |

在top_tb中实例化DUT时,就可以直接使用接口

1 | |

4. 如何在driver(类)中使用接口

不能直接,这种方式只能在module模块中才能实现

1 | |

在类中应该使用虚接口virtual interface:

1 | |

替代后的全部my_driver代码如下,可见绝对路径已消除

1 | |

5. 如何链接top_tb的input_if与my_driver中的vif(config_db机制)

使用run_test进行实例化,从而无法直接引用my_driver实例

使用config_db机制

config_db机制:

config_db用来在端口间传递数据(端口级),分为set和get两步操作

uvm_config_db#(?)::set操作,可以简单地理解成是“寄信”uvm_config_db#(?)::get则相当于是“收信”

在top_tb中执行set操作:

1 | |

在my_driver中,执行get操作:

1 | |

build_phase

- 定义:与main_phase一样,build_phase也是UVM中内建的一个phase

- 执行顺序:当UVM启动后,会自动执行 build_phase,运行在new之后,main_phase之前

- 主要作用:主要通过config_db的set和get操作来传递一些数据, 以及实例化成员变量等

- 使用注意事项:需要在build_phase中调用

super.build_phase(phase),因为父类的build_phase中执行了一些必要的操作,这里必须显式调用并执行- 与main_phase不同:main_phase是任务,build_phase是函数不消耗仿真时间

`uvm_fatal宏

- 参数:两个与

`uvm_info前两个参数意义一样- 主要作用:表示验证平台出现了重大问题而无法继续下去,必须停止仿真并做相应的检查

- 与

`uvm_info不同:会调用$finish()结束仿真

config_db的参数

- config_db的set和get函数都有四个参数,且第三个参数必须完全一致

uvm_config_db::set

- 第二个参数表示的是路径索引(2.2.1节提到

`uvm_info中的路径索引)

- run_test创建的实例名为

uvm_test_top,无论传给run_test参数是什么创建的实例名都是uvm_test_top- 第四个参数表示要将哪个interface 通过config_db传递给my_driver

uvm_config_db::get

- 第四个参数表示把得到的interface传递给哪个my_driver的成员变量

参数化:

uvm_config_db#(virtual my_if)是一个参数化的类,其参数就是要寄信的类型- 如果要传递一个int类型:

uvm_config_db#(int)::set

2.3 为验证平台加入各个组件

2.2节的操作基于信号级,本节引入scoreboard、reference model、monitor这些组件是基于transaciton

2.3.1 加入transaction

transaction的概念:transaction就是用于模拟物理协议/以太网协议/…,一 笔transaction就是一个包

1. 一个简单的transaction定义

1 | |

uvm_sequence_itemmy_transaction的基类是uvm_sequence_item,uvm_sequence_item的祖先是

uvm_object

uvm_object_utils

- 不使用

uvm_component_utils而使用` uvm_object_utils的原因:

- transaction不同于driver等组件,具有生命周期,这种类一般派生自uvm_object或uvm_object的派生类

post_randomize

post_randomize是SystemVerilog中提供的一个函数,

当某个类的实例的randomize函数被调用后,post_randomize会紧随其后无条件地被调用

2. driver驱动transaction

1 | |

流程:

① 随机化:main_phase中执行transactin的randomize()

② 数据入列:main_phase执行数据入列函数,把transaction压入data_q

SystemVerlog提供的流操作符实现

IEEE Standard for SystemVerilog—Unified Hardware Design,Specification,and Verification Language 的11.4.14章

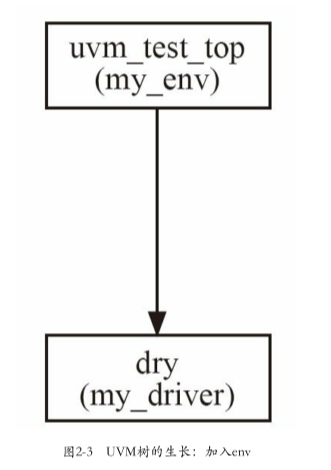

2.3.2 加入env

我们在哪对各种组件例化?

- (不可行)top_tb中使用run_test不行,因为run_test只能实例化一个实例

- (不可行)top_tb中直接new不行,这样run_test没意义了

- (正确的)引入一个容器类,在这个类里面例化各种组件,此时run_test的参数不再是my_driver而是容器类。uvm中使用继承自

uvm_env的子类,来表示这个容器类

1. 定义my_env

1 | |

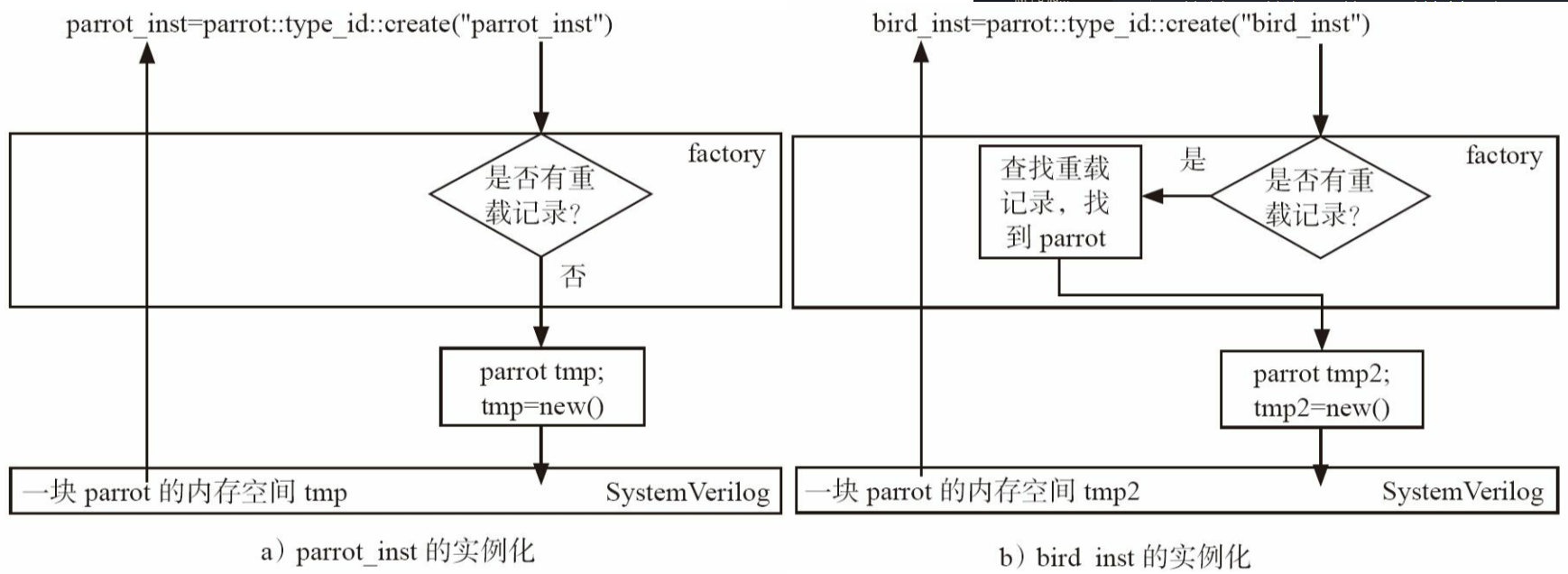

类名::type_id::create

- factory机制带来的独特的实例化方式,只有factory注册过的类可以这种方式例化(代替new)

- 好处:后面可以用到factory中强大的重载功能

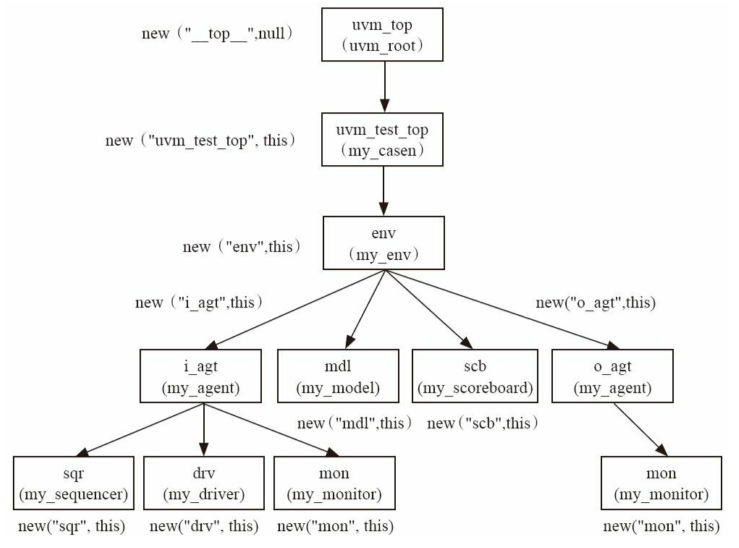

2. 树形结构——回顾my_driver参数2

1 | |

- name:实例名称

- parent:由于是在uvm_env例化,则my_driver的drv实例是my_env

- 建立了树形结构

3. build_phase顺序

build_phase的执行遵照从树根到树叶的顺序,当把整棵树的build_phase都执行完毕后,再执行后面的phase

因此,先执行my_env的build_phase,再执行my_driver的build_phase

4. 修改config_db

树根始终是run_test创建的uvm_test_top,这里uvm_test_top对象代表了一个my_env类

我们为啥要修改config_db?

答:我们加了一个env,你忘了吗

假如在my_env中实例化一个my_driver为my_drv:

1 | |

则在top_tb.sv中修改为:

1 | |

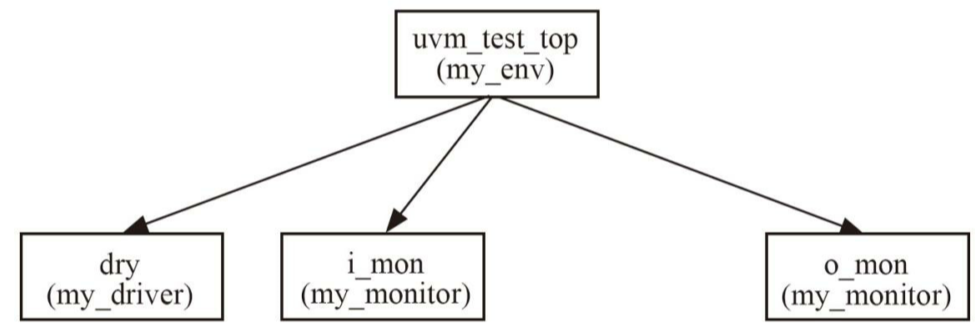

2.3.3 加入monitor

monitor作用:收集DUT行为

monitor内容:收集DUT端口数据,转换为transaction后交给后续组件(与driver相反)

driver内容:把transaction数据变为DUT端口级别,并驱动到DUT

1 | |

流程:

数据入列:main_phase执行数据入列函数,把transaction压入data_q

永不停歇

由于monitor需要时刻收集数据,永不停歇,所以在main_phase中使用

while(1)来实现对比monitor中的collect_one_pkt与driver中的drv_one_pkt:

- 两者代码非常相似

- 当收集完一个transaction后, 通过my_print函数将其打印出来

- my_printf在my_transaction中定义

transaction中定义的my_printf:

1 | |

env中对组件的例化:

1 | |

实例化两个monitor

- 一个用于检测DUT输入

- 一个用于检测DUT输出

为什么输入也monitor?

这个答案仁者见仁,智者见智。这里还是推荐使用monitor,原因是:

- 第一,在一个大型的项目中,driver根据某一协议发送数据,而 monitor根据这种协议收集数据,如果driver和monitor由不同人员实现,那么可以大大减少其中任何一方对协议理解的错误

- 第二,在后文将会看到,在实现代码重用时,使用monitor是非常有必要的

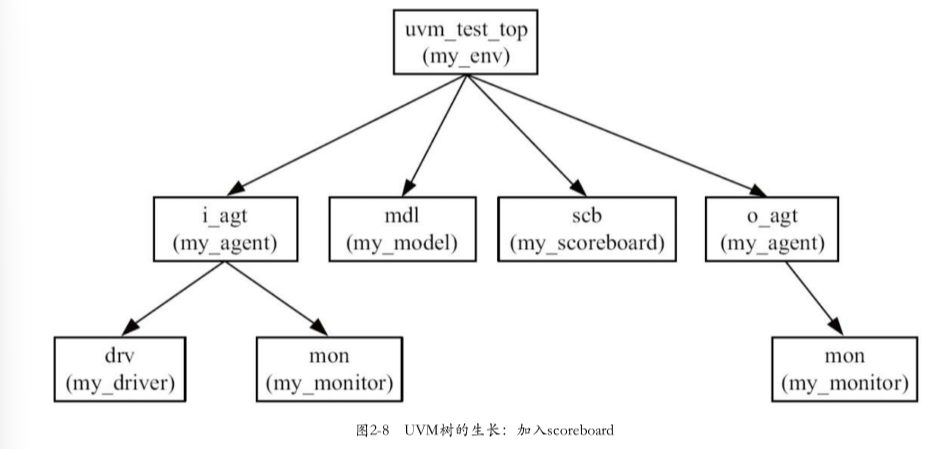

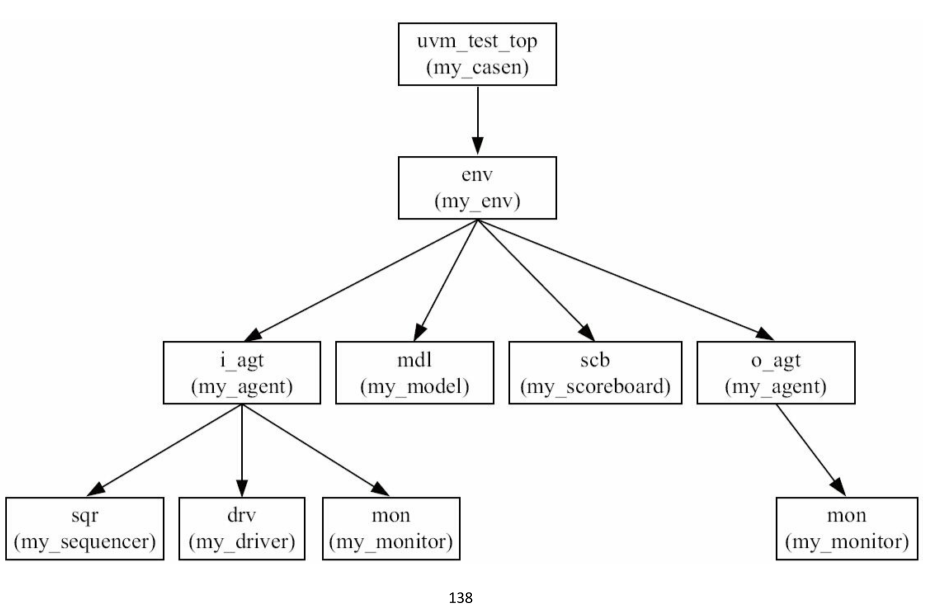

2. 现在的树结构

3. top_tb中config_db修改

使用config_db将input_if和output_if传递给两个monitor,从而完成端口连接

1 | |

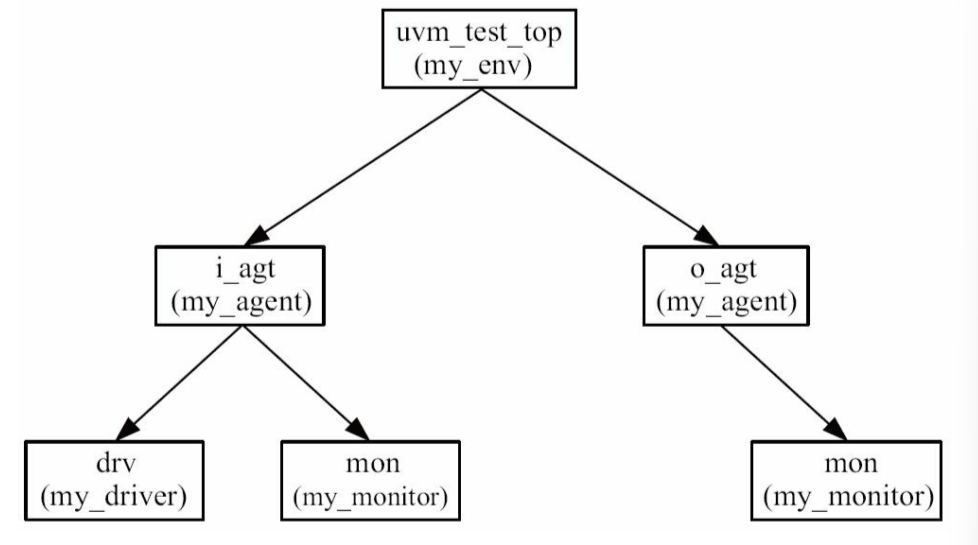

2.3.4 封装成agent

driver与monitor代码相似(本质处理同一种协议)

因此UVM常把二者封装在一起,成为agent

不同的agent就代表了不同的协议

1. my_agent定义

1 | |

uvm_agent

- 所有agent派生自此类

is_active

is_active是uvm_agent的一个成员变量,类型为uvm_active_passive_enum是一个枚举类型- 默认为

UVM_PASSIVE

uvm_active_passive_enum:

typedef enum bit { UVM_PASSIVE=0, UVM_ACTIVE=1 } uvm_active_passive_enum;UVM_PASSIVE:意味着输入端口,无需驱动任何信号,只做检查信号(即只要monitor不要driver)UVM_ACTIVE:意味着输出端口,需驱动任何信号

2. 修改env中对driver和monitor的实例化(同时配置is_active)

1 | |

3. 目前树结构

4. config_db修改端口连接

1 | |

(补充)5.用config_db也可以传is_active

背景:使用new实例化时,无法传递is_active。此时使用config_db机制可以传递is_active

注意!:UVM中约定俗成的还是在build_phase中完成实例化工作。因此,强烈建议仅在build_phase中完成实例化

1 | |

2.3.5 加入reference model

作用:完成与DUT相同功能

输出:被scoreboard接收

1. 定义my_model

1 | |

此reference model就是单纯使用transaction中的my_copy函数,复制一份从i_agt得到的transaction,再传递到后级的scoreboard

reference和其他组件一样,再env中被实例化

2. 目前的树结构

3. transaction的传输

目前传输:

i_agt -> ref -> scoreboard

i_agt -> dut(目前还没提到DUT模块在哪)

TLM(Transaction Level Modeling)

UVM一般使用TLM(Transaction Level Modeling)实现component之间的transaction通信

TLM有多种实现方式:

- 发送的其中一种方法使用

uvm_analysis_port- 接收的其中一种方法使用

uvm_blocking_get_port- 连接:在此基础上还需要再env上定义一个

uvm_tlm_analysis_fifo(一个fifo)将二者连在一起

uvm_analysis_port是TLM发送的实现方式的一种

- 定义:

uvm_analysis_port #(my_transaction) ap;- 参数化的类,参数为需要传递数据的类型(本节中为my_transaction)

- 通过调用内建函数

write完成发送- 非阻塞的

uvm_blocking_get_port是TLM接收的实现方式的一种

- 定义:

uvm_blocking_get_port #(my_transaction) port;- 参数化的类,参数为需要传递数据的类型(本节中为my_transaction)

- 通过调用内建函数

get完成接收

uvm_tlm_analysis_fifo是TLM连接的实现方式的一种

- 定义:

uvm_tlm_analysis_fifo #(my_transaction) agt_mdl_fifo;参数化的类,参数为需要传递数据的类型(本节中为my_transaction)

具体连接方法:

- 通过在connect_phase中,分别层次化调用monitor中的

uvm_analysis_port与model中的uvm_blocking_get_port两种port的内建函数connect完成发送与接收的连接- 连接时,需要调用

uvm_tlm_analysis_fifo中用于指示端口类型的成员变量:analysis_export与blocking_get_export为什么需要一个fifo?为啥不直接把monitor中的analysis_port和model中的blocking_get_port连接?

- analysis_port是非阻塞性质的,ap.write函数调用完成后马上返回,不会等待数据被接收。假如当write函数调用时, blocking_get_port正在忙于其他事情,而没有准备好接收新的数据时,此时被write函数写入的my_transaction就需要一个暂存的位置,这就是fifo

connect_phase

- 在build_phase之后马上执行

- 与build_phase的同级执行顺序不同,connect_phase从树叶到叶根(从小到大)

- 即:先执行driver和monitor的connect_phase,再执行agent的connect_phase,最后执行env的connect_phase

- 这样做有利于在实例化组件之后,进行层次化连接(见本节总结)

4. 使用uvm_analysis_port发送

my_monitor中:

- 定义一个

uvm_analysis_port类型的port - 在build_phase中实例化

- 当准备好一个transaction后,在main_phase中写入该port

- 写入port通过调用它的内建函数

write实现

- 写入port通过调用它的内建函数

如下:

1 | |

1 | |

5. 使用uvm_blocking_get_port接收

在model中:

- 定义一个

uvm_blocking_get_port类型的port - 在build_phase中实例化

- 不断读取i_agt从此port发送来的transaction

- 从port读取通过调用它的内建函数

get实现

- 从port读取通过调用它的内建函数

如下:

1 | |

1 | |

6. 使用uvm_tlm_analysis_fifo连接

在env中:

- 定义一个

uvm_tlm_analysis_fifo类型的fifo,一个 - 在build_phase中实例化

uvm_tlm_analysis_fifo- 注意:无需对env中的ap和port例化,他俩在monitor和model中已经被例化过了,这里只是做调用

- 在connect_phase中进行连接

- 发送这么连接到fifo:

i_agt.ap.connect(agt_mdl_fifo.analysis_export); - 接收这么连接到fifo:

model.port.connect(agt_mdl_fifo.blocking_get_export);agt_mdl_fifo:一个uvm_tlm_analysis_fifo

- 发送这么连接到fifo:

如下:

1 | |

1 | |

6. 总结一下

- 主要目的:model需要得到从i_agt来的transaction

方式:

- i_agt发送

- model接收

- env建立fifo并连接

实例化位置:

- i_monitor发送,因此

uvm_analysis_port在i_monitor中实例化 - i_agt实例化i_monitor,为了方便引用,因此在这里定义了一个指向i_monitor.ap的指针

- model中接收,因此

uvm_blocking_get_port在model中实例化 - env中实例化一个

uvm_tlm_analysis_fifo,并实例化各种组件,通过层次化引用到ap和port

- i_monitor发送,因此

- 重要执行顺序:

- env在build_phase中实例化agent

- agent在build_phase中实例化i_monitor

- agent在connect_phase中引用i_monitor.ap

- env在conncet_phase中引用i_monitor.ap和model.port,并进行连接

为什么是i_monitor发送?

- 因为driver是给到dut的,基于信号级;model是基于transaction,因此需要i_monitor转换后的

2.3.6 加入scoreboard

用于比较dut与ref的输出

1.scoreboard定义

1 | |

流程:

- 建立两个进程

- 进程1:接收

exp_port(ref)一个trans到队列expect_queue中- 进程2:

- 从

act_port(dut)接收一个trans为get_actual- expect_queue弹出一个trans到tmp_tran

- 调用get_actual.compare函数

数据:

scoreboard比较的数据:

- 来自reference model的port,通过端口exp_port获取

- 来自monitor的o_agt,通过端口act_port获取

- 你可能好奇为什么DUT是通过monitor的o_agt获取到scoreboard的?你个笨蛋!DUT是直接和o_agt连接的,把数据打包为事务级(driver相反,把事务级转为端口级)

端口与对应组件(2.3.5)

- scoreboard:act_port, exp_port

- monitor:o_agt

- reference model:port

2.实例化scoreboard

在my_env中实例化scoreboard

2.3.7 加入field_automation机制

用于在transaction中定义变量,从而可以用到uvm的transaction函数

1.my_transaction定义修改

1 | |

file_automation机制>

流程:

uvm_object_utils_begin与`uvm_object_utils_end划定file_automation定义的范围- 针对不同数据类型调用不同宏进行变量定义

uvm_field_intuvm_field_array_int经过以上步骤,可以直接调用定义了这些变量的类的方法:

copycomparepack_bytesunpack_bytes

2.my_model与scoreboard中直接调用file_automation带来的方法

1 | |

1 | |

3.引入file_automation的好处/driver与monitor的定义简化

好处:引入field_automation机制的另外一大好处是简化了driver和monitor。在2.3.1节及2.3.3节中,my_driver的drv_one_pkt任务和 my_monitor的collect_one_pkt任务代码很长,但是几乎都是一些重复性的代码

使用field_automation机制后,drv_one_pkt任务可以 简化为:

1 | |

pack流程:

- 直接调用

pack_bytes对比:

- pack_bytes将tr中所有的字段变成byte流放入data_q中

- 在2.3.1节中是手工地将所有字段放入data_q中的。 pack_bytes极大地减少了代码量

my_monitor的collect_one_pkt可以简化成:

1 | |

unpack流程,括号内表示解释:

- 定义一个接收data_q的动态数组,用作

unpack_bytes函数参数(unpack_bytes函数的输入参数必须是一个动态数组,所以需要先把收集到的、放在data_q中的数据复制到一个动态数组中,这里使用到的是data_array)- 由于tr在定义字段的时候使用到了一个动态数组字段,这里的需要指定大小后才能接收到tr的字段里,讲道理我感觉可以在main_phase就指定了(由于在tr中的pload是一个动态数组,所以需要在调用

unpack_bytes之前指定其大小,这样unpack_bytes函数才能正常工作)- 调用

unpack_bytes打包成的数据流顺序:

在把所有的字段变成byte流放入data_q中时,字段按照uvm_field系列宏书写的顺序排列

在上述代码中是先放入dmac,再依次放入smac、ether_type、pload、crc

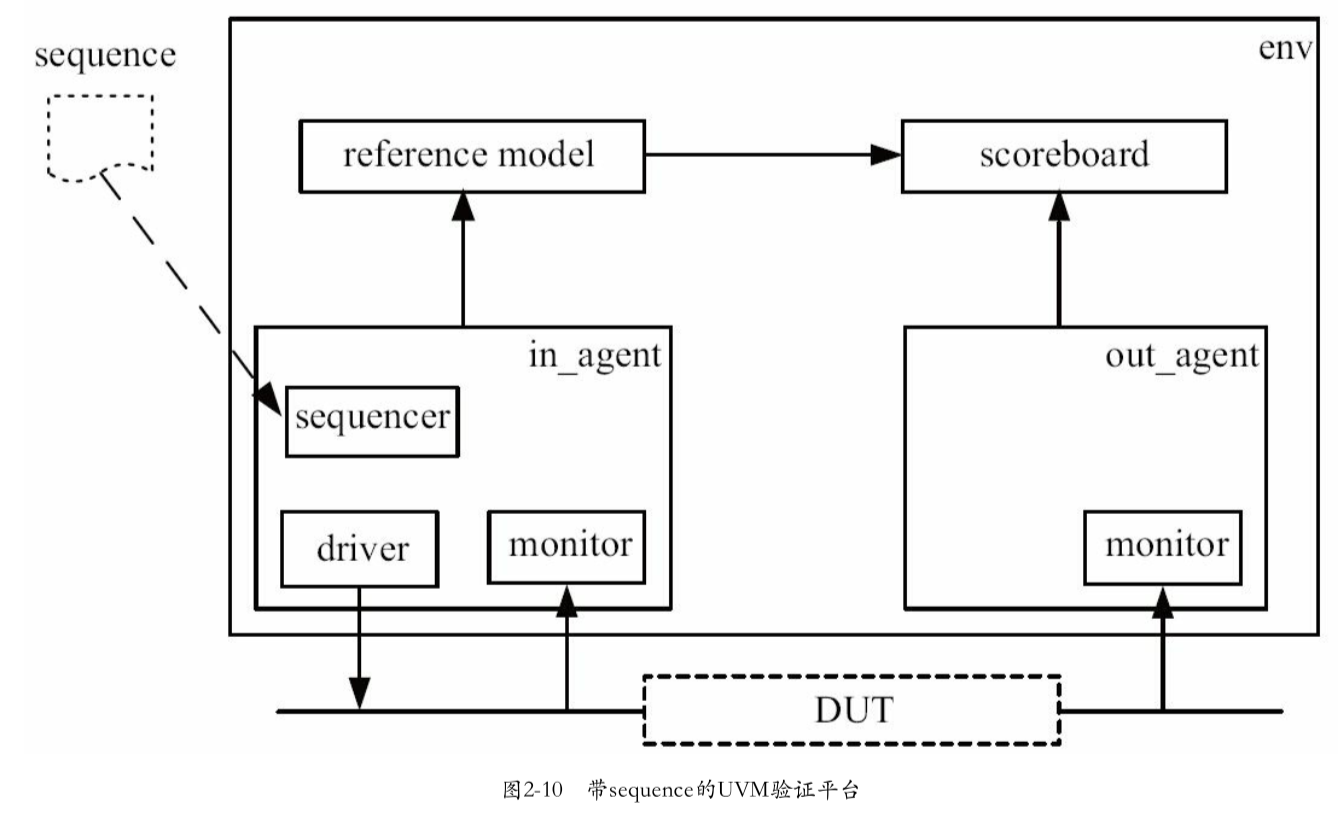

2.4 UVM的终极大作:sequence机制

2.4.1 在验证平台中加入sequencer

功能:sequence机制用于产生激励

区别:前面的例子中激励都是在driver中产生的,但是在一个规范化的UVM验证平台中,driver只负责驱动transaction,不负责生产transaction

sequence机制两大组成部分:

- sequence

- sequencer

1.定义一个sequencer

1 | |

流程:

uvm_sequencer是一个参数化的类,参数为自定义的transaction- 派生自

uvm_sequencer- 使用

`uvm_component_utils进行注册与其他组件的关系:

- sequencer产生transaction

- driver接收transaction

2.有关派生自参数化的类

my_driver定义修正

之前定义的my_driver时都是直接从

uvm_driver派生的,即class my_driver extends uvm_driver;,这是种不常见的写法因为

uvm_driver也是一个参数化的类,应该在定义时指明driver要驱动的transaction类型,这么写是正确的class my_driver extends uvm_driver#(my_transaction);使用参数的好处

可以直接使用

uvm_driver中的某些预先定义好的成员变量如

uvm_driver中有成员变量req,它的类型就是传递给uvm_driver的参数,在这里就是my_transaction,可以直接使用req

参数定义后的my_driver中,带来的好处(req直接使用),注:这里依然是在driver中产生激励,下一节从driver中移除

1 | |

3.把sequencer放入到agent中

在完成sequencer的定义后,由于sequencer与driver的关系非常密切,因此要把其加入agent中

1 | |

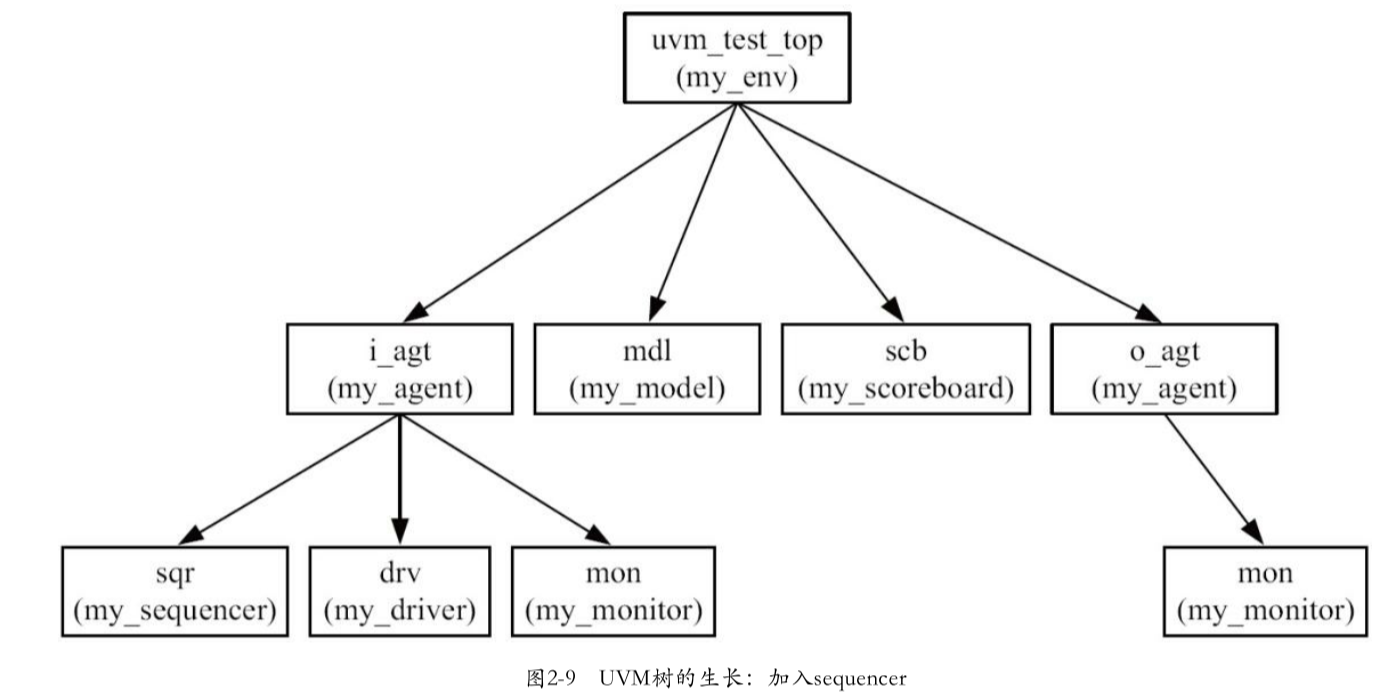

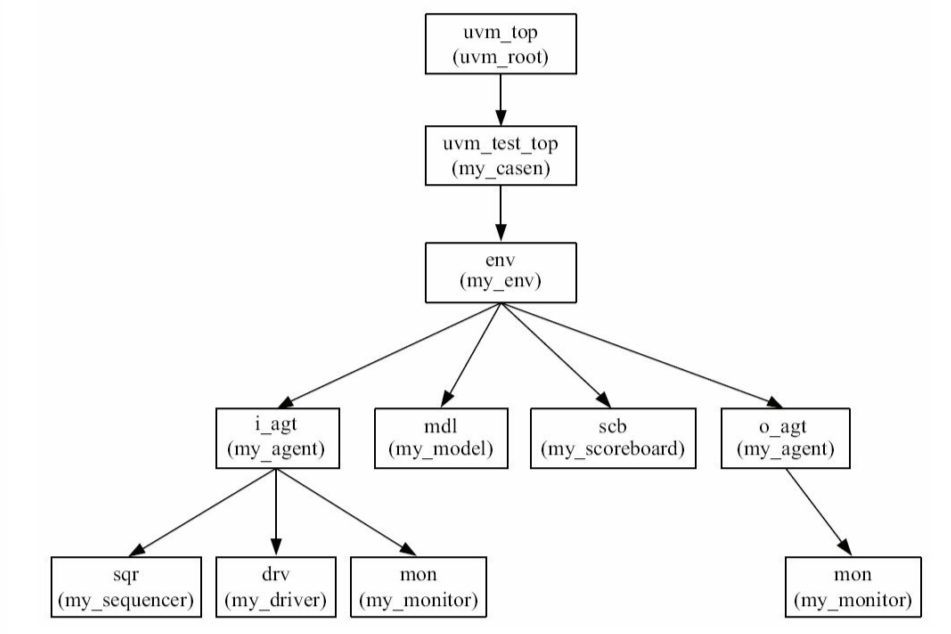

4.加入sequencer后的UVM树结构图

2.4.2 sequence机制

sequence不属于验证平台的任何一部分,但是它与sequencer之间有密切的联系

sequencer与sequence的关系

- 只有在 sequencer的帮助下,sequence产生出的transaction才能最终送给driver

- sequencer只有在sequence出现的情况下才能体现其价值

一个奇怪的比喻

- sequence就像是一个弹夹,里面的子弹是transaction

- 而sequencer是一把枪

- 弹夹只有放入枪中才有意义,枪只有在放入弹夹后才能发挥威力

sequencer与sequence的不同

- sequencer是一个

uvm_component- sequence是一个

uvm_object,与transaction一样具有生命周期,比my_transaction生命周期要长一些,其内的transaction全部 发送完毕后,它的生命周期也就结束了- sequence使用

`uvm_object_utils宏注册到factory中

1.一个sequence的定义

1 | |

定义流程:

- 派生自

uvm_sequence,参数为transaction类型- 定义

body,每一个sequence都有一个body任务,当一个sequence启动之后,会自动执行body中的代码

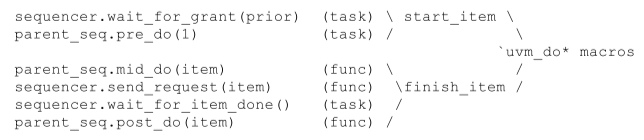

`uvm_do这是UVM中最常用的宏之一,作用:

- 将一个my_transaction的变量m_trans实例化

- 将m_trans随机化

- 将m_trans送给sequencer

如果不用

`uvm_do宏,也可以直接使用start_item与finish_item的方式产生transaction什么时候返回:等待driver的

item_done

2.sequence与sequencer的交互

交互:

- 一个sequence在向sequencer发送transaction前,要先向sequencer发送一个请求

- sequencer把这个请求放在一个仲裁队列中

sequencer的具体工作:

- 检测仲裁队列里是否有某个sequence发送transaction的请求

- 检测driver是否申请transaction

sequencer检测细节:

- 如果仲裁队列里有发送请求,但是driver没有申请trans:一直等待driver

- 如果仲裁队列中没有发送请求,但是driver向sequencer申请新的trans:sqr进入等待seq状态

- 如果仲裁队列中有发送请求,同时driver也在向sequencer申请新的trans:直接同意并移交

3.driver如何向sequencer申请transaction

- 在agent的

connect函数中,把drv中的变量seq_item_port与sqr中的seq_itemu_export连接,代码如下:

1 | |

- 连接好之后,就可以在driver中通过

get_next_item或try_next_item任务向sequencer申请新的trans,代码如下:

使用get_next_item

1 | |

使用try_next_item

1 | |

my_driver代码解析:

- 使用while(1),因为需要不断驱动

- 通过

get_next_item任务得到一个trans,或者try_next_item- 通过

item_done任务告知sequencer为什么会有一个

item_done?

- 一种握手机制

- 可以用来返回response(6.7.1)

- sqr内部保存的同一trans会不断发送,直到调用了

item_done相比于

get_next_item,try_next_item的行为更加接近真实driver的行为:当有数据时,就驱动数据,否则总线将一直处于空闲状 态

4.启动seq(在哪里实例化seq)

启动可以在不同组件的main_phase中(sqr/env),但在实际应用中, 使用最多的还是通过default_sequence的方式启动sequence见2.4.3节

在my_env中启动:

1 | |

在my_sqr中启动

1 | |

流程:

- 声明一个seq变量

- seq工厂机制实例化

- 调用seq的

start方法,入参为sqr指针(如果不指明则不知道匹配的sqr是谁)objection机制与结束仿真

在UVM中,objection一般伴随着sequence,通常只在sequence出现的地方才提起和撤销 objection。如前面所说,sequence是弹夹,当弹夹里面的子弹用光之后,可以结束仿真了

sqr与env中启动的不同:唯一区别是seq.start的参数变为了this

2.4.3 default_sequence的使用

sequence是在my_env的main_phase中手工启动的,作为示例使用这种方式足够了,但在实际应用中, 使用最多的是通过default_sequence的方式启动sequence

1.如何在default_sequence中启动seq

使用default_sequence的方式非常简单,只需要在某个component(如my_env)的build_phase中进行一行设置

在my_env中启动default_sequence的代码:

1 | |

config_db的使用:这是除了在top_tb中通过config_db设置virtual interface后再一次用到config_db参数一:

- 与在top_tb中不同的是,这里set函数的第 一个参数由null变成了this,而第二个代表路径的参数则去除了

uvm_test_top- 事实上,第二个参数是相对于第一个参数的相对路径,由于上述代码是在my_env中,而my_env本身已经是uvm_test_top了,且第一个参数被设置为了this,所以第二个参数中就不需要uvm_test_top

- 在top_tb中设置virtual interface时,由于top_tb不是一个类,无法使用this指针,所以设置set的第一个参数为null,第二个参数使用绝对路径uvm_test_top.xxx

参数二:在第二个路径参数中,出现了

main_phase。这是UVM在设置default_sequence时的要求。由于除了main_phase外,还存在其他任务phase,如configure_phase、reset_phase等,所以必须指定是哪个phase,从而使sequencer知道在哪个phase启动这个sequence参数三、参数四、参数类型:至于set的第三个和第四个参数,以及

uvm_config_db#(uvm_object_wrapper)中为什么是uvm_object_wrapper而不是uvm_sequence或者其他,则纯粹是由于UVM的规定,用户在使用时照做即可为什么这里只用设置一次

config_dbconfig_db通常都是成对出现的,如:在top_tb中通过set设置virtual interface,而在driver或者monitor中通过get函数得到virtual interface

那么在这里是否需要在sequencer中手工写一些get相关的代码呢?答案是否定的。UVM已经做好了这些,读者无需再把时间花在这上面

也可以在top_tb中启动default_sequence:

1 | |

形参设置:

第一个参数和第二个参数应该改变一下

也可以在其他的组件内,如my_agent的build_phase

1 | |

形参设置:

只需要正确地设置set的第二个参数即可(相对于my_env的)

3.default_sequence如何提起和撤销objection

在上一节手动启动sequence前后,分别提起和撤销objection,此时使用default_sequence自动启动,又如何提起和撤销objection呢?

方法:使用继承自uvm_sequence中的变量starting_phase,在sequence中使用starting_phase进行提起和撤销objection

sequence定义代码如下:

1 | |

sequencer在启动default_sequence时会自动做如下相关操作:

1 | |

UVM1.2貌似优化了starting_phase功能,使用方式有所改变

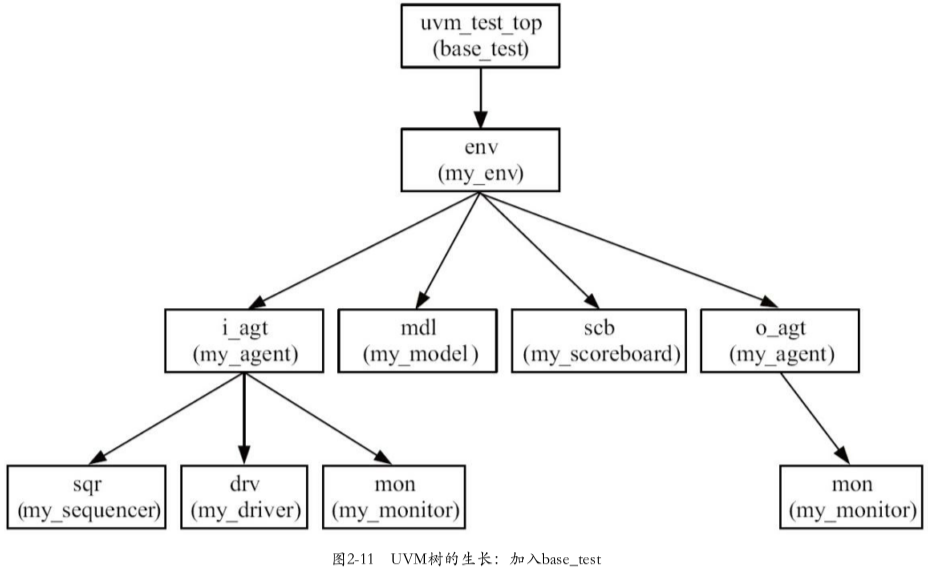

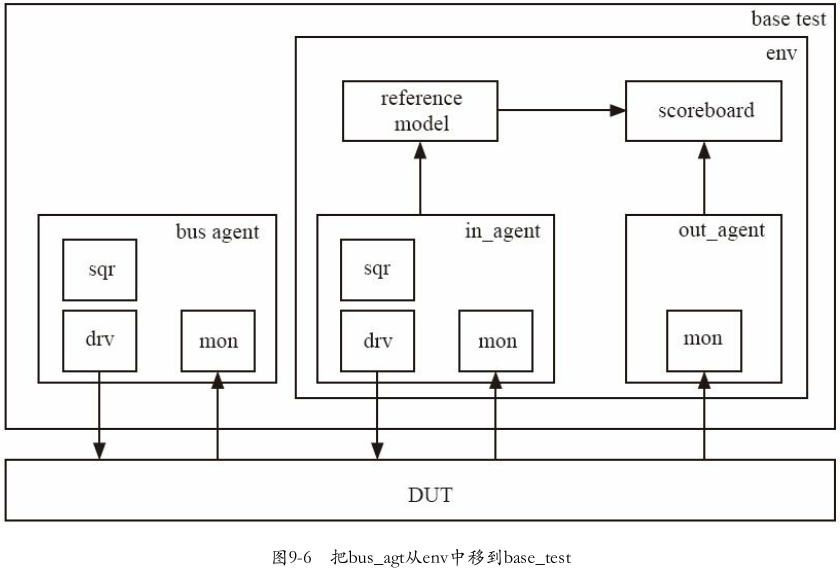

2.5 建造测试用例

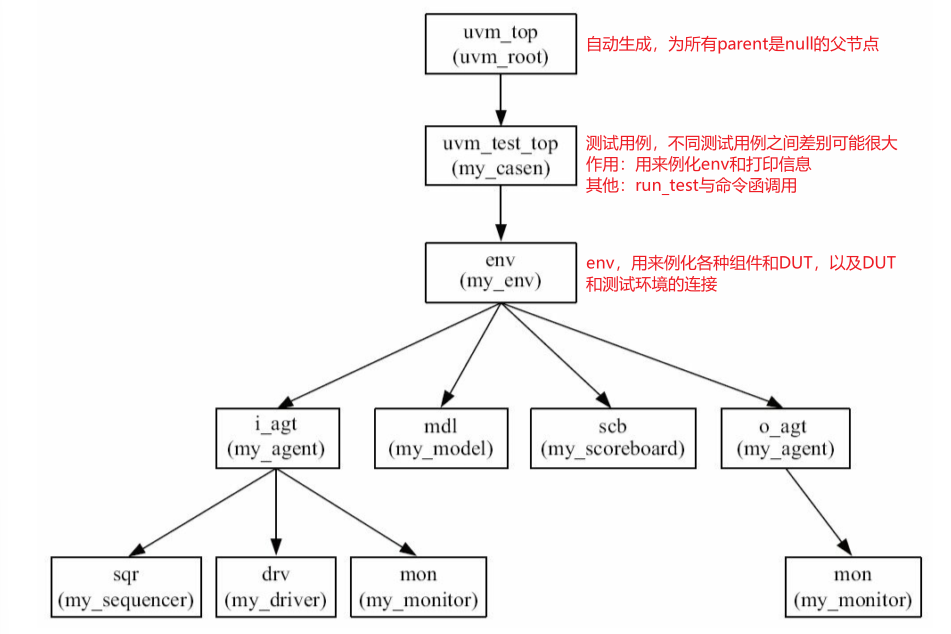

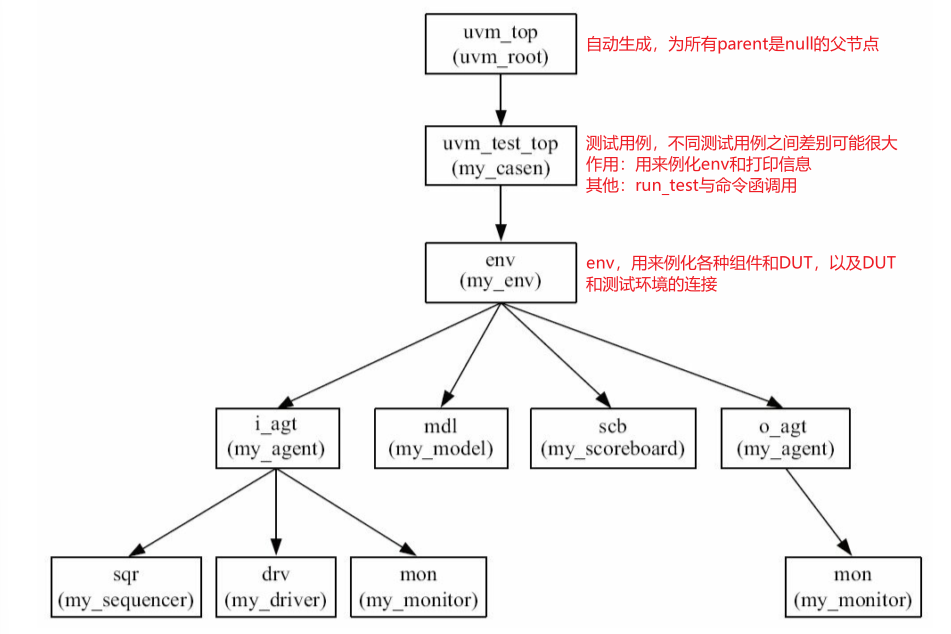

2.5.1 加入base_test

1.前情提要

UVM使用的是一种树形结构,在本书的例子中:

- 最初这棵树的树根是

my_driver - 由于要放置其他component,树根变成 了

my_env - 但是在一个实际应用的UVM验证平台中,my_env并不是树根,通常来说,树根是一个基于

uvm_test派生的类

本节先讲述base_test,真正的测试用例都是基于base_test派生的一个类

1.定义base_test

1 | |

定义流程:

- 派生自

uvm_test- 使用

`uvm_component_utils宏注册到工厂中- 在

build_phase中实例化my_env- 在

build_phase中设置default_sequence,以后都在这里设置default_sequencebase_test一般做什么

- base_test中做的事情在根据不同的验证平台及不同的公司而不同,没有统一的答案

- 此例用到了report_phase,用于根据

UVM_ERROR数量打印不同信息,除此之外一些工具可以根据打印信息判断DUT是否通过了某个测试用例的检查- 设置整个验证平台的超时退出时间

- 通过config_db设置验 证平台中某些参数的值

report_phase

report_phase也是UVM内建的一个phase,它在main_phase结束之后执行

2.加入base_test后的UVM树

3.top_tb模块修改run_test的env为base_test

1 | |

2.5.2 UVM中测试用例的启动

测试用例=测试向量=pattern

1.如何启动两个(多个也行)不同的测试用例

不同测试用例需要修改default_sequence,从而需要多个base_test

方法1:修改run_test参数

- 启动my_case0,需要在top_tb中更改run_test的参数:

1 | |

- 启动my_case1,需要在top_tb中更改run_test的参数:

1 | |

需要不断编译!

当my_case0运行的时候需要修改代码,重新编译后才能运行;当my_case1运行时也需如此,这相当不方便

方法2:使用命令行

UVM提供对不加参数的run_test的支持

- 直接run_test

1 | |

在这种情况下,UVM会利用

UVM_TEST_NAME从命令行中寻找测试用例的名字,创建它的实例并运行

- 命令行运行时需要添加参数

1 | |

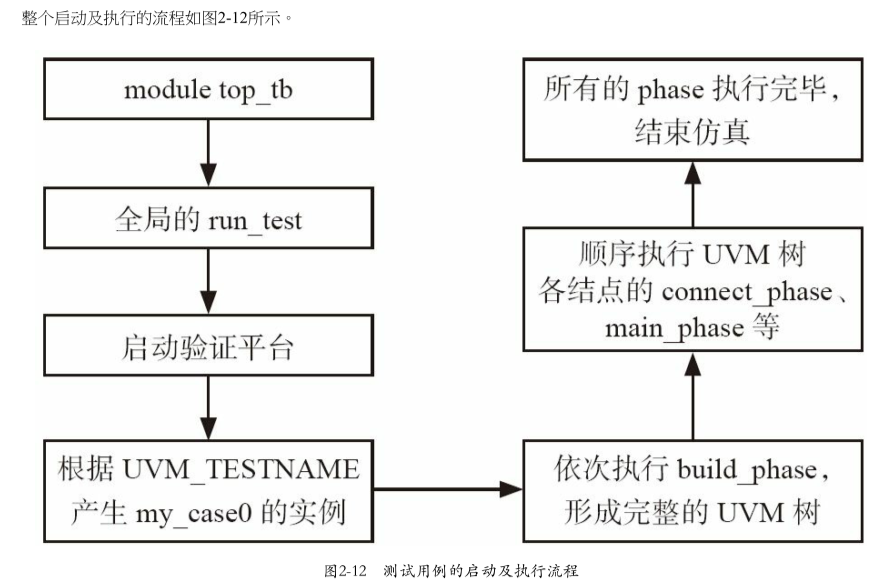

2.测试用例流程启动与验证平台执行流程总结

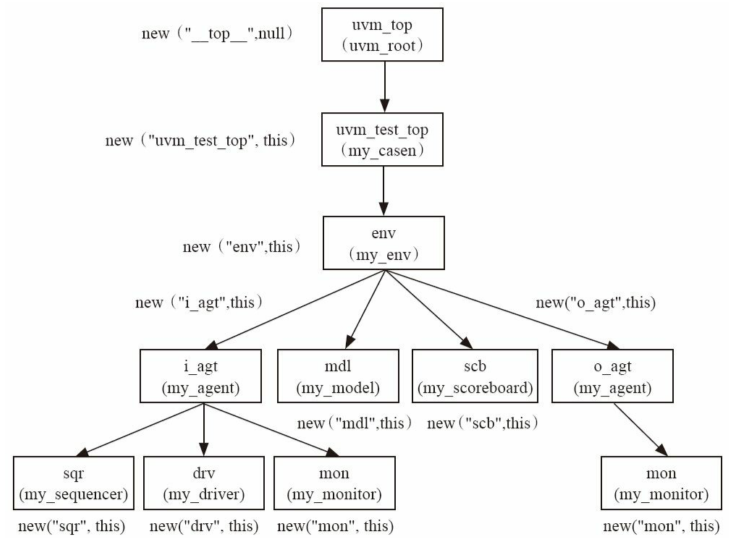

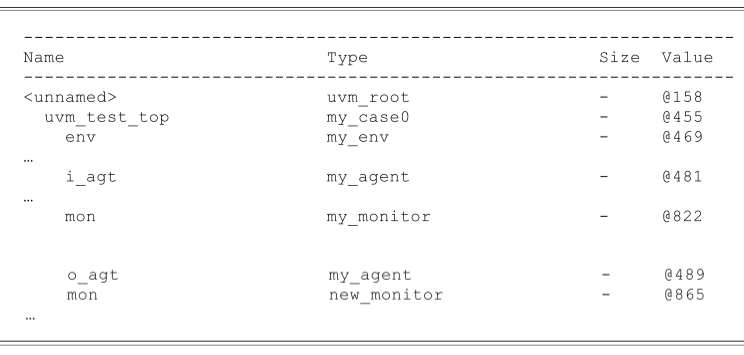

启动后UVM树的结构如图

UVM树与上一节的不同:

把base_test替换为my_casen(说明有好几个测试用例)

3.测试用例定义细节

my_case0与case0_sequence:

1 | |

my_case1与case1_sequence:

1 | |

`uvm_do_with宏是

`uvm_do系列宏中的一个,用于在随机化时提供对某些字段的约束

2022-11-22

第三章UVM基础

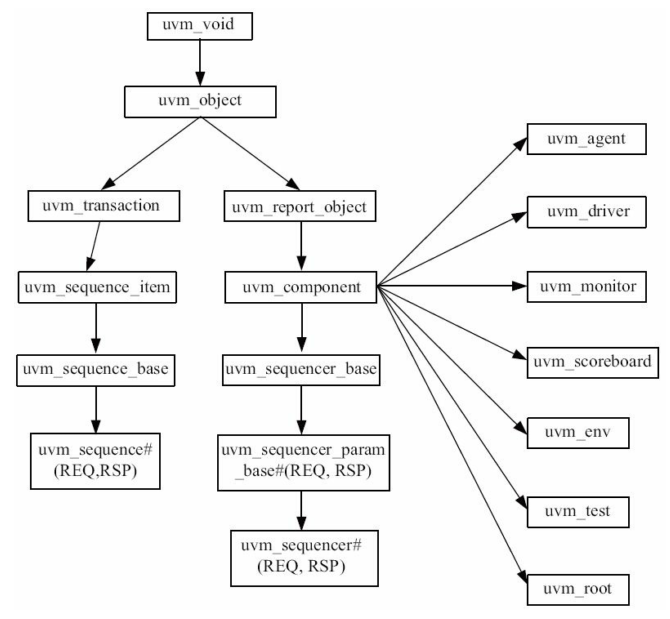

3.1 uvm_object与uvm_component

3.1.1 uvm_component派生自uvm_object

- 要点一:

uvm_object是UVM中最基本的类,几乎所有类都继承自uvm_object - 要点二:

uvm_component派生自uvm_object - 要点三:

uvm_object派生出两个分支 - 要点四:UVM树的所有结点都是

uvm_component(下图左分支不可能出现在UVM树上)

uvm_component独立于uvm_object的两条特性:

- 能在new的时候指定parent参数来形成一种树形的组织结构

- 能phase的自动执行

UVM中常用类的继承关系

3.1.2 常用的uvm_object派生类

uvm_sequence_item:用于派生transaction,transaction就是封装了一定信息的一个类uvm_transaction:UVM中不能从uvm_transaction派生一个transaction,而要从uvm_sequence_item派生uvm_sequence:用于派生所有的sequence,sequence直接与sequencer打交道config:用于规范验证平台的行为方式,- 如规定driver在读取总线时 地址信号要持续几个时钟,片选信号从什么时候开始有效等

- 这里要注意config与config_db的区别。在上一章中已经见识了使用 config_db进行参数配置,这里的config其实指的是把所有的参数放在一个object中,如10.5节所示。然后通过config_db的方式设置给所有需要这些参数的component

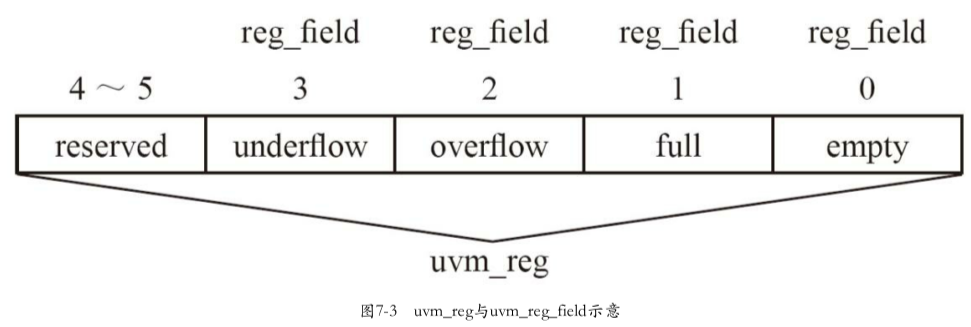

uvm_reg_item、uvm_reg_map、uvm_mem、uvm_reg_field、uvm_reg、uvm_reg_file、uvm_reg_block等与寄存器相关的众多的类,用于register modeluvm_phase:用为控制uvm_component的行为方式,使得uvm_component平滑地在各个不同的 phase之间依次运转- 其他还有很多并不那么重要,这里不再一一列出

3.1.3 常用的uvm_component派生类

合集:

继承关系:

路径图:

3.4总结图

uvm_driver:派生driver

driver的功能主要就是向sequencer索要sequence_item(transaction),并将sequence_item里的信息驱动到DUT的端口上- driver完成了从transaction级别到DUT能够接受的端口级别信息的转换

- 与

uvm_component相比多的成员变量:

uvm_seq_item_pull_port #(REQ, RSP) seq_item_port;uvm_seq_item_pull_port #(REQ, RSP) seq_item_prod_if; // aliasuvm_analysis_port #(RSP) rsp_port;REQ req;RSP rsp;- 在函数/任务上,与

uvm_component相比没有做过多的扩展

uvm_monitor:派生monitor

monitor从DUT的pin上接收数据,并把接收到的数据转换成

transaction级的sequence_item,再把转换后的数据发送给scoreboard,供其比较与driver相反

- 与

uvm_component相比,uvm_monitor几乎没有做任何扩充- 几乎没有做任何扩展

- 理论上来说所有的monitor要从

uvm_monitor派生,但是实际上如果从uvm_component派生,也没有任何问题

uvm_sequencer:派生sequencer

- sequencer的功能就是组织管理

sequence,当driver要求数据时, 它就把sequence生成的sequence_item转发给driver- 与

uvm_component相比,uvm_sequencer做了相当多的扩展,在第六章介绍

uvm_scoreboard:派生scoreboard

- scoreboard的功能就是比较

reference model和monitor分别发送来的数据,根据比较结果判断DUT是否正确工作- 与

uvm_component相比,uvm_scoreboard几乎没有做任何扩充- 几乎没有做任何扩展

- 理论上来说所有的monitor要从

uvm_scoreboard派生,但是实际上如果从uvm_component派生,也没有任何问题reference model:

UVM中并没有针对reference model定义一个类,reference model都是直接派生自

uvm_componentreference model的作用就是模仿DUT

uvm_agent:派生agent

- 只是把driver和monitor封装在一起,根据参数值来决定是只实例化monitor还是要同时实例化driver和monitor

- 主要作用是重构性

- 与

uvm_component相比,uvm_agent的最大改动在引入了一个变量is_active

uvm_env:派生env

- env将验证平台上用到的固定不变的component都封装在一 起

uvm_env几乎没有做任何扩展- 加入寄存器模型,包括reg model与adapt,并进行相应连接,在

uvm_test中添加寄存器模型更常用

uvm_test:所有的测试用例要派生自uvm_test或其派生类,不同的测试用例之间差异很大,所以从uvm_test派生出来的类各不相同

- 任何一个派生出的测试用例中,都要实例化

env,只有这样,当测试用例在运行的时候,才能把数据正常地发给DUT,并正常接收DUT数据- uvm_test_top是一个

run_test("注册的类名")生成的注册类名的实例,实例名固定为uvm_test_topuvm_test几乎没有做任何扩展- 用法

- 例化env

- 控制打印信息

- 控制objection(5.1.7)

- 启动seq(2.5.2)

- 通过config_db设置seq(6.6)

- 加入寄存器模型,包括reg model与adapt,并进行相应连接(7.2.2)

- reg_predictor

base_test:

- print_topology(8.2.4 factory机制的调试)

uvm_root

uvm_top是一个全局变量,它是uvm_root的一个实例(而且也是唯一的一个实例,设计模式中鼎鼎)- UVM中所有parent为null的component的父节点

uvm_top的名字是__top__,但是在显示路径的时候,并不会显示出这 个名字,而只显示从uvm_test_top开始的路径- UVM默认生成,你不用管

- 作用:为了确保整个验证平台中只有一棵树,所有节点都是uvm_top子节点

testbench模块

import uvm_pkg::*;和`include "uvm_macros.svh"和`include “自定义的各种uvm组件.sv”- 运行

run_test();,有关run_test();的内容参考2.5.2- 产生其他信号(clk,rstn)

- 用于例化DUT,virtual interface

- 将DUT与virtual interface直接连接

- 通过

config_db将virtual interface与uvm_test_top.env?中各个组件进行连接

其他扩展:

在哪控制objection?

- scoreboard或sequence中启动,详见5.2.3

- 存在virtual sequence在最顶层virtual sequence中启动,详见6.5.4

全局变量

factory

- 来源:8.2.2

- 作用:用于uvm_component外调用重载函数

3.1.4 uvm_object相关宏

uvm_object相关的factory宏有如下几个:

`uvm_object_utils:注册object到factory中`uvm_object_param_utils:注册参数化的object到factory中`uvm_object_utils_begin:对成员变量使用field_automation机制`uvm_object_param_utils_begin:参数化的对成员变量使用field_automation机制`uvm_object_utils_end:结束注册,与uvm_object_*_begin成对出现

3.1.5 uvm_component相关宏

uvm_component相关的factory宏有如下几个:

`uvm_component_utils:注册component到factory中`uvm_component_param_utils:注册参数化的component到factory中`uvm_component_utils_begin:对成员变量使用field_automation机制`uvm_component_param_utils_begin:参数化的对成员变量使用field_automation机制`uvm_object_utils_end:结束注册,与uvm_object_*_begin成对出现

在类似于my_transaction这种类中使用field_automation机制可以让人理解,可是在component中使用field_automation机制有必要吗?

uvm_component派生自uvm_object,可以直接使用object的compare、print等方法- 可以自动地使用config_db来得到某些变量的值。具体的可以参考3.5.3节的介绍

3.1.6 copy与clone,comp的一些限制

由于uvm_component是作为UVM树的结点存在的,使它失去了uvm_object的某些特征

1.无法使用clone方法

uvm_object的clone方法使用方式:

1 | |

上述

clone函数无法用于uvm_component中,因为一旦使用后,新clone出来的类,其parent参数无法指定

2.可以使用copy方法

clone=new+copy:

- 在使用copy前,目标实例必须已经使用new函数分配好了内存空间

- 使用clone函数时,目标实例可以只是一个空指针

uvm_component无法使用clone函数,但是可以使用copy函数。因为在调用copy之前,目标实例已经完成了实例化,其 parent参数已经指定了

3.禁止子节点同名

位于同一个父结点下的不同的component,在实例化时不能使用相同的名字

如下的方式中都使用名字a1是会出错的:

1 | |

3.1.7 uvm_component与uvm_object的二元结构

这本书在讲尬的…

3.2 UVM的树形结构

3.2.1 uvm_component中的parent参数

uvm_component在new的时候,需要指定一个类型为uvm_component的变量parent

1 | |

一般使用时,parent通常是this

为什么要有parent这个参数?直接

new(string name)不好吗

- 书中写了一堆废话。。

- 最主要是要解决如何找到所有UVM节点的问题,加入了parent句柄,在new之后分别在对象与嵌套对象中维护一个m_children数组,从而能够知道一共几个

- 我的补充:讲道理,这应该是语言的基本特性。。。讲的这么复杂多少有点。。。

3.2.2 UVM树真正的根:uvm_top

UVM中真正的树根是一个称为uvm_top的东西,完整的UVM树如下:

uvm_top哪来的?

uvm_top是一个全局变量,它是uvm_root的一个实例(而且也是唯一的一个实例,设计模式中鼎鼎)- UVM中所有parent为null的component的父节点

- UVM默认生成,你不用管

- 作用:为了确保整个验证平台中只有一棵树,所有节点都是uvm_top子节点

总结一下:

补充:

UVM顶层:uvm_test_top是一个自动生成的

uvm_root的实例,所有parent为null的组件的父节点(即上级),实例名为uvm_top测试用例:uvm_test_top是一个

run_test("注册的类名")生成的注册类名的实例,实例名固定为uvm_test_top用法

- 例化env

- 控制打印信息

- 控制objection(5.1.7)

- 启动seq(2.5.2)

如何得到uvm_top句柄?

1 | |

3.2.3 层次结构相关函数

extern virtual function uvm_component get_parent();函数,用于得到当前实例的parentextern function uvm_component get_child(string name);函数,用于得到childextern function void get_children(ref uvm_component children[$]);函数,用于得到所有childextern function int get_first_child(ref string name);:函数,得到第一个child的名字extern function int get_next_child(ref string name);:函数,得到下一个child的名字extern function int get_num_children();函数,返回当前component所拥有的child的数量

遍历所有child的方法1(使用get_children)

1 | |

遍历所有child的方法2(使用get_child、get_first_child、get_next_child)

1 | |

3.3 field automation机制

一般用于类的内部成员变量定义

3.3.1 field automation机制相关宏

uvm_field_*系列宏:

1 | |

枚举类型示例(它有三个参数,所以单独拿出来说下):

2

3

4

5typedef enum {TB_TRUE, TB_FALSE} tb_bool_e;

…

tb_bool_e tb_flag;

…

`uvm_field_enum(tb_bool_e, tb_flag, UVM_ALL_ON)基本和数组/队列的不同

- 多了

*_real和*_event*_enum多了一个参数联合数组是SystemVerilog中定义的一种非常有用的数据类型,在验证平台中经常使用

在与联合数组有关的uvm_field系列宏中, 出现的第一个类型是存储数据类型,第二个类型是索引类型,如

uvm_field_aa_int_string中的_int_string用于声明那些存储的数据是int,而其索引是string类型的联合数组

3.3.2 field automation机制常用功能

field automation功能非常强大

extern virtual function uvm_object clone();完全复制实例,不用提前实例化,参考3.1.6extern function void copy(uvm_object rhs);复制实例,把A实例复制到B实例中,使用B.copy(A)。使用此函数前,B实例必须已经使用new函数分配了内存空间extern function bit compare(uvm_object rhs, uvm_comparer comparer=null);比较实例,比较A与B使用A.compare(B),一致返回1,否则0extern function int pack_bytes(ref byte unsigned bytestream[], input uvm_packer packer=null);用于将所有字段打包为byte流,参考第二章extern function int unpack_bytes(ref byte unsigned bytestream[], input uvm_packer packer=null);用于把byte流恢复到某个类的实例中extern function int pack(ref bit bitstream[], input uvm_packer packer=null);与pack_bytes类似extern function int unpack(ref bit bitstream[], input uvm_packer packer=null);与unpack_bytes类似extern function int pack_ints(ref int unsigned intstream[], input uvm_packer packer=null);用于恢复一个int流print用于打印所有字段

除此之外,field automation提供自动得到使用config_db::set设置的参数的功能,这点请参照3.5.3节

3.3.3 field automation机制中的标志位(flag)

flag用于field automation定义变量的功能

1 | |

UVM_ALL_ON的值是'b000000101010101,表示打开该变量的copy、compare、print、record、pack功能UVM_ALL_ON|UVM_NOPACK的结果是'b000001101010101,这样UVM在执行pack操作时,首先检查bit9,发现其为1,直接忽略bit8所代表的UVM_PACK

3.3.4 field automation中宏与if的结合

这本书中又讲了一个让人摸不着头脑的例子

简单来说,就是field_automation可以这么用:

1 | |

使用if来决定field_automation:

1 | |

3.4 UVM中打印信息的控制

一般在测试用例中设置,测试用例主要做打印信息的控制与仿真结束的控制(断点/rasie/error等待)以及default_sequence,env主要做组件例化和uvm_port连接

3.4.1 打印信息冗余度(uvm_verbosity)

UVM通过冗余度级别的设置提高了仿真日志的可读性

- 在打印信息之前,UVM会比较要显示信息的冗余度级别与默认的冗余度阈值,如果小于等于阈值显示,否不显示

- 默认的冗余度阈值是

UVM_MEDIUM,所有低于等于UVM_MEDIUM(如UVM_LOW)的信息都会被打印出来

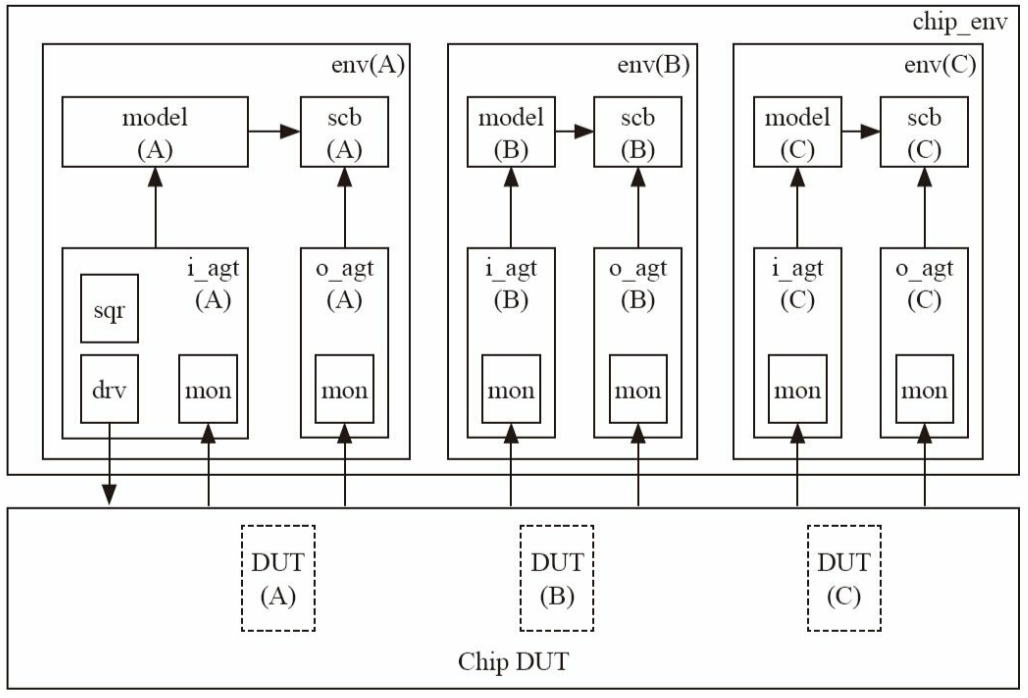

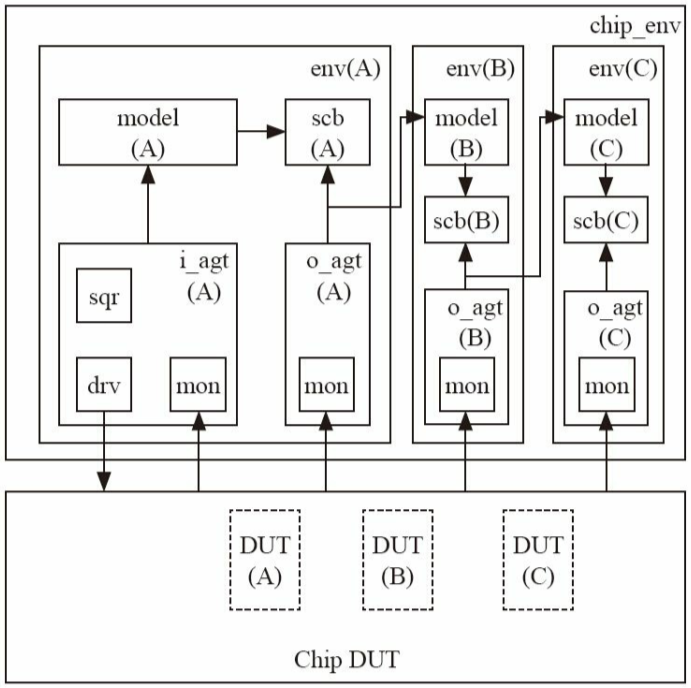

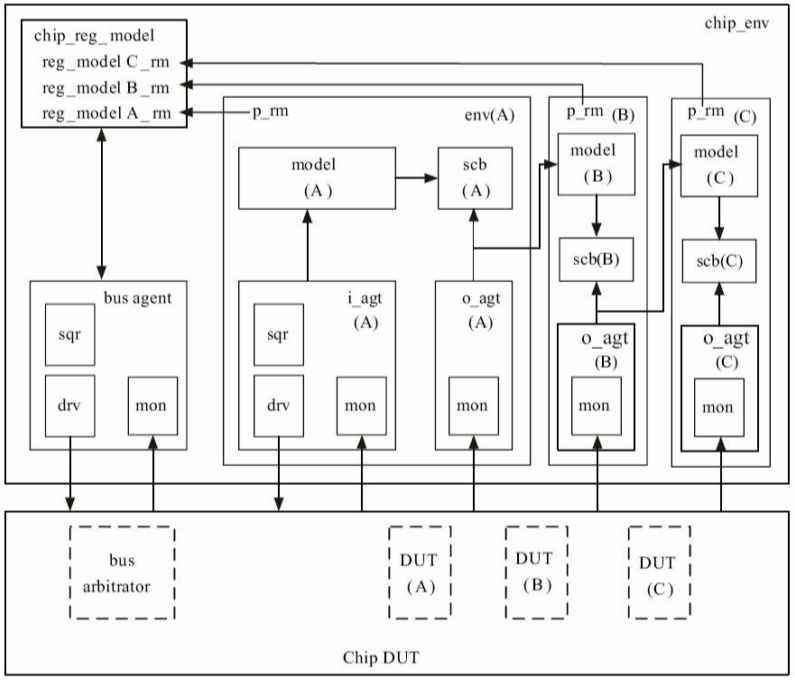

对不同的component设置不同的冗余度阈值非常有用。在芯片级别验证时,重用了不同模块(block)的env。由于个人习惯的不同,每个人对信息冗余度的容忍度也不同,有些人把所有信息设置为UVM_MEDIUM,也有另外一些人喜欢把所有的信息都设置为UVM_HIGH。通过设置不同env的冗余度级别,可以更好地控制整个芯片验证环境输出信息的质量。

1.以组件为单位的函数

get_report_verbosity_level得到某个component的冗余度阈值:

2

3virtual function void connect_phase(uvm_phase phase);

$display("env.i_agt.drv's verbosity level is %0d", env.i_agt.drv.get_report_verbosity_level ());

endfunction返回值:

uvm_verbosity

2

3

4

5

6

7

8typedef enum {

UVM_NONE = 0,

UVM_LOW = 100,

UVM_MEDIUM = 200,

UVM_HIGH = 300,

UVM_FULL = 400,

UVM_DEBUG = 500

} uvm_verbosity;

set_report_verbosity_level设置某个特定component的默认冗余度阈值,使用代码如下

2

3

4virtual function void connect_phase(uvm_phase phase);

env.i_agt.drv.set_report_verbosity_level(UVM_HIGH);

...

endfunction

set_report_verbosity_level调用phase:

- 需要牵扯到层次引用,所以需要在

connect_phase及以后的phase才能调用这个函数- 如果不牵扯到任何层次引用,可以在

connect_phase之前调用

set_report_verbosity_level只对某个特定的component起作用

set_report_verbosity_level_hier递归设置某component及其子节点的默认冗余度阈值,使用代码如下:

env.i_agt.set_report_verbosity_level_hier(UVM_HIGH);

2.组件内以ID为单位的函数

set_report_id_verbosity函数来区分不同的ID的冗余度阈值,使用示例:

2

3

4

5

6//某组件中

`uvm_info("ID1", "ID1 INFO", UVM_HIGH)

`uvm_info("ID2", "ID2 INFO", UVM_HIGH)

//env中

env.i_agt.drv.set_report_id_verbosity("ID1", UVM_HIGH);

//经过上述设置后“ID1INFO”会显示,但是“ID2INFO”不会显示

set_report_id_verbosity_hier递归设置某component及其子节点的某ID的默认冗余度阈值,使用代码如下:

env.i_agt.set_report_id_verbosity_hier("ID1", UVM_HIGH);

3.在命令行中设置

UVM支持在命令行中设置冗余度阈值:

2

3><sim command> +UVM_VERBOSITY=UVM_HIGH

>或者:

><sim command> +UVM_VERBOSITY=HIGH

- 这两个命令行参数是等价的,即可以把冗余度级别的前缀

UVM_省略- 上述的命令行参数会把整个验证平台的冗余度阈值设置为UVM_HIGH。相当于是在base_test中调用

set_report_verbosity_level_hier函数,把base_test及以下所有component的冗余度级别设置为UVM_HIGH

3.4.2 重载打印信息的严重性

UVM默认有四种信息严重性:UVM_INFO、UVM_WARNING、UVM_ERROR、 UVM_FATAL

1.重载打印信息的严重性

重载是深入到UVM骨子里的一个特性

这四种严重性可以互相重载

set_report_severity_override重载严重性

2

3

4//如果要把driver中所有的`UVM_WARNING显示为`UVM_ERROR,可以使用如下的函数

virtual function void connect_phase(uvm_phase phase);

env.i_agt.drv.set_report_severity_override(UVM_WARNING, UVM_ERROR); //env.i_agt.drv.set_report_severity_id_override(UVM_WARNING, "my_driver", UVM_ERROR);

endfunction不提供递归重载,与设置冗余度不同

严重性重载用的较少,一般的只会对某个component内使用,不会递归的使用

针对某个component的特定ID重载严重性:

env.i_agt.drv.set_report_severity_id_override(UVM_WARNING, "my_driver", UVM_ERROR);命令行中实现重载严重性:

2

3<sim command> +uvm_set_severity=<comp>,<id>,<current severity>,<new severity>

# 如果要把driver中所有的`UVM_WARNING显示为`UVM_ERROR,可以使用如下的函数(替代set_report_severity_override中的示例)

><sim command> +uvm_set_severity="uvm_test_top.env.i_agt.drv,my_driver,UVM_WARNING,UVM_ERROR"若要设置所有的ID,可以在id处使用

_ALL_:

<sim command> +uvm_set_severity="uvm_test_top.env.i_agt.drv,_ALL_,UVM_WARNING,UVM_ERROR"

3.4.3 严重性与结束仿真

UVM_FATAL出现时,表示出现了致命错误,仿真会马上停止

在end_of_elaboration_phase及其前的phase中,如果出现了一个或多个UVM_ERROR,那么UVM就认为出现了致命错误,会调用uvm_fatal结束仿真(5.1.6节提到),其他情况UVM_ERROR默认不会结束(最后一句不会结束我瞎猜的)

1.设置UVM_ERROR退出阈值

UVM_ERROR达到一定数量时也可以结束仿真

- 这个功能非常有用。对于某个测试用例,如果出现了大量的

UVM_ERROR,根据这些错误已经可以确定bug所在了,再继续仿真下去意义已经不大,此时就可以结束仿真,而不必等到所有的objection被撤销

set_report_max_quit_count设置UVM_ERROR退出阈值,使用函数示例

2

3

4

5function void base_test::build_phase(uvm_phase phase);

super.build_phase(phase);

env = my_env::type_id::create("env", this);

set_report_max_quit_count(5);

endfunction

get_max_quit_count查询当前的UVM_ERROR退出阈值,如果返回值为0则表示无论出现多少个UVM_ERROR都不会退出仿真在命令行中设置退出阈值:

+UVM_MAX_QUIT_COUNT=6,NO第一个参数6表示退出阈值,而第二个参数NO表示此值是不可以被后面的设置语句重载,其值还可以是YES

2.设置其他严重性退出

set_report_severity_action把其他严重性加入计数目标,下面的代码把UVM_WARNING加入计数目标:

2

3

4

5virtual function void connect_phase(uvm_phase phase);

…

set_report_max_quit_count(5);

env.i_agt.drv.set_report_severity_action(UVM_WARNING, UVM_DISPLAY|UVM_COUNT);

endfunction

set_report_severity_action:递归设置

env.i_agt.set_report_severity_action_hier(UVM_WARNING, UVM_DISPLAY| UVM_COUNT);

3.针对ID计数退出

除了针对严重性进行计数外,还可以对某个特定的ID进行计数

set_report_id_action:下面代码把ID为my_drv的所有信息加入计数退出

env.i_agt.drv.set_report_id_action("my_drv", UVM_DISPLAY| UVM_COUNT)

set_report_id_action_hier递归设置

env.i_agt.set_report_id_action_hier("my_drv", UVM_DISPLAY| UVM_COUNT);

4.联合ID与严重性计数退出

除了分别对严重性和ID进行设置外,UVM还支持把它们联合起来进行设置

2>set_report_severity_id_action

env.i_agt.drv.set_report_severity_id_action(UVM_WARNING, "my_driver", UVM_DISPLAY| UVM_COUNT);

set_report_severity_id_action_hier:递归形式

env.i_agt.set_report_severity_id_action_hier(UVM_WARNING, "my_driver", UVM_DISPLAY| UVM_COUNT);命令行中设置:

2

3

4

5<sim command> +uvm_set_action=<comp>,<id>,<severity>,<action>

#如

<sim command> +uvm_set_action="uvm_test_top.env.i_agt.drv,my_driver,UVM_NG,UVM_DISPLAY|UVM_COUNT"

#针对所有ID时,用_ALL_代替ID

<sim command> +uvm_set_action="uvm_test_top.env.i_agt.drv,_ALL_,UVM_WARNING,UVM_DISPLAY|UVM_COUNT"

3.4.5 UVM的断点功能

断点功能需要从仿真器的角度进行设置,不同仿真器的设置方式不同。为了消除这些设置方式的不同,UVM支持内建的断点功能,当执行到断点时,自动停止仿真,进入交互模式

1.具体实现

- 把3.4.4节介绍的函数中

UVM_COUNT替换为UVM_STOP就可以实现断点功能,函数目录:

1 | |

- 命令行中也可以设置断点:

1 | |

2.使用示例

使用set_report_severity_action函数,当env.i_agt.drv中出现UVM_WARNING时,立即停止仿真,进入交互模式

1 | |

3.4.6 将输出信息导入文件中

各个仿真器提供将显示在标准输出的信息同时输出到一个日志文件中的功能,但是这个日志文件混杂了所有的UVM_INFO、UVM_WARNING、UVM_ERROR及UVM_FATAL

UVM提供将特定信息输出到特定日志文件的功能

1 | |

代码总结

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28//严重性

env.i_agt.drv.set_report_severity_file(UVM_INFO, info_log);

env.i_agt.drv.set_report_severity_file(UVM_WARNING, warning_log);

env.i_agt.drv.set_report_severity_file(UVM_ERROR, error_log);

env.i_agt.drv.set_report_severity_file(UVM_FATAL, fatal_log);

env.i_agt.drv.set_report_severity_action(UVM_INFO, UVM_DISPLAY | UVM_LOG);

env.i_agt.drv.set_report_severity_action(UVM_WARNING, UVM_DISPLAY | UVM_LOG);

env.i_agt.drv.set_report_severity_action(UVM_ERROR, UVM_DISPLAY | UVM_COUNT | UVM_LOG);

env.i_agt.drv.set_report_severity_action(UVM_FATAL, UVM_DISPLAY | UVM_EXIT | UVM_LOG);

//严重性递归

env.i_agt.set_report_severity_file_hier(UVM_INFO, info_log);

env.i_agt.set_report_severity_file_hier(UVM_WARNING, warning_log); env.i_agt.set_report_severity_file_hier(UVM_ERROR, error_log); env.i_agt.set_report_severity_file_hier(UVM_FATAL, fatal_log);

env.i_agt.set_report_severity_action_hier(UVM_INFO, UVM_DISPLAY| UVM_LOG); env.i_agt.set_report_severity_action_hier(UVM_WARNING, UVM_DISPLAY| UVM_LOG); env.i_agt.set_report_severity_action_hier(UVM_ERROR, UVM_DISPLAY| UVM_COUNT |UVM_LOG);

env.i_agt.set_report_severity_action_hier(UVM_FATAL, UVM_DISPLAY| UVM_EXIT | UVM_LOG);

//id

env.i_agt.set_report_id_file_hier("my_driver", driver_log); env.i_agt.set_report_id_file_hier("my_drv", drv_log); env.i_agt.set_report_id_action_hier("my_driver", UVM_DISPLAY| UVM_LOG);

env.i_agt.set_report_id_action_hier("my_drv", UVM_DISPLAY| UVM_LOG);

//id递归

env.i_agt.set_report_severity_id_file_hier(UVM_WARNING, "my_driver", driver_log); env.i_agt.set_report_severity_id_file_hier(UVM_INFO, "my_drv", drv_log); env.i_agt.set_report_id_action_hier("my_driver", UVM_DISPLAY| UVM_LOG);

env.i_agt.set_report_id_action_hier("my_drv", UVM_DISPLAY| UVM_LOG);

//严重性与id组合

env.i_agt.drv.set_report_severity_id_file(UVM_WARNING, "my_driver", driver_log);

env.i_agt.drv.set_report_severity_id_file(UVM_INFO, "my_drv", drv_log);

env.i_agt.drv.set_report_id_action("my_driver", UVM_DISPLAY| UVM_LOG);

env.i_agt.drv.set_report_id_action("my_drv", UVM_DISPLAY| UVM_LOG);

//严重性与id组合递归

env.i_agt.set_report_severity_id_file_hier(UVM_WARNING, "my_driver", driver_log); env.i_agt.set_report_severity_id_file_hier(UVM_INFO, "my_drv", drv_log); env.i_agt.set_report_id_action_hier("my_driver", UVM_DISPLAY| UVM_LOG);

env.i_agt.set_report_id_action_hier("my_drv", UVM_DISPLAY| UVM_LOG);

3.4.7 控制打印行为

UVM中的打印信息的行为uvm_action_type:

1 | |

多行为可叠加(类似field automation中的标志位):

1 | |

默认严重级对应的行为:

1 | |

3.5 config_db机制

一般在build_phase中使用

3.5.1 UVM中的路径

- 使用

get_full_name()函数得到component路径 - 使用

comp::get()得到某componet的句柄

1.路径分析

UVM中的路径图(new函数而不是factory中的create是为了方便)

1 | |

打印值为

uvm_test_top.env.i_agt.drv

uvm_top:

uvm_top的名字是__top__,但是在显示路径的时候,并不会显示出这 个名字,而只显示从uvm_test_top开始的路径

uvm_test_top:

uvm_test_top实例化时的名字是uvm_test_top,这个名字是由UVM在run_test时自动指定的路径与层次:

- 路径是

create或new传递的名字组成- 层次结构是由组件句柄的引用

尽量保持保持组件句柄与实例时传递名称统一,否则:

2

3如果drv在new时指定的名字不是drv,而是driver,即:

drv = my_driver::type_id::create("driver");

那么drv在my_casen看来,层次结构依然是env.i_agt.drv,但其路径变为了env.i_agt.driver

3.5.2 set与get函数的参数

config_db用于在UVM验证平台间传递参数,通常成对出现(但是在某些情况下可以只有set而没有get语句,即省略get语句3.5.2节):

- get收信

- set寄信

1.在某个casen的build_phase中可以使用如下方式寄信:

1 | |

第一个和第二个参数联合起来组成目标路径,与此路径符合的目标才能收信

第一个参数

cntxt必须是一个uvm_component实例的指针set第一个参数若为null,UVM会自动把第一个参数替换为代码

uvm_root::get(),即uvm_top第一个参数应该尽量使用

this。在无法得到this指针的情况下(如在top_tb中),使用null或者uvm_root::get()

第二个参数

inst_name是相对此实例的路径第三个参数

field_name表示一个记号,用以说明这个值是传给目标中的哪个成员的第四个参数是要设置的值

2.在driver中的build_phase使用如下方式收信:

1 | |

- 第一个参数和第二个参数联合起来组成路径

第一个参数

cntxt也必须是一个uvm_component实例的指针cntxt- get第一个参数若为null,UVM会自动把第一个参数替换为代码

uvm_root::get(),即uvm_top - 第一个参数应该尽量使用

this。在无法得到this指针的情况下(如在top_tb中,或者seq中),使用null或者uvm_root::get()

- get第一个参数若为null,UVM会自动把第一个参数替换为代码

第二个参数

inst_name是相对此实例的路径(使用组件cntxt作为起始搜索点 ,获取inst_name中field_name的值,如果cntxt是配置对象适用的实例,则inst_name可以是空字符串)- 第三个参数

field_name就是set函数中的第三个参数,这两个参数必须严格匹配 - 第四个参数则是要设置的变量

3.默认句柄:

- set/get第一个参数为null,UVM会自动把第一个参数替换为代码

uvm_root::get(),即uvm_top,以下两种写法是完全等价的:

1 | |

4.set参数也可以这么写

既然set函数的第一个和第二个参数联合起来组成路径,那么在castn的build_phase中可以通过如下的方式设置env.i_agt.drv中pre_num_max的值:

1 | |

- 第一个参数把

this替换为了this.env - 第二个参数是

my_driver相对于env的路径

5.get参数也可以这么写

get函数的参数

1 | |

这些写法都是可以的,只是它们相对于本节最开始的写法没有任何优势。所以还是提倡使用最开始的写法。但是这种写法也 并不是一无是处,在3.5.6节中会介绍它们的一种应用

6.常用写法

- get中用于接收此comp的:参数1:

null或uvm_root::get(),参数2:get_full_name()或从uvm_test_top开始的绝对路径字符串 - set中一般用

this:参数1:this,参数2:子节点的相对路径字符串

3.5.3 省略get语句

set与get函数一般都是成对出现,但是在某些情况下,是可以只有set而没有get语句,即省略get语句

某些情况:指的给在component中使用field automation机制注册的变量传值时,收信方在build_phase中调用super.build_phase()后就可以省略config_db::get直接读取了

示例如下:

1 | |

原理:

这里的关键是build_phase中的super.build_phase语句,当执行到driver的super.build_phase时,会自动执行get语句

这种做法的前提是:

- 组件(这里是my_driver)必须使用

`uvm_component_utils宏注册 - 收信参数(这里是pre_num)必须使用

`uvm_field_int宏注册 - 在调用set函数的时候,set函数的第三个参数必须与要get函数中变量的名字相一致(这里是pre_num)

- 所以上节中,虽然说这两个参数可以不一致,但是最好的情况下还是一致

3.5.4-3.5.5 多重设置

在前面的所有例子中,都是设置一次(config_db#(T)::set),获取一次config_db#(T)::get。但是假如设置多次,而只获取一次,最终会得到哪个值呢?

- 跨层次->组件判断

- 同层次->时间判断(最后优先级最高)

1.跨层次的多重设置

UVM规定层次越高,那么它的优先级越高。这里的层次指的是在UVM树中的位置,越靠近根结点uvm_top,则认为其层次越高。

如何判断set是哪一层的?

- 通过第一个参数:

uvm_config_db#(int)::set(this, "env.i_agt.drv", "pre_num", 100); - 如果第一个参数不是

this而是uvm_root::get(),则都是从uvm_top树根设置,需要进行同层次时间判断 - 因此,无论如何,在调用

set函数时其第一个参数应该尽量使用this。在无法得到this指针的情况下(如在top_tb中),使用null或者uvm_root::get()

2.同层次的多重设置

处于同一层次时,是时间优先,例如下面两个语句同时出现在测试用例的build_phase中时,driver最终获取到的值将会是109:

1 | |

像上面的这种用法看起来完全是胡闹,没有任何意义

3.5.6 非直线与直线的设置与获取

直线设置:在被设置的树干的某个节点组件上设置

非直线设置:在其他节点组件设置

直线获取:在被设置的节点组件上获取

非直线获取:从别的被设置的节点组件那里获取

举例:

在图3-4所示的UVM树中,driver的路径为

uvm_test_top.env.i_agt.drv

- 在

uvm_test_top,env或者i_agt中,对driver中的某些变量通过config_db机制进行设置,称为直线设置- 但是若在其他

component,如scoreboard中,对driver的某些变量使用config_db机制进行设置,称为非直线设置

- 在

my_driver中使用config_db::get获得其他任意component设置给my_driver的参数,称为直线的获取- 假如要在其他的

component,如在reference model中获取其他component设置给my_driver的参数的值,称为非直线的获取

非直线设置的危险:

在UVM树中,build_phase是自上而下执行的,UVM并没有明文指出同一级别的build_phase的执行顺序。所以当my_driver在获取参数值时,my_scoreboard的build_phase可能已经执行了,也可能没有执行,所以,这种非直线的设置,会有一定的风险,应该避免这种情况的出现

非直线获取的便捷(一次设置,多个获取):

非直线的获取可以在某些情况下避免config::set的冗余。上面的例子在reference model中获取driver的pre_num的值,如果不这样做,而采用直线获取的方式,那么需要在测试用例中通过config_db::set分别给reference model和driver设置pre_num的值。 同样的参数值设置出现在不同的两条语句中,这大大增加了出错的可能性。因此,非直线的获取可以在验证平台中多个组件(UVM树结点)需要使用同一个参数时,减少config_db::set冗余

3.5.7 config_db机制对通配符的支持(使用星号)

在config_db::set操作时,其第二个参数都提供了完整的路径,但实际上也可以不提供完整的路径而使用通配符*代替

1.举例说明

2.5.2节的top_tb.sv中,使用完整路径设置virtual interface的代码可以写成这样:

1 | |

3.5.8 检查字符串路径(检查config_db参数二)

1 | |

config_db机制一个致命缺点是,其set函数的第二个参数是字符串,如果字符串写错,那么根本就不能正确地设置参数值,而且SystemVerilog的仿真器也不会给出任何参数错误提示

1.解决方法

UVM提供了一个函数check_config_usage:

- 它可以显示出截止到此函数调用时有哪些参数是被设置过但是却没有被获取过

- 由于config_db的set及get语句一般都用于build_phase阶段,所以此函数一般在connect_phase被调用

使用示例

1 | |

default sequence也会被检查出来:是因为default sequence是设置给main_phase的,它在main_phase的时候被获 取,而main_phase是在connect_phase之后执行的

3.5.9 set_config与get_config

UVM1.2发布,set_config与get_config被从UVM标准中移除,成为过时的用法

1.介绍

1 | |

config_db比set/get_config强大的地方在于,它设置的参数类型并不局限于以上三种。常见的枚举类型、virtual interface、bit类 型、队列等都可以成为config_db设置的数据类型

2.使用示例

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20//文件:src/ch3/section3.5/3.5.9/my_case0.sv

function void my_case0::build_phase(uvm_phase phase);

super.build_phase(phase);

uvm_config_db#(uvm_object_wrapper)::set(this,

"env.i_agt.sqr.main_phase",

"default_sequence",

case0_sequence::type_id::get());

set_config_int("env.i_agt.drv", "pre_num", 999);

set_config_int("env.mdl", "rm_value", 10);

endfunction

//文件: src/ch3/section3.5/3.5.9/my_model.sv

>function void my_model::build_phase(uvm_phase phase);

int rm_value;

super.build_phase(phase);

port = new("port", this);

ap = new("ap", this);

void'(get_config_int("rm_value", rm_value));

`uvm_info("my_model", $sformatf("get the rm_value %0d", rm_value), UVM_LOW)

endfunction命令行使用:

UVM提供命令行参数来对它们进行设置

2<sim command> +uvm_set_config_int=<comp>,<field>,<value>

<sim command> +uvm_set_config_string=<comp>,<field>,<value>在设置int型参数时,可以在其前加上如下的前缀:’b、’o、’d、’h,分别表示二进制、八进制、十进制和十六进制的数据。如果不加任何前缀,则默认为十进制

3.5.10 config_db的调试

chech_config_usage(void):显示出截止到函数调用时,系统中有哪些参数被设置过但是没有被读取过print_config(int num):参数为1表示递归的查询,若为0则只显示当前component的信息,用于找出哪些被设置过的信息对于它们是可见的(不会列出default sequence的相关设置)UVM_CONFIG_DB_TRACE命令行参数

无论哪种方式,如果set函数的第二个参数设置错误,都不会给出错误信息。

本书会在10.6.3节提供一个函数,它会检查set函数的第二个参数,如果不可达,将会给出UVM_ERROR的信息。

第四章UVM中的TLM1.0通信

4.1 TLM1.0

UVM中通信主要有两种方案:

- 方案1:使用IMP直连(4.1-4.2)

- 方案2:使用FIFO连接

方案1直连需要在例化IMP的类中实现相关的功能任务/函数;一定需要一个IMP;在一个类中具有多个IMP时需要使用特殊的宏进行声明,不然会导致该功能函数/任务重载

方案2使用FIFO,可以看作一块缓存加两个IMP,因此不必要实现相关任务,只需要专注于数据

4.1.1 验证平台内部的通信

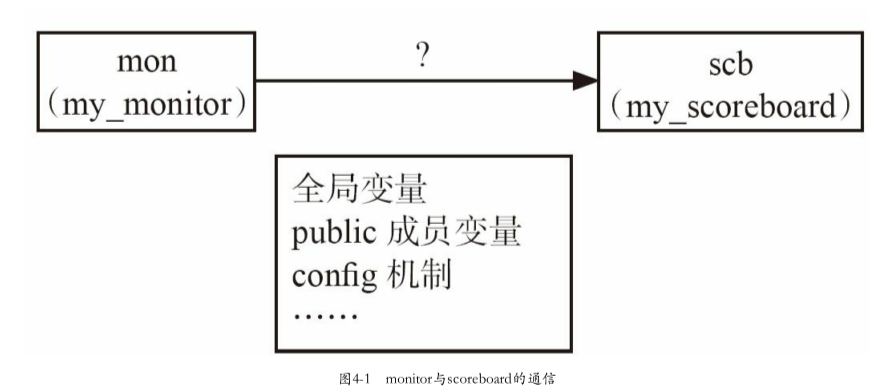

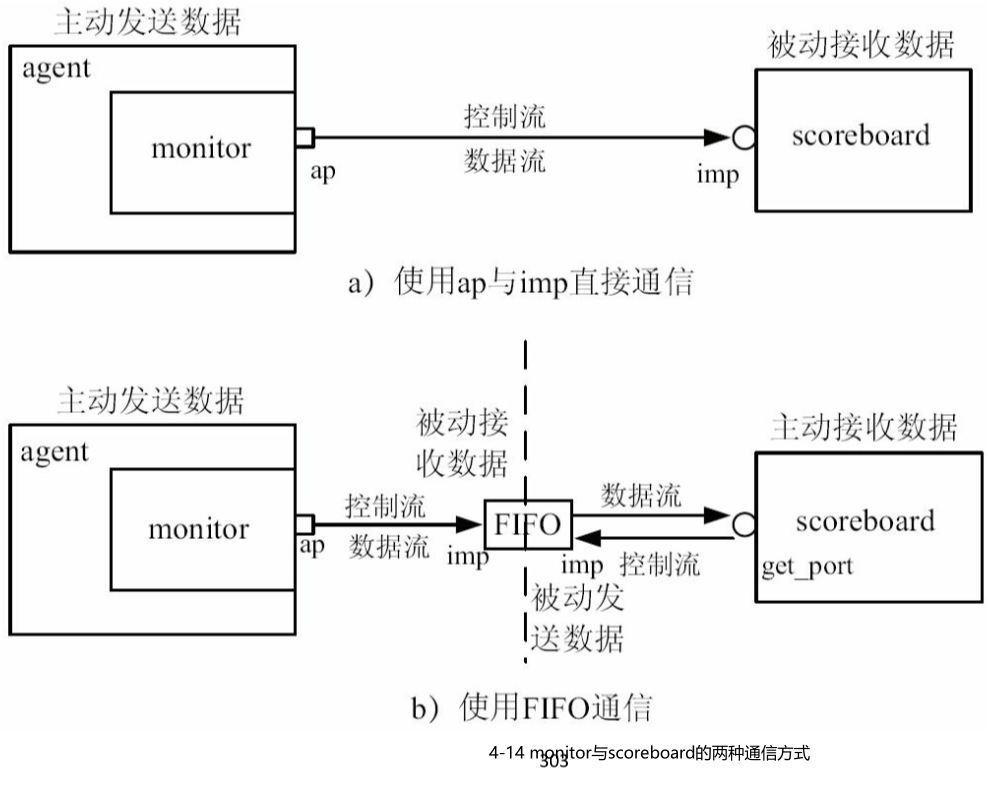

如果要在两个uvm_component之间通信,如一个monitor向一个scoreboard传递一个数据(如图所示)有哪些方法呢?

方法一:全局变量

使用全局变量,最简单的方法。在monitor里对此全局变量进行赋值,在scoreboard里监测此全局变量值的改变。这种方法 简单、直接,不过要避免使用全局变量,滥用全局变量只会造成灾难性的后果

方法二:从外部访问类的内部成员变量

从外部访问类的内部成员变量。在scoreboard中有一个变量,这个变量设置为外部可以直接访问的,即public类型的,在monitor中对此变量赋值。这个方法的问题在于,整个scoreboard里面的所有非local类型的变量都对monitor是可见的,而假如monitor的开发人员不小心改变了scoreboard中的一些变量,那么后果将可能会是致命的

方法三:config_db机制,设置与接收

uvm_object.步骤:

- 从

uvm_object派生出一个参数类config_object,在此类中有monitor要传给 scoreboard的变量- 在

base_test中,实例化这个config_object,并将其指针通过config_db#(config_object):set传递给scoreboard和monitor- 当monitor要和scoreboard通信时,只要把此

config_object中相应变量的值改变即可。scoreboard中则监测变量值的改变, 监测到之后做相应动作这种方法比上面的两种方法都要好,但是仍然显得有些笨拙:

- 一是要引入一个专门的config_object类

- 二是一定要有

base_test这个第三方的参与。在大多数情况下,这个第三方是不会惹麻烦的。但是永远不能保证某一个从base_test派生而来的类会不会改变这个config_object类中某些变量的值。也就是说,依然存在一定的风险方法四:最佳方案

使用TLM

为什么不用sv中的机制?

这些问题使用现行的SystemVerilog中的一些机制,如Semaphore、Mailbox,再结合其他的一些技术等都能实现,但是这其中的问题在于这种通信显得非常复杂,用户需要浪费大量时间编写通信相关的代码

解决办法:使用UVM的各种端口

UVM中的各种端口就可以实现这种功能:在monitor和scoreboard之间专门建立一个通道,让信息只能在这个通道内流动,scoreboard也只能从这个通道中接收信息

- 可以保证scoreboard中的信息只能从monitor中来,而不能从别的地方来;

- 同时赋予这个通道阻塞或者非阻塞等特性

4.1.2 TLM的定义

TLM是Transaction Level Modeling(事务级建模)的缩写,起源于SystemC的一种通信标准。

其他内容请参考《UVM入门进阶5(了解):TLM2与同步通信元件》

TLM通信常用术语:

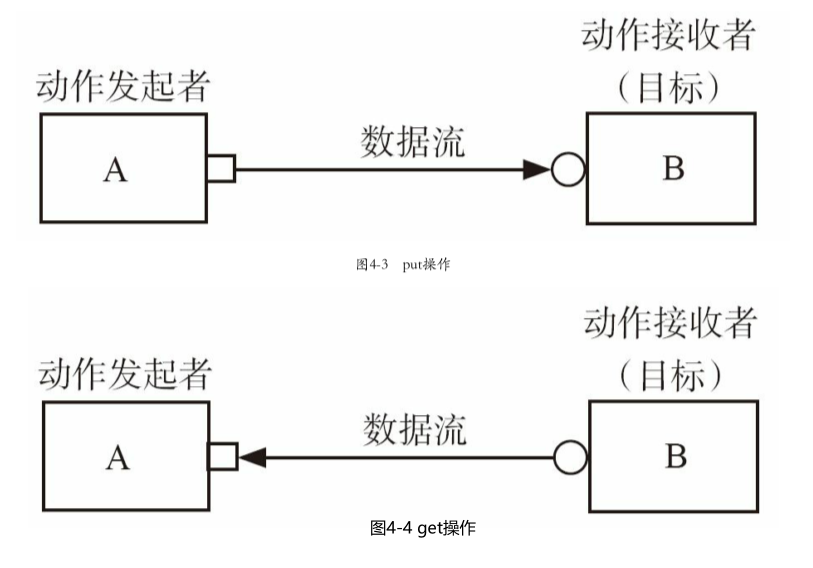

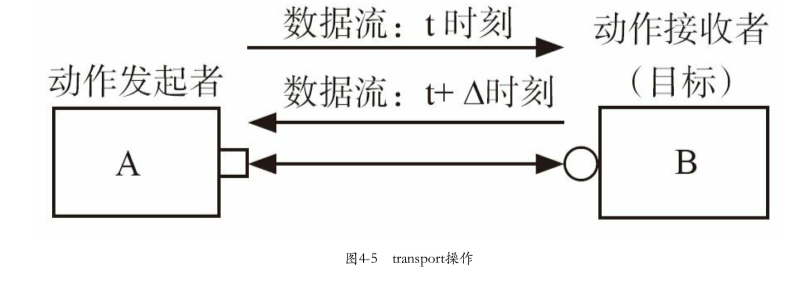

put操作,通信的发起者A把一个transaction发送给Bget操作,A向B索取一个transactiontransport操作/requeset-response操作,相当于一次put操作加一次get操作,这两次操作的”发起者”都是A,目标都是B(现实世界中, 相当于是A向B提交了一个请求request,而B返回给A一个响应response。所以这种transport操作也常常被称做request-response操作)

TLM中一共有三种端口:

- PORT

- EXPORT

- IMP(见4.2.2)

上面三种端口的控制流优先级为:PORT>EXPORT>IMP,在调用connect函数时只能高优先级调用,低优先级的端口作为入参

方框为PORT,圆圈为EXPORT,三角为IMP,PORT和EXPORT体现的是控制流而不是数据流

4.1.3 PORT与EXPORT

对应于不同的操作,有不同的PORT与EXPORT

UVM中常用的15个PORT有:

1 | |

UVM中常用的15个EXPORT,与上面15PORT一一对应:

1 | |

参数:

T:这个PORT/EXPORT中的数据流类型REQ, RSP:发起请求时传输的数据类型,返回的数据类型

blocking、nonblocking

- 都没有表示端口既可以用作是阻塞的,也可以用作是非阻塞的

blocking表示该端口只能用作阻塞nonblocking表示该端口只能用作非阻塞- 补充:这种划分方法可以看出,UVM把一个端口固定为只能执行某种操作(如对于

uvm_blocking_put_port#(T),它只能执行阻塞的put操作,想要执行非阻塞的put操作是不行的,想要执行get操作,也是不行的)

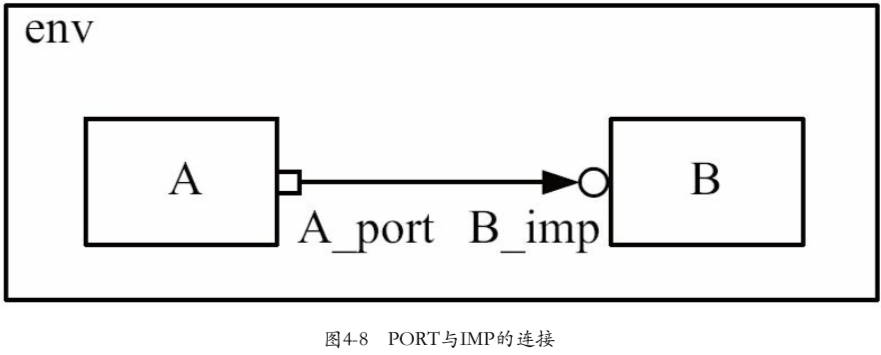

4.2a 直连通信

- 4.2.1节至4.2.6节以

blocking_put系列端口为例介绍PORT,EXPORT及IMP之间的互相连接 - 4.2.7节介绍

blocking_get系列端口的连接 - 4.2.8节介绍

blocking_transport系列端口的连接

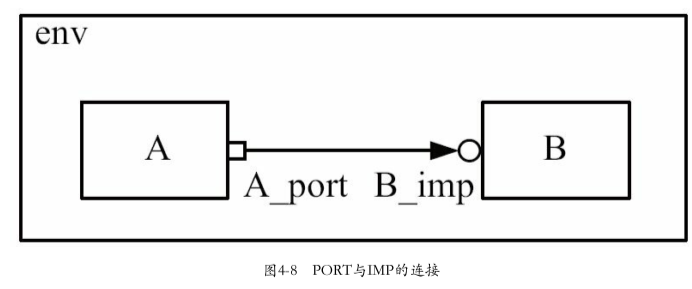

4.2.1 PORT与EXPORT的连接

1.UVM中使用connect函数来建立连接

如A要和B通信(A是发起者)则使用A.port.connect(B.export),但不能写成B.export.connect(A.port)。(因为在通信的过程中,A是发起者,B是被动承担者。这种通信时的主次顺序也适用于连接时,只有发起者才能调用connect函数,而被动承担者则作为connect的参数)

2.代码示例:A,B定义

类A的定义(PORT)

1 | |

port实例化参数:

2

3

4function new(string name,

uvm_component parent,

int min_size = 1;

int max_size = 1);

- 参数

name是该PORT名字- 参数

parent是uvm_component父节点变量- 参数

min_size是必须连接到这个PORT的下级端口数量的最小值- 参数

max_size是必须连接到这个PORT的下级端口数量的最大值- 补充:如果不看参数

min_size与max_size,new函数实际上是一个uvm_component的new函数

类B的定义(EXPORT)

1 | |

EXPORT实例化参数:

参考PORT

3.直接建立A_port与B_export的实例变量连接是错误的

我们将在下一节讨论IMP中实现A,B的连接,这节先说明直接连接是错误的

env中A,B错误的直接连接:

1 | |

运行上述代码,可以看到仿真器给出如下的错误提示:

1 | |

解释:A_port,B_export相当于两道门,直接相连没有数据存储,这笔transaction一定要由B_export后续的某个组件进行处理。在UVM中,完成这种后续处理的也是一种端口:IMP

4.2.2 UVM中的IMP

IMP是UVM中的精髓,承担了UVM中TLM的绝大部分实现代码,它的作用:完成接收数据后的处理工作,在UVM中这种后续处理也是端口,即IMP

按照控制流的优先级排序,UVM中三种端口顺序为:PORT、EXPORT、IMP。IMP的优先级最低,一个PORT可以连接到一个IMP,并发起三种操作,反之则不行

UVM中的IMP示例(这15种IMP与15种PORT和15种EXPORT一一对应):

1 | |

参数:

- T是这个IMP传输的数据类型

- IMP为实现这个接口的一个

component

IMP参数怎么理解?

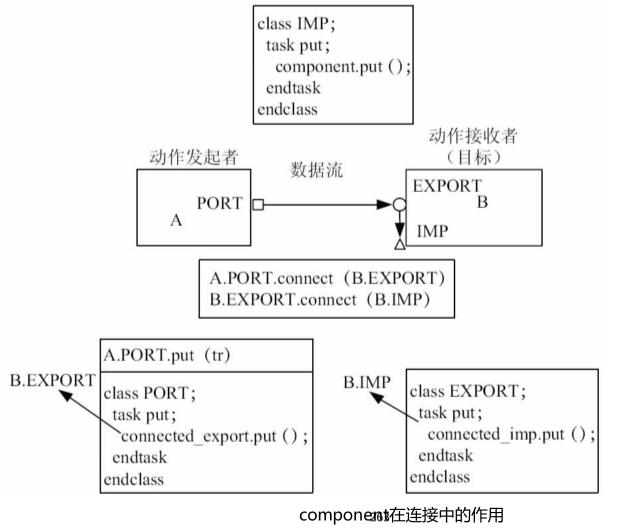

以blocking_put端口为例,在下图中,

A_port被连接到B_export,而B_export被连接到B_imp。当写下A.A_port.put(transaction)时,此时B.B_imp会通知B有transaction过来了,这个过程是如何进行的呢?可以简单理解成A.A_port.put(transaction)这个任务会调用B.B_export的put,B.B_export的put(transaction)又会调用B.B_imp的put(transaction),而B_imp.put最终又会调用B的相关任务,如B.put(transaction)。所以关于A_port的操作最终会落到B.put这个 任务上,这个任务是属于B的一个任务,与A无关,与A的PORT无关,也与B的EXPORT和IMP无关也就是说,(重要)这些put操作最终还是要由B这个component来实现,即要由一个component来实现接口的操作。所以每一个IMP要和一个component相对应。

总结,处理程序调用顺序:

调用A_port.put时的过程:

A_port.put-调用->B_export.put-调用->B_imp.put-调用->B.put重点!

理解下图中A连接到B_export,B_export连接到B_imp这个过程

2.代码示例

1 | |

连接解释:

A_port连接到B_export,B_export连接到B_imp(参考本节第一部分)

如果不实现B的put函数/任务没有实现,则运行代码会报错(为什么要实现B的put,请参考【IMP参数怎么理解?】)

4.2.3 PORT/EXPORT与IMP的连接

TLM中一共有三种端口:

- PORT

- EXPORT

- IMP(见4.2.2)

上面三种端口的控制流优先级为:PORT>EXPORT>IMP,在调用connect函数时只能高优先级调用,低优先级的端口作为入参

1.实现PORT与IMP的连接

背景:有三个component:A、B和env,其中env是A和B的父结点,现在要把A中的PORT和B中的IMP 连接起来实现通信

主要步骤:

第一步:A,B中的端口声明

A中采用了

uvm_blocking_put类型的PORT,因此B中IMP相应的类型是uvm_blocking_put_imp补充:参数解释

uvm_blocking_put_imp#(T, IMP)的参数T和IMP:T(要传输的transaction),IMP(实现接口功能的uvm_comonent,这里时B_imp所在的uvm_component B)第二步:功能接口实现:

B中的关键是定义一个任务/函数put,A_port的put操作最终要落到B的put上

补充:功能函数的名称要求

- A_port与B_imp是

blocking_put时B内需要定义1个成员:B.put任务/函数- A_port与B_imp是

nonblocking_put时B内需要定义2个成员:B.try_put函数,B.can_put函数- A_port与B_imp是

put时B内需要定义3个成员:B.put任务/函数,B.try_put函数,B.can_put函数

- A_port与B_imp是

blocking_get时B内需要定义1个成员:B.get任务/函数- A_port与B_imp是

nonblocking_get时B内需要定义2个成员:B.try_get函数,B.can_get函数- A_port与B_imp是

get时B内需要定义3个成员:B.get任务/函数,B.try_get函数,B.can_get函数

- A_port与B_imp是

blocking_peek时B内需要定义1个成员:B.peek任务/函数A_port与B_imp是

nonblocking_peek时B内需要定义2个成员:B.try_peek函数,B.can_peek函数A_port与B_imp是

peek时B内需要定义3个成员:B.peek任务/函数,B.try_peek函数,B.can_peek函数

- A_port与B_imp是

blocking_get_peek时B内需要定义2个成员:B.peek任务/函数,B.get任务/函数A_port与B_imp是

nonblocking_get_peek时B内需要定义4个成员:B.try_peek函数,B.can_peek函数,B.try_get函数,B.can_get函数A_port与B_imp是

get_peek时B内需要定义6个成员:B.peek任务/函数,B.try_peek函数,B.can_peek函数,B.get任务/函数,B.try_get函数,B.can_get函数

- A_port与B_imp是

blocking_transport时B内需要定义1个成员:B.transport任务/函数- A_port与B_imp是

nonblocking_transport时B内需要定义1个成员:B.nb_transport函数- A_port与B_imp是

transport时B内需要定义2个成员:B.transport任务/函数,B.nb_transport函数在前述的这些规律中,对于所有

blocking系列的端口可以是任务,也可以是函数。但是对于nonblocking系列端口来说,只能定义函数。第三步:连接

一定要在connect_phase中调用

connect进行连接,具体实现如下

2

3

4function void my_env::connect_phase(uvm_phase phase);

super.connect_phase(phase);

A_inst.A_port.connect(B_inst.B_imp);

endfunction(可选)第四步调用put:

A发送数据到B调用

put函数,具体实现如下(也是上一节A定义的代码):

2

3

4

5

6

7

8

9

10//文件:src/ch4/section4.2/4.2.3/my_env.sv

task A::main_phase(uvm_phase phase);

my_transaction tr;

repeat(10) begin

#10;

tr = new("tr");

assert(tr.randomize());

A_port.put(tr);//调用了十次put

end

endtask

2.EXPORT与IMP的连接

除了端口声明不同,其他与PORT和IMP连接完全一样(与4.2.2相比,这里export作为起点,而不是中间点),示例代码如下:

1 | |

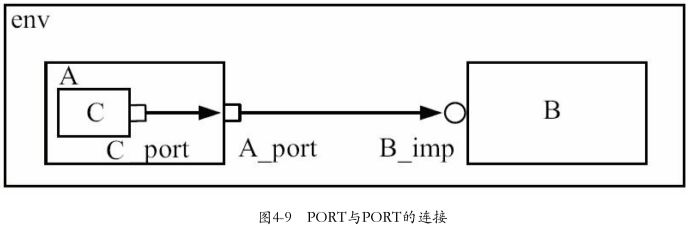

4.2.5 不同层次之间的连接(PORT与PORT,EXPORT与EXPORT)

1.PORT与PORT的连接

- 在前面的连接中,都是不同类型的端口之间连接(PORT与IMP、PORT与EXPORT、EXPORT与IMP),且不存在层次的关系。在UVM中,支持带层次的连接关系,如下图所示

- PORT与PORT之间的连接不只局限于两层,可以有无限多层

代码片段如下:

1 | |

隐含了控制流关系,内层port调用

connect

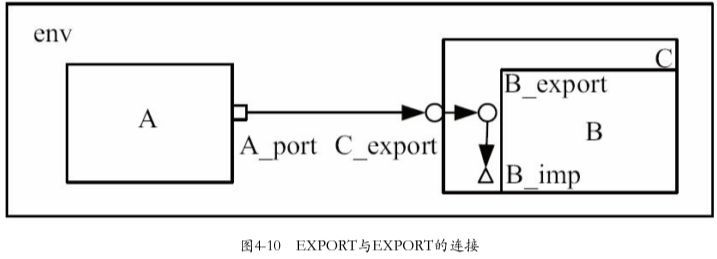

2.EXPORT与EXPORT的连接

除了支持PORT与PORT之间的连接外,UVM同样支持EXPORT与EXPORT之间的连接,如下图所示

EXPORT与EXPORT之间的连接也不只局限于两层,也可以有无限多层

A中是PORT,B与C中是EXPORT,B中还有一个IMP。UVM支持C的EXPORT连接到B的EXPORT,并最终连接 到B的IMP

示例代码如下:

1 | |

隐含了控制流方向,所以是外层调用内层

4.2b 其他功能系列

4.2.7 get

前面几节中都是以blocking_put系列端口为例进行介绍,本节介绍blocking_get系列端口的应用

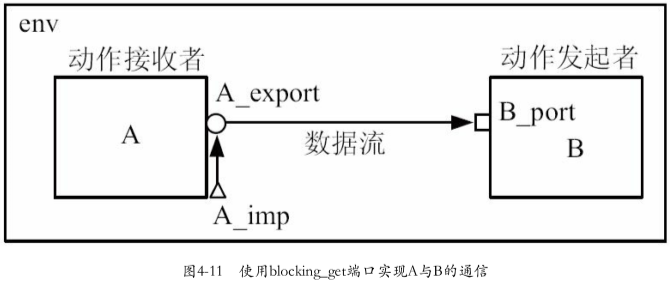

get系列端口与put系列端口在某些方面完全相反,若要实现下图从A到B的通信,使用blocking_get系列端口的框图

数据流依然是从A到B,但是A由动作发起者变成了动作接收者,而B由动作接收者变成了动作发起者

1.主要步骤:

第一步:A,B中的端口声明

B_port的类型为

uvm_blocking_get_portA_export的类型为

uvm_blocking_get_export,A_imp的类型为uvm_blocking_get_imp第二步:实现功能(与put类似)

uvm_blocking_get_imp所在的component要实现一个名字为get的函数/任务第三步:连接

第四步:调用get

2.代码详解

1 | |

涉及:

①定义接口:

A_export,A_imp②定义功能:数据最终流向A,所以需要A_imp,需要实现数据处理功能,即

get,改功能主要将A内transaction发送到B③连接:在A中把A_export与A_imp连接

1 | |

涉及:

① 端口定义

④调用

get,这个get最终会调用到A.get,从而获取到A中transcation

1 | |

涉及:

③ B_port与A_export连接

3.其他get端口连接

与blocking_put系列端口类似:

blocking_get_port也可以直接连接到blocking_get_impblocking_get_port也可以连接到blocking_get_portblocking_get_export也可以连接到blocking_get_export

在这些连接关系中,需要谨记的是连接的终点必须是一个IMP

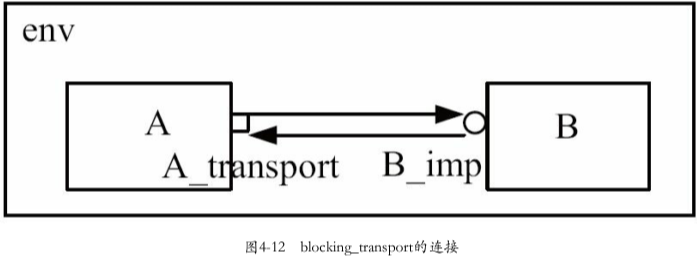

4.2.8 transport

特性:双向,与*_get和*_put不同,在*_transport系列端口中, 通信变成了双向的,即又有get又有put

1.主要步骤:

第一步:A,B中的端口声明

A中定义一个

uvm_blocking_transport_*B中需要定义一个类型为

uvm_blocking_transport_imp的IMP第二步:实现功能

IMP所在的component要实现一个名字为

transport任务/函数第三步:连接

第四步:调用

transport

2.代码详解

1 | |

涉及:

① A中定义一个

uvm_blocking_transport_port④ 调用

transport,把生成的transaction作为第一个参数REQ发送到B_imp,B_imp接收到这个参数调用transport任务做了点什么,最后把操作的结果作为transport第二个参数RSP返回回去,A根据RSP进行后面操作

1 | |

涉及:

① B中需要定义一个类型为

uvm_blocking_transport_imp的IMP② 实现

transport,通过A调用主要实现:A把生成的transaction作为第一个参数REQ发送到B_imp,B_imp接收到这个参数调用transport任务做了点什么,最后把操作的结果作为transport第二个参数RSP返回回去,A根据RSP进行后面操作

1 | |

涉及:

③ A_transport_port与B_imp连接

3.其他连接

- 在本例中:

uvm_blocking_transport_port直接连接到uvm_blocking_transport_imp - 还可以:

uvm_blocking_transport_port前者还可以连接到uvm_blocking_transport_export - 总结:

uvm_blocking_transport_port,uvm_blocking_transport_export,uvm_blocking_transport_imp连接关系与uvm_blocking_put系列端口类似

4.2.9 nonblocking

特性:非阻塞,nonblocking端口的所有操作都是非阻塞的,换言之,必须用函数实现,而不能用任务实现,以用nonblocking端口实现图4-8所示的连接关系为例

1.主要步骤:

第一步:A,B中的端口声明

A中定义一个

uvm_nonblocking_*_*_portB中需要定义一个类型为

uvm_nonblocking_*_imp的IMP第二步:实现功能

IMP所在的component要实现:

can_put/get/peek函数,try_put/get/peek函数第三步:连接

第四步:调用

由于端口变为了非阻塞的,所以在送出

transaction之前需要调用can_put函数来确认是否能够执行put操作。can_put最终会调用 B中的can_put,然后再调用try_put真正发送到B_imp中

2.代码详解

1 | |

涉及:

① A中定义一个类型为

uvm_nonblocking_put_port的PORT④ 调用

can_put查询是否能发送,try_put进行发送

1 | |

涉及:

① B中定义一个类型为

uvm_nonblocking_put_imp的IMP② 实现

can_put查询是否能发送的函数,try_put进行发送数据的处理(这里是直接接收了)

1 | |

涉及:

③ A_port与B_imp连接

4.2.10 peek

详情参考4.3.4节,FIFO中的内容

peek端口与get相似,其数据流、控制流都相似,唯一的区别在于当get任务被调用时,FIFO内部缓存中会少一个transaction,而 peek被调用时,FIFO会把transaction复制一份发送出去,其内部缓存中的transaction数量并不会减少

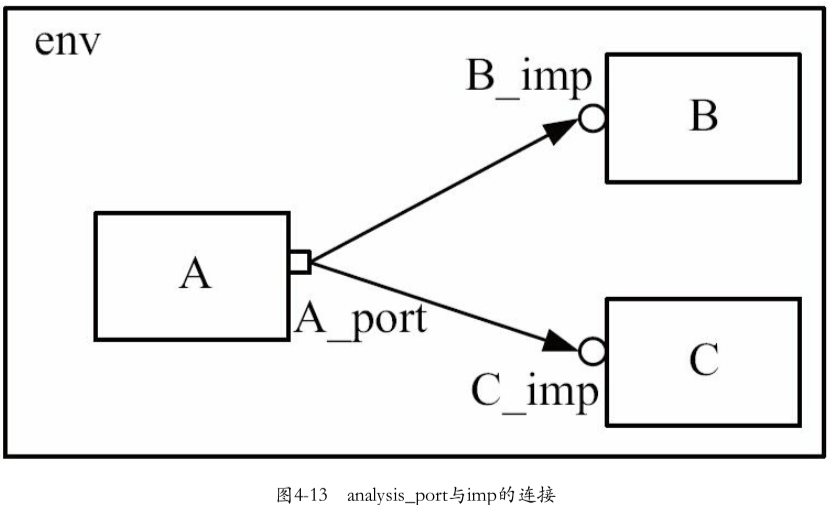

4.3.1 analysis

除了4.2提到的5个功能系列(get/put/transport/peek/get_peek),UVM中还有一个功能系列(analysis)可以实现一对多通信的功能,即广播功能,主要有一下三个

1 | |

1.analysis端口与普通端口的区别:

- 一个analysis_port(analysis_export)可以连接多个IMP,且IMP的类型必须是uvm_analysis_imp

- 对于analysis_port和analysis_export来说,没有阻塞和非阻塞的概念。 因为它本身就是广播,不必等待与其相连的其他端口的响应,所以不存在阻塞和非阻塞

- 对于analysis系列端口来说,只有一种操作:

write(对于普通的put系列端口,有put、try_put、can_put等操作,对于普通的get系列端口,有get、try_get和can_get等操作)

2.上图analysis端口关键代码实现定义

1 | |

4.3.2a 跨层次的三种连接方案

考虑图2-13中o_agt的monitor与scoreboard之间的通信,使用analysis_port实现

1 | |

在env中可以使用connect连接。由于monitor与scoreboard在UVM树中间隔了o_agt,所以这里有三种连接方式

1.第一种:直接跨层次引用

直接在env中跨层次引用monitor中的ap:

1 | |

2.第二种:例化端口连接

在agent中声明一个ap并实例化它,在connect_phase将其与monitor的ap相连,并可以在env中把agent的ap直接连接到 scoreboard的imp:

1 | |

3.第三种:间接跨层次引用(推荐)

在agent中声明一个ap,但是不实例化它,让其指向monitor中的ap。在env中可以直接连接agent的ap到scoreboard的 imp:

1 | |

第一种最简单,但是其层次关系并不好,第二种稍显麻烦,第三种既具有明显的层次关系,同时其实现也较简单

4.3.2b 一个component内有多个IMP

问题背景:在上面的例子中,scoreboard只接收一路数据,但在现实情况中,scoreboard除了接收monitor的数据之外,还要接收reference model的数据。相应的scoreboard就要再添加一个 uvm_analysis_imp的IMP,如model_imp。此时问题就出现了,由于接收到的两路数据应该做不同的处理,所以这个新的IMP也要有一个write任务与其对应。但是write只有一个,怎么办?

一句话问题背景(以下内容都以analysis为例):当一个comp中需要连接多个端口,需要例化多个IMP,多个IMP需要多个write函数,这可怎么办?

方案1:使用FIFO通信,直接不用实现write函数了(4.3中进行解释)

方案2:使用`uvm_analysis_imp_decl宏,直接添加(本节解释)

使用方案2:

UVM考虑到了这种情况,它定义了一个宏`uvm_analysis_imp_decl来解决这个问题,其使用方式为:

1 | |

步骤:

- 上述代码通过宏

`uvm_analysis_imp_decl声明了两个后缀_monitor和_model- UVM会根据这两个后缀定义两个新的IMP类:

uvm_analysis_imp_monitor和uvm_analysis_imp_model,

- UVM会根据这两个后缀定义两个新的IMP类:

- 在

my_scoreboard中分别声明并实例化这两个类:monitor_imp和model_imp - 当与

monitor_imp相连接的analysis_port执行write函数时,会自动调用write_monitor函数 - 当与

model_imp相连接的analysis_port执行write函数时,会自动调用write_model函数

所以,只要完成后缀的声明,并在write后面添加上相应的后缀就可以正常工作了

我的一点总结

4.2主要提到了TLM中的三个端口:PORT,EXPORT,IMP,优先级从左往右,控制流从左往右(还有两种端口ananlaysis,4.3节进行分析)

三种端口又根据功能,分为了不同类型:blocking_put,blocking_get,blocking_transport,noblocking_put,noblocking_get,noblocking_transport

三种端口在一个连接中应保持功能类型的统一,例如:这是一条完整的put通路从blocking_put_port到blocking_put_export再到blocking_put_imp

功能特性主要有:put发送,get接收,transport双向,noblocking非阻塞

- 阻塞:实现的时候可以是任务,从而有了阻塞时间

- 非阻塞:实现的时候应该全都是函数,不应该有时间

IMP类型的端口,需要对数据进行处理,具体讲是需要在定义了IMP端口的类中,实现不同的功能特性任务/函数(对于非阻塞而言只有函数)

- 对于

put功能,需要实现数据的接收 - 对于

get功能,需要实现数据的发送(因为port调用了get,get对应到imp.get并最终调用到该类中的相关函数/任务) - 对于

transport功能,需要实现接收一个请求,返回一个响应 - 对于

nonblocking,需要实现try_*处理函数,以及can_*来判断是否能调用处理函数

4.3 FIFO通信

FIFO的类型有两种:

- 一种是4.3.3中的

uvm_tlm_analysis_fifo - 另外一种是

uvm_tlm_fifo

这两者的唯一差别在于前者有一个analysis_export端口,并且有一个write函数,而后者没有。4.3.4节中介绍的所有端口同时适用于这两者

4.3.3 使用FIFO通信

4.3.2a节中monitor和scoreboard的通信,monitor占据主动地位, 而scoreboard只能被动地接收

那么有没有简单的方法呢?让scoreboard实现主动的接收呢?这两个问题的答案都是肯定的,那就是使用第2章使用的方式:利用FIFO来实现monitor和scoreboard的通信

4-14解释

如图4-14b所示,在agent和scoreboard之间添加一个

uvm_analysis_fifo,FIFO的本质是一块缓存加两个IMPFIFO的连接关系中:

- 在monitor与与FIFO的连接关系中,monitor中依然是

analysis_port- FIFO中是

uvm_analysis_imp,数据流和控制流的方向相同- 在scoreboard与FIFO的连接关系中,scoreboard中使用

blocking_get_port端口

FIFO的本质:FIFO的本质是一块缓存加两个IMP

2.FIFO的例化与连接

主要展示my_env.sv(设计框架参考4.3.2a中提到的),FIFO例化与连接的代码

这里再解释一下为什么例化三个FIFO,因为是参考第二章的例子:

agt_scb_fifo意思是从agent到scoreboardagt_mdl_fifo意思是从agent到modelmdl_scb_fifo意思是从model到scoreboard

实现了两条到scoreboard的事务级内部通信:

①dut->agent(monitor)->scoreboard

②agent(drv)->model->scoreboard

1 | |

构造函数:

function new(string name, uvm_component parent = null, int size = 1);

- FIFO在本质上是一个component,所以其前两个参数是uvm_component的

new函数中的两个参数- 第三个参数是

size,用于设 定FIFO缓存的上限,在默认的情况下为1,如果为0则缓存无限连接要点:

- 使用FIFO通信后,连接主要是FIFO的连接

- FIFO上没有

IMP,因为EXPORT就是IMP实现的,解释见下方连接到FIFO的是EXPORT而不是IMP

原因:

实际上,FIFO中的

analysis_export和blocking_get_export虽然名字中有关键字export,但是其类型却是IMP。UVM为了掩饰IMP的存在,在它们的命名中加入了export关键字。如analysis_export的原型如下:

>uvm_analysis_imp #(T, uvm_tlm_analysis_fifo #(T)) analysis_export;

3.FIFO连接的好处

第一个好处是不必在scoreboard中再写一个名字为write的函数。scoreboard可以按照自己的节奏工作,而不必跟着monitor的节奏

第二个好处是FIFO的存在隐藏了IMP,这对于初学者来说比较容易理解

第三个好处是可以轻易解决上一节讲到的当reference model和monitor同时连接到scoreboard应如何处理的问题。事实上,FIFO的存在自然而然地解决了它,这根本就不是一个问题了

4.3.4a FIFO上的端口

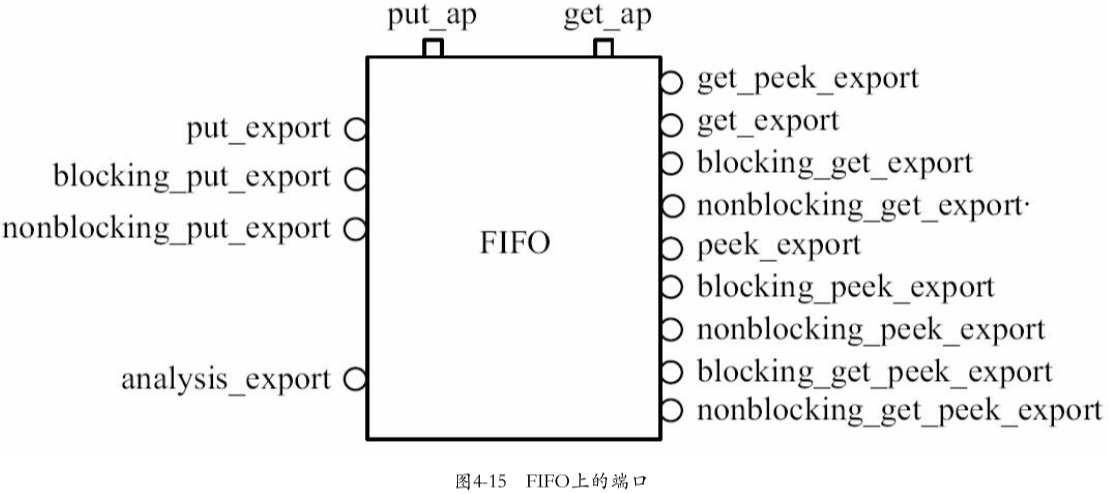

4.3.3介绍了FIFO上的blocking_get_export(用于数据获取)和analysis_export(用于数据输入)端口(两个端口实际上是IMP),实际上FIFO端口有众多接口。uvm_tlm_analysis_fifo端口示意图如下:

端口:

一共有12+1+2=15个端口,其中12个export是除transport系列外的12种IMP,1个是

uvm_tlm_analysis_fifo的analysis_export,2个是analysis_port2个

analysis_port的作用:

put_ap:

- 大致内容:FIFO的

put任务被调用后,不仅会缓存数据到FIFO,还会通过put_ap端口额外发送出transaction- 具体细节:当FIFO上的

blocking_put_export或者put_export被连接到一 个blocking_put_port或者put_port上时,FIFO内部被定义的put任务被调用,这个put任务把传递过来的transaction放在FIFO内部的缓存里,同时,把这个transaction通过put_ap使用write函数发送出去。FIFO的put任务定义如下:

2

3

4virtual task put(input T t);

m.put(t);//m即是FIFO内部的缓存,使用SystemVerilog中的mailbox来实现

put_ap.write(t);

endtask

get_ap:

- 与

put_ap相似,当FIFO的get任务被调用时,同样会有一个transaction从get_ap上发出,FIFO的get任务定义如下

2

3

4

5

6virtual task get(output T t);

m_pending_blocked_gets++;

m.get(t);

m_pending_blocked_gets--;

get_ap.write(t);

endtask

4.3.4b FIFO的调试函数

UVM也提供了几个函数用于FIFO的调试

used()函数用于查询FIFO缓存中有多少transactionis_empty()函数用于判断当前FIFO缓存是否为空is_full()用于判断当前FIFO缓存是否已经满了flush()用于清空FIFO缓存中的所有数据,一般用于复位

4.4 用FIFO还是用IMP(端口数组与for循环)

每个人对于这个问题都有各自不同的答案

FIFO优点:

- 在用FIFO通信的方法中,完全隐藏了IMP这个UVM中特有、而TLM中根本就没有的东西。用户可以完全不关心IMP。因此,对于用户来说,只需要知道

analysis_port、blocking_get_port即可。这大大简化了初学者的工作量。尤其是在scoreboard面临多个IMP,且需要为IMP声明一个后缀时,这种优势更加明显 - 对于使用端口数组的情况,FIFO要优于IMP,可以使用for循环进行例化、函数调用和端口连接(端口数组<—>FIFO数组的端口)

FIFO缺点:FIFO连接的方式增加了env中代码的复杂度,满满的看上去似乎都是与FIFO相关的代码。尤其是当要连接的端口数量众多时,这个缺点更加明显(毕竟直连不需要在env中例化FIFO,且只需要写一行connect就够了)

2022年11月30日,20:25:04

第5章 UVM验证平台的运行

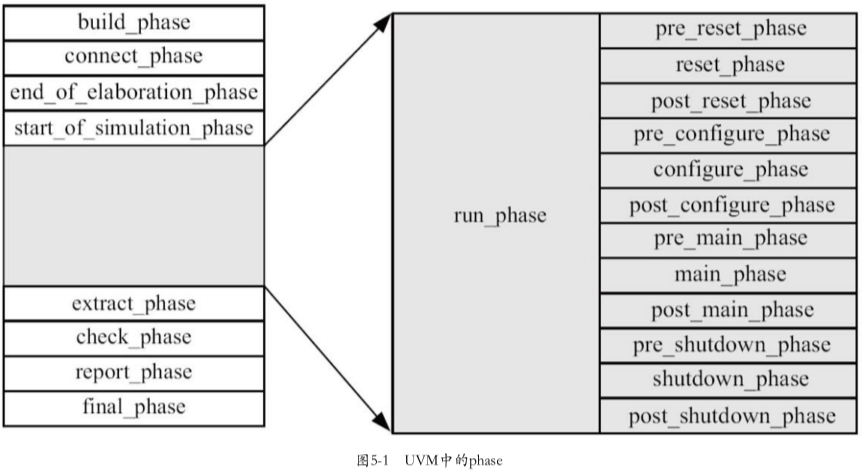

5.1 phase机制

5.1.1 phase基础

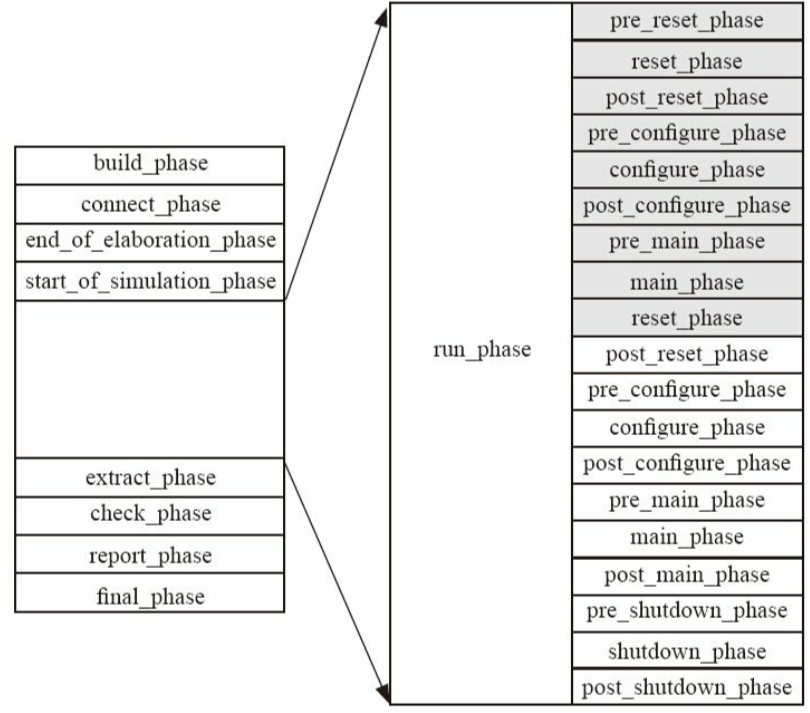

1.phase分类

UVM中的phase,按照其是否消耗仿真时间($time打印出的时间)的特性,可以分成两大类:

- function phase:下图中白色的phase

- task phase:下图中灰色的phase,包括

run_phase和12个run-tiime phase

对于task phase分为两种,一种是run_phase,一种是run-time(运行时/动态运行时) phase,其中run-time phase包括12个小phase

总结:

reset_phase主要做一些清理工作,并等待复位完成为什么这么多phase

- 不会都用:在一般的应用中,无论是

function phase还是task phase都不会将它们全部用上- 使用频率最高:的是

build_phase、connect_phase和main_phase- 好处,方便迁移:这么多phase除了方便验证人员将不同的代码写在不同的phase外,还有利于其他验证方法学向UVM迁移。一般的验证方法学都会把仿真分成不同的阶段,但是这些阶段的划分通常没有UVM分得这么多、这么细致。所以一般来说,当其他验证方法学向UVM迁移的时候,总能找到一个phase来对应原来方法学中的仿真阶段,这为迁移提供了便利

run-time phase引入时间:动态运行(run-time)phase是UVM1.0引入的新的phase,其他phase则在UVM1.0之前(即UVM1.0EA版和OVM中)就已经存在了为什么引入12个

run-time phase?

- 为了精细化的控制:分成小的phase是为了实现更加精细化的控制。reset、configure、main、shutdown四个phase是核心,这四个phase通常模拟DUT的正常工作方式,在reset_phase对DUT进行复位、初始化等操作,在configure_phase则进行DUT的配置,DUT的运行主要在main_phase完成,shutdown_phase则是做一些与DUT断电相关的操作。通过细分实现对DUT更 加精确的控制。假设要在运行过程中对DUT进行一次复位(reset)操作,在没有这些细分的phase之前,这种操作要在 scoreboard、reference model等加入一些额外的代码来保证验证平台不会出错。但是有了这些小的phase之后,分别在scoreboard、 reference model及其他部分(如driver、monitor等)的reset_phase写好相关代码,之后如果想做一次复位操作,那么只要通过phase的跳转,就会自动跳转回reset_phase。(关于跳转的内容,请参考5.1.7节)

run_phase是OVM遗留的phase作用

- function phase:八个

phase- task phase:

run_phase以及12个run-time phasefunction phase

connect_phase

- 传递实例句柄,包括:

reg_model实例在base中传递给env,env传递给ref_model

run-time phase:

reset、configure、main、shutdown四个phase是核心,这四个phase通常模拟DUT的正常工作方式,通过细分实现对DUT更加精确的控制

- 在

reset_phase对DUT进行复位、初始化等操作- 在

configure_phase则进 行DUT的配置- DUT的运行主要在

main_phase完成shutdown_phase则是做一些与DUT断电相关的操作

run_phase是OVM遗留的

2.phase执行的时间顺序

phase首先是按照时间决定当前应该执行哪个phase,再从空间中遍历所有组件运行,当所有组件执行完后该phase进入到下一个phase

所有的phase都会按照图5-1中的顺序自上而下自动执行/启动:

- 对于function phase同一时间只有一个phase在执行

- 对于task phase有两个phase并行:

run_phase和某个run-time phase并行运行,顺序大致如下代码- 对于

run-time phase,执行也是从上到下进行 - 使用domain特性可将不同组件的

run-time phase分隔(见5.3节)

- 对于

1 | |

3.phase执行的空间顺序(以UVM树的视角)

主要顺序:

- build_phase:自上而下

- 其他所有phase(function,task phase):自下而上

同一层次顺序:根据例化时的名称使用字典序的排序

注意:UVM并未保证一直会是这个顺序(这个顺序是在UVM1.1d源代码中找到的,UVM并未保证一直会是这个顺序)。如果代码存在依赖这种顺序的执行,必须立刻修改,并杜绝这种依赖出现

UVM树的遍历顺序:深度优先

注意:如果存在要求位于不同分支的两个组件,某一组件phase提前于另一组件phase执行的代码,必须立刻修改,并杜绝这种依赖出现

不同组件的

task phase顺序并行启动

task phase运行耗费时间,所以它并不是等到“下面”的phase(如driver的run_phase)执行完才执行“上面”的phase(如agent 的run_phase),而是将这些run_phase通过fork…join_none的形式全部启动。所以,更准确的说法是自下而上的启动,同时在运行不同组件的

task phase执行同步(三个同步):

- 所有组件

run-time phase之间需要同步(即所有组件某一run-time phase都进行结束,才代表该run-time phase进行结束,否则提前结束的组件进行等待)- 所有组件

run_phase需要同步(即所有组件run_phase都进行结束,才代表run_phase进行结束,否则提前结束的组件进行等待)run_phase与post_shutdown_phase的同步(即所有组件的run_phase和pose_shutdown_phase都结束,才代表task phase结束,进入extract_phase)

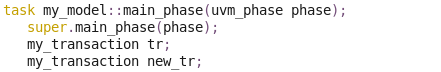

5.1.5 super.phase的使用

前文代码中有的地方调用super.xxx_phase有的地方不调用,这里做下总结

1.前文代码中

在main_phase中,有时出现super.main_phase, 有时又不会;

在build_phase中,一般都会出现super.build_phase

2.何时调用super.xxx_phase

何时调用super.xxx_phase?

- 场景1(使用机制):对于

build_phase且需要自动获取config_dg::set设置参数(config_db),或使用了field automation的时需要调用super.build_phase(如果build_phase不需要自动获得参数就不调用super.build_phase) - 场景2(继承):对于用户自定义类的子类,如果自定义的父类在某个

phase中定义了重要内容,则子类中应该调用super.xxx_phase - 其他大多数情况完全可以不加上

super.xxxx_phase语句,如第2章中所有的super.main_phase都可以去掉。因为除了build_phase外,UVM实现的基础phase没有任何作用,如下代码所示

1 | |

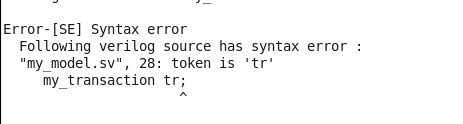

3.补充

以下是我在搜索资料的时候找到的内容

函数/任务内部成员变量定义应在最前面

在my_model中,super用于my_transaction 声明之前如图

会出现下图错误

这样定义则正常,如图

原因:SystemVerilog要求,声明必须位于语句之前(调用

super.xxx_phase就已经开始运行语句了)https://bbs.eetop.cn/thread-852901-1-1.html

new构造函数

new构造函数必须调用super.new(name, parent);,原因:SystemVerilog要求扩展类构造函数调用https://stackoverflow.com/questions/37672145/example-with-super-function-call-in-uvm

5.1.6 build_phase与UVM_ERROR

在end_of_elaboration_phase及其前的phase中,如果出现了一个或多个UVM_ERROR,那么UVM就认为出现了致命错误,会调用uvm_fatal结束仿真。

好处:提高debug效率

UVM的这个特性在小型设计中体现不出优势,但是在大型设计中,这一特性非常有用。大型设计中,真正仿真前的编译、优化可能会花费一个多小时的时间。完成编译、优化后开始仿真,几秒钟后,出现一个

uvm_fatal就停止仿真。当修复了这个问题后,再次重新运行,发现又有一个uvm_fatal出现。如此反复,可能会耗费大量时间。但是如果将这些uvm_fatal替换为uvm_error,将所有类似的问题一次性暴露出来,一次性修复,这会极大缩减时间,提高效率2.2.4节

我们在

connect_phase中,如果config_db::set没有设置成功用则调用`uvm_fatal来结束仿真事实上这里调用

`uvm_error也能结束仿真

5.1.7 phase的跳转

整个验证平台的phase可以实现跳转,通过调用下方两个函数,进行跳转和参数的获取(补充:多domain的run-time phase跳转phase的跳转只能局限在某一domain中(原文5.3.3))

跳转函数

jump

function void uvm_phase::jump(uvm_phase phase);

- 参数必须是一个

uvm_phase类型的变量

uvm_phase类型的变量获取方式如下:

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21uvm_build_phase::get();

uvm_connect_phase::get();

uvm_end_of_elaboration_phase::get();

uvm_start_of_simulation_phase::get();

uvm_run_phase::get();

uvm_pre_reset_phase::get();

uvm_reset_phase::get();

uvm_post_reset_phase::get();

uvm_pre_configure_phase::get();

uvm_configure_phase::get();

uvm_post_configure_phase::get();

uvm_pre_main_phase::get();

uvm_main_phase::get();

uvm_post_main_phase::get();

uvm_pre_shutdown_phase::get();

uvm_shutdown_phase::get();

uvm_post_shutdown_phase::get()

uvm_extract_phase::get();

uvm_check_phase::get();

uvm_report_phase::get();

uvm_final_phase::get();那些phase可以作为jump的参数呢?

uvm_reset_phase::get();及以后的phase(除run_phase)run_phase也是不可以跳转的向前跳转与向后跳转

从

main_phase跳转到reset_phase是一种向前跳转,这种向前跳转中,只能是main_phase前的动态运行(run-time phase)中的一个从

main_phase跳转到shutdown_phase是一种向后跳转,在向后跳转中,除了动态运行的phase外(run-time phase),还可以是函数phase,如可以从main_phase跳转到final_phase

我知道你在找这张图

2.一个示例

假如在验证平台中监测到reset_n信号为低电平,则马上从main_phase跳转到reset_phase,driver的代码如下:

1 | |

reset_phase`主要做一些清理工作,并等待复位完成。`main_phase`中一旦监测到reset_n为低电平,则马上跳转到`reset_phase

在my_case中控制objection代码如下:

1 | |

运行上面例子的结果:

1 | |

- 结果整个验证平台都从

main_phase跳转到了reset_phase - 出现了一个UVM_WARNING

- 整个验证平台phase的运行结果图:

为什么会有

UVM_WARNING?这是因为在 my_driver中调用jump时,并没有把my_case0中提起的objection进行撤销

3.跳转的清理!!!

跳转中最难的地方在于跳转前后的清理和准备工作。如上面的运行结果中的警告信息就是因为没有及时对objection进行清理

对于scoreboard来说,这个问题可能尤其严重。在跳转前,scoreboard的expect_queue中的数据应该清空,同时要容忍跳转后DUT可能输出一些异常数据。

5.1.8 phase机制的必要性

1.Verilog背景

Verilog中有非阻塞赋值和阻塞赋值,相对应的,在仿真器中要实现分为NBA区域和Active区域[1],这样在不同的区域做不同 的事情,可以避免因竞争关系导致的变量值不确定的情况。同样的,验证平台是很复杂的,要搭建一个验证平台是一件相当繁杂的事情,要正确地掌握并理顺这些步骤是一个相当艰难的过程

[1] 可以参照《IEEE Std 1364—2005 IEEE Standard Verilog® Hardware Description Language》

其他参考:https://blog.csdn.net/dinghj3/article/details/122513314

2.UVM的phase

- 在不同时间做不同的事情,这就是UVM中phase的设计哲学

- 仅仅划分成phase是不够的,phase的自动执行功能才极大方便了用户

- phase的引入在很大程度上解决了因代码顺序杂乱可能会引发的问题。遵循UVM的代码顺序划分原则(如build_phase做实例化工作,connect_phase做连接工作等),可以在很大程度上减少验证平台开发者的工作量,使其从一部分杂乱的工作中解脱出来

5.1.9 phase的调试

如果碰到问题后每次都使用`uvm_info在每个phase打印不同的信息显然是不能满足要求的,使用命令行参数自动打印

命令行参数:

1 | |

运行时命令输出:

1 | |

5.1.10 超时退出

超时背景:在验证平台运行时,有时测试用例会出现挂起(hang up)的情况。在这种状态下,仿真时间一直向前走,driver或者monitor并没有发出或者收到transaction,也没有UVM_ERROR出现

测试用例特性:一个测试用例的运行时间是可以预计的,如果超出了这个时间,那么通常就是出错了。在UVM中通过uvm_root的set_timeout函数可以设置超时时间:

1 | |

如上的代码将超时的时间定为500ns。如果达到500ns时,测试用例还没有运行完毕,则会给出一条uvm_fatal的提示信息,并退出仿真

set_timeout:

- 参数1:要设置的时间

- 参数2:此设置是否可以被其后的其他set_timeout语句覆盖(0不可以,1可以)

`UVM_DEFAULT_TIMEOUT宏:

- 默认的超时退出时间是9200s,是通过宏

`UVM_DEFAULT_TIMEOUT来指定的命令行

- 除了可以在代码中设置超时退出时间外,还可以在命令行中设置

- 其中

timeout是要设置的时间,overridable表示能否被覆盖,其值可以是YES或者NO

2

3<sim command> +UVM_TIMEOUT=<timeout>,<overridable>

如

<sim command> +UVM_TIMEOUT="300ns, YES"总结一下提到过让验证平台停止的方法:

- 直接

`uvm_fatal- 设置

UVM_ERROR阈值- 在

end_of_elaboration_phase及其前的phase中,直接调用`uvm_errorset_timeout超时退出drop_objection通知系统可以关闭验证平台(之前需要先raise_objection)

5.2 objection机制

objection字面的意思——反对、异议

5.2.1 objection与task phase

objection的引入是为了解决何时结束仿真的问题,它更多面向task phase,而不是面向function phase,不过在function phase中使用也不报错(原文5.2.2)

1.机制使用

在验证平台中,可以通过drop_objection来通知系统可以关闭验证平台。当然,在撤销 之前首先要

raise_objection,示例代码如下:

1 | |

2

3virtual function void raise_objection ( uvm_object obj = null,

string description = "",

int count = 1 )

- 第一个形参phase是加入objection的phase,如果未指定object或为 null,则选择隐式顶级组件uvm_root

- 第二个形参是字符串,用于标记特定的反对意见,用于跟踪/调试,默认为空

- 第三个形参为objection的数量,默认为1

2.phase与objection

1.UVM

- 在进入到某一phase时,UVM会收集此phase提出的所有objection,并实时监测所有objection是否已经被撤销

- 当发现所有objection都已经撤销后,那么就会关闭此phase,开始进入下一个phase

- 如果UVM发现此phase没有提起任何objection,那么将会直接跳转到下一个phase中

- 当所有的phase都执行完毕后,就会调用

$finish来将整个的验证平台关掉

2.run_phase与run-time phase的objection

对于run_phase来说,有两种方式rasie_objection:

- 方式1:其他

run-time phase中有rasie_objection - 方式2:自己

rasie_objection

对于run-time phase只能自己rasie_objection,在run_phase中的rasie_objection对它没有作用

5.2.2 形参phase的必要性

所有phase的函数/任务的形参中,都有一个phase,如:

1 | |

为什么要有这个形参?

因为要便于在任何component的phase中都能raise_objection,而要raise_objection则必须通过phase.raise_objection来完成,所以必须将phase作为参数传递到main_phase等任务中。可以想象,如果没有这个phase参数,那么想要提起一个objection就会比较麻烦了

作者真能扯

5.2.3 在哪控制objection

在第2章的例子中,最初是在driver中

raise_objection,但是事实上,在driver中raise_objection的时刻并不多。这是因为driver中通常都是一个无限循环的代码,由于无限循环的特性,phase.drop_objection永远不会被执行到

在driver,monitor和reference model中,有类似的情况,它们都是无限循环的,因此一般其中控制objection

一般来说,在一个实际的验证平台中,通常会选择以下两种方案之一:

方案1:在scoreboard中进行控制

在2.3.6节中,scoreboard的main_phase被做成一个无限循环如果要在scoreboard中控制objection,则需要去除这个无限循环,通过config_db::set的方式设置收集到的transaction的数量pkt_num,当收集到足够数量的transaction后跳出循环:

1 | |

上述代码中将原本的fork...join语句改为了fork...join_any。当收集到足够的transaction后,第二个进程终结,从而跳出 fork…join_any,执行drop_objection语句

方案2:如在第2章中介绍的例子那样,在sequence中提起sequencer的objection,当sequence完成后,再撤销此objection

总结:以上两种方式在验证平台中都有应用。其中用得最多的是第二种,这种方式是UVM提倡的方式。UVM的设计哲学就是全部 由sequence来控制激励的生成,因此一般情况下只在sequence中控制objection

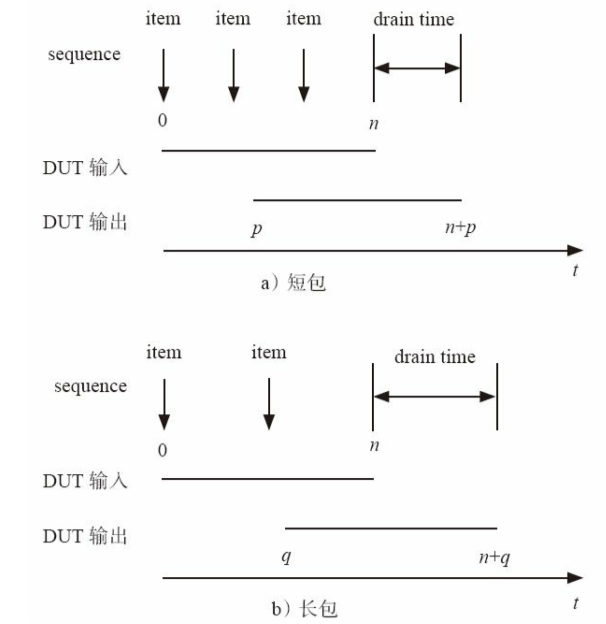

5.2.4 drain_time(撤销objection延时)

在sequence中,n时刻发送完毕最后一个transaction,如果此时立刻drop_objection,那么最后在n+p时刻DUT输出的包将无法接收到。因此,在sequence中,最后一个包发送完毕后,要延时p时间才能drop_objection

1.考虑两种实现方式

第一种,直接#(无法控制延迟时间)

1 | |

缺点:

- 随机发送激励时,延时的大小也是随机的,所以无法精确地控制延时,只能根据激励选择一个最大的延时

- 如果某一天,DUT对于同样的激励,其处理延时变大,那就要修改所有的延时大小

第二种,使用drain_time

所谓drain_time,就是所有objection被撤销后等待一段时间,在这段时间内,那些正在运行的线程依然在正常地运转,drain_time过去才进入下一phase

drain_time的设置方式为:phase.phase_done.set_drain_time

1 | |

phase_done是uvm_phase内定义的一个成员变量:

uvm_objection phase_done; // phase done objection一个phase对应一个drain_time,并不是所有的phase共享一个drain_time

在没有设置的情况下,drain_time的默认值为0

5.2.5 objection的调试

与phase的调试一样,UVM同样提供了命令行参数来进行objection的调试:

1 | |

结果如下:

1 | |

在调用raise_objection时,count=1表示此次只提起了这一个objection,下面代码是提起两个objection的结果

1 | |

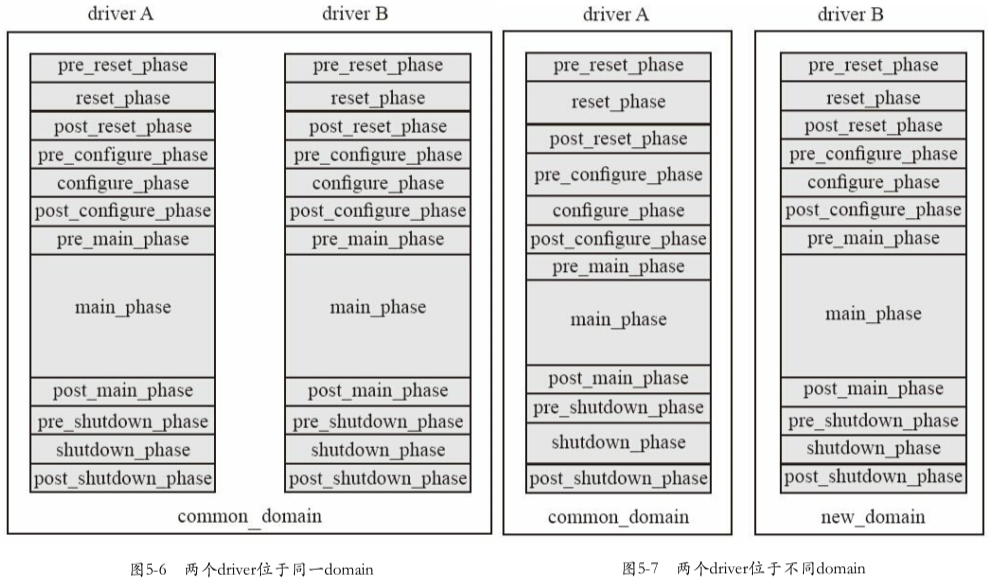

5.3 domain

5.3.1 domain简介

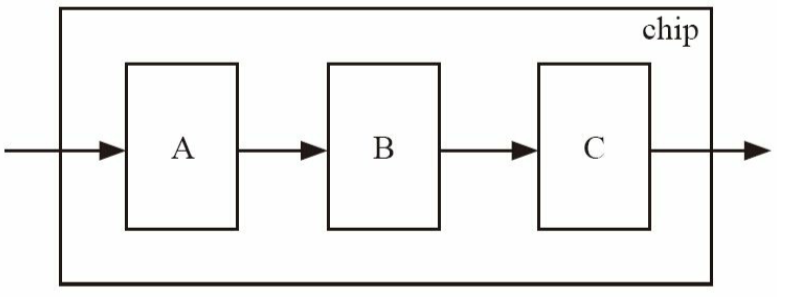

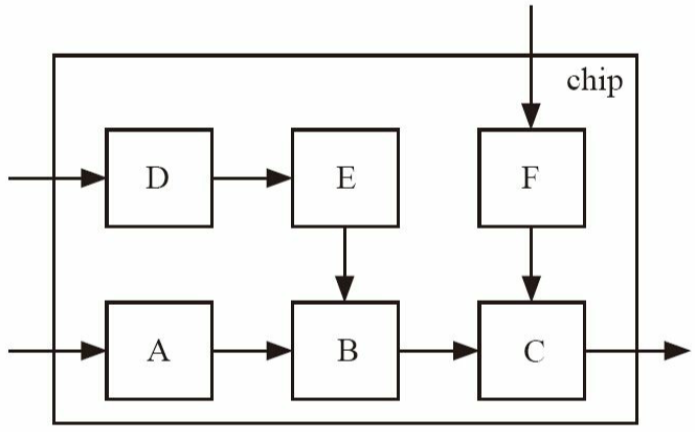

问题背景:设DUT分成两个相对独立的部分,这两个独立的部分可 以分别复位、配置、启动,但如果没有domain的概念,那么这两块独立的部分则必须同时在reset_phase复位,同时在configure_phase配置,同时进入main_phase开始正常工作。这种协同性当然是没有问题的,但是没有体现出独立性。图5-6中画出了这两个部分的driver位于同一domain的情况

解决方案,使用不同domain划分多个时钟域,这图5-7中列出了两个driver位于不同domain的情况,实现了两个driver的run-time phase异步执行

domain特性:

- 默认情况下,验证平台中所有component都位于一个名字为

common_domain的domain中 - domain只能隔离

run-time phase,无法隔离run_phase和function phase - phase的跳转只能局限在某一domain中(原文5.3.3)

5.3.2 多domain的例子

如何把某个组件置于新的domain中:

1 | |

步骤:

声明一个了一个

uvm_domain:uvm_domain new_domain;在构造函数中实例化该

uvm_domain:new_domain = new("new_domain");在

connect_phase中将该组件加入到domain中:set_domain(new_domain);

function void uvm_component::set_domain(uvm_domain domain, int hier=1);

- 第二个参数表示是否递归调用,如果为1,则

domain及其子节点都将全部加入到该domain中。由于子节点的实例化一般在build_phase中完成,所以这里一般在connect_phase中调用set_domain

2022-12-02 15:45:38

第六章 UVM中的sequence :seedling:

6.1 sequence基础

6.1.1 激励产生(从driver中剥离激励产生功能)

为什么激励最初产生在driver中,后来产生在sequence中?

- 原因:如果要修改激励,则需要将driver.main_phase重新写了一遍,可扩展性太差

分析后发现main_phase代码只有中间的改变了,那为什么不定义一个gen_pkt用于专门产生激励的函数来替代这段代码?

- 原因1:如果直接定义两个

gen_pkt则不符合sv,造成重复定义 - 原因2:如果使用虚函数,则需要定义新的子类

driver,重载gen_pkt函数,更麻烦了

为解决上面的问题,UVM引入了sequence机制,在解决的过程中还使用了factory机制、config机制,具体来讲:使用sequence机制之后,在不同的测试用例中,将不同的sequence设置成sequencer的main_phase的default_sequence。当sequencer执行到main_phase时,发现有default_sequence,那么它就启动sequence

sequence机制和TLM的区别?

- sequence机制描述的是,sequence、sequencer、agent、driver之间的关系

- TLM描述的是其他组件之间的事务级连接

sequence机制如何实现的?猜测resource_db机制

resource_db机制与config_db机制的底层实现是一样的,uvm_config_db类就是从uvm_resource_db类派生而来的。在寄存器模型的sequence中,get操作是通过resource_db来进行的(详见7.6.2)

6.1.2 sequence机制回顾

sequence的实例化有两种方式:

- 手动调用

seq::start(sqr)函数 - 使用

default_sequence

执行逻辑:

body:

- 每一个sequence都有

pre_body、body、post_body任务 - 当一个sequence启动后会自动执行sequence的

pre_body、body、post_body任务 - 作用:

- 发送transcation(

`uvm_do,`uvm_send…) - 控制objection机制

- 发送transcation(

sequence机制参考实现步骤(2.4.3):

- sqr定义(只用简单注册一下sqr到factory,其他不用实现)

- sqr实例化(在agent中例化sqr,drv,mon)

- seq定义(主要定义

body()函数,并在该函数内调用`uvm_do用来发送激励)- seq的实例化(两种方案:手动

new;或者在使用default_sequence是参数四指定为case0_sequence::type_id::get()形式- seq启动(在case/env中启动,有两种方案:手动

seq.start(sqr)或default_sequence)- 连接driver与sqr(在agent中连接,使用继承自UVM各自组件的端口,代码:

drv.seq_item_port.connect(sqr.seq_item_export))- drv申请item(在driver的

main_phase向sqr申请数据,使用到seq_item_port.get_next_item(req);和seq_item_port.item_done();

item_done还可以用来返回response(6.7.1)

default_sequence如何使用:调用uvm_config_db

1 | |

方式总结

方式①:手动实例化+手动启动(在case中直接定义)

1 | |

方式②:工厂实例化+手动启动(在vseq中定义,vseq在case中使用default_sequence自动实例化)

1 | |

方式③:手动实例化 + default_sequence(seq实例,如某seq)

这样做的好处就是,既可以利用default_sequence,又可以配置sequence_library_cfg省去繁杂的配置(6.8.4)

1 | |

方式④:直接default_sequence(seq类的id,如case0_sequence::type_id::get())

1 | |

default_sequence做了什么?

① 在uvm_sequence这个基类中,有一个变量名为starting_phase,它的类型是uvm_phase,sequencer在启动default_sequence时,会执行如下代码,实现在sequence中使用starting_phase进行提起和撤销objection:

2seq.starting_phase = phase;

seq.start(this);

6.2 sequence的仲裁机制

6.2.1 在同一sequencer上启动多个sequence

1.如何定义

定义两个sequence,运行后会显示两个sequence交替产生transaction

1 | |

2.优先级

sequencer根据什么选择使用哪个sequence的transaction呢?

依据创建的transaction的优先级、sequencer的仲裁算法、sequence的优先级,优先级越高越容易选中

- 使用

`uvm_do(SEQ_OR_ITEM) 或 `uvm_do_with(SEQ_OR_ITEM, CONSTRAINTS)宏时创建的seq默认优先级为-1- 默认sqr的仲裁算法为

SEQ_ARB_FIFO,它会严格遵循先入先出的顺序,而不会考虑优先级- seq时启动时可以指定seq的优先级:

seq.start(sqr, null, pri);改变transaction优先级

可以通过

`uvm_do_pri(SEQ_OR_ITEM, PRIORITY) 或 `uvm_do_pri_with(SEQ_OR_ITEM, PRIORITY, CONSTRAINTS)改变所产生的transaction的优先级,其中形参pri必须≥-1,代码示例如下:

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43class sequence0 extends uvm_sequence #(my_transaction);

my_transaction m_trans;

function new(string name= "sequence0");

super.new(name);

endfunction

virtual task body();

if(starting_phase != null)

starting_phase.raise_objection(this);

repeat (5) begin

`uvm_do_pri(m_trans, 100)

`uvm_info("sequence0", "send one transaction", UVM_MEDIUM)

end

#100;

if(starting_phase != null)

starting_phase.drop_objection(this);

endtask

`uvm_object_utils(sequence0)

endclass

class sequence1 extends uvm_sequence #(my_transaction);

my_transaction m_trans;

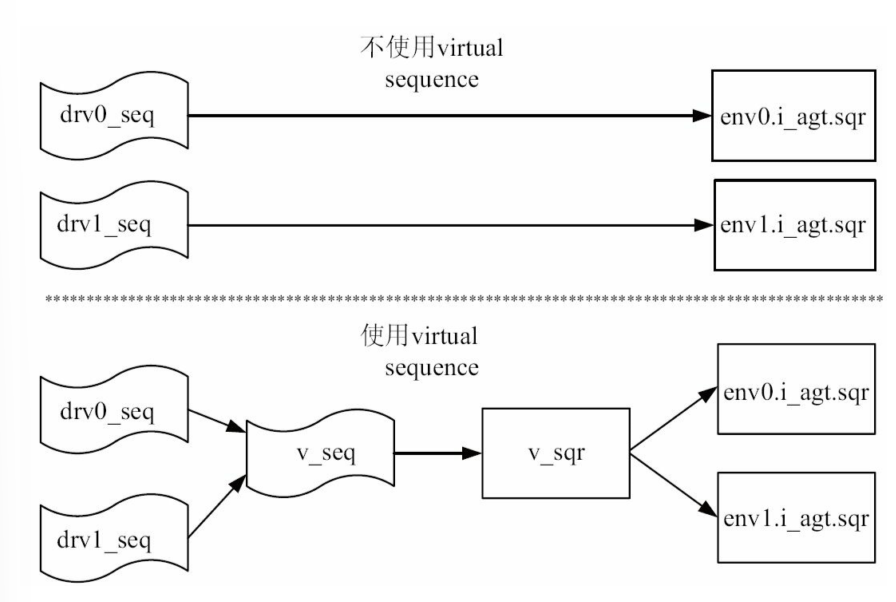

function new(string name= "sequence1");