AXI4.0 初步学习

参考资料

手册

一个介绍指南

该指南概述了与 AMBA AXI 相关的主要主题,包括不同通道和信号的使用和操作。当您通过阅读AMBA AXI 和 ACE 协议规范了解更多有关 AMBA AXI 的信息时,这些知识将很有用。您可以将您的知识付诸实践,以开发实现 AMBA AXI 协议的接口

手册的下载地址

AMBA协议簇不同协议汇总

AXI基础七讲

AXI Basics 2 - Simulating AXI interfaces with the AXI Verification IP (AXI VIP)

- AXI Basics 4 - Using the AXI VIP as protocol checker for an AXI4 Master interface

- AXI Basics 5 - Create an AXI4-Lite Sniffer IP to use in Xilinx Vivado IP Integrator

- AXI Basics 6 - Introduction to AXI4-Lite in Vitis HLS

- AXI Basics 7 - Connecting to the PS using AXI4-Lite and Vitis HLS

AXI基础七讲(中文版)

主要内容

1 AXI3与AXI4之间的区别是什么?

- AXI3只支持多达16拍的burst 。而AXI4支持高达256拍的burst 。

- AXI3支持write interleave。AXI4不支持write interleave

- AXI3支持locked 传输,AXI4不支持locked传输

- AXI4支持QoS,AXI3不支持QoS

2 AXI4-Lite详解

2.1 AXI4-Lite特性

AXI4-Lite是AXI4协议的精简版,它适用于不需要AXI4完整功能的简单控制寄存器样式的接口

相较AXI4,AXI4-Lite协议的特点是:

- 所有读写交易的突发长度均为1

- 仅支持32位或64位的数据总线宽度

- 所有访问都是不可修改的,不可缓冲的

- 不支持独占访问

2.2 AXI4-Lite接口信号

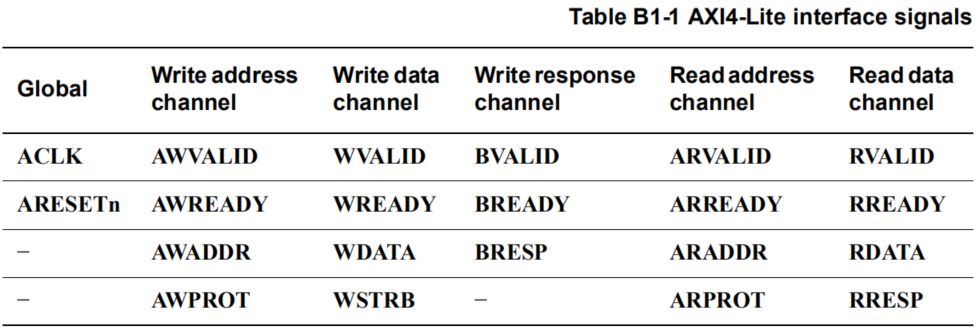

AXI4-Lite协议信号较AXI4少了很多,具体信号如下:

1)全局信号

| 信号 | 源 | 描述 |

|---|---|---|

| ACLK | 时钟源 | 全局时钟信号,所有输入信号均在ACLK上升沿采样,所有输出信号的更改只能在ACLK上升沿之后。主从接口上的所有输入和输出信号间不允许有组合路径同AXI4 |

| ARESETn | 复位源 | 全局复位信号,为异步复位同步置位信号,即ARESETn在任意时刻变为低电平可立刻生效,但置位为1时只能在ACLK的下一个上升沿生效同AXI4 |

2)写地址通道

| 信号 | 源 | 位宽 | 默认值 | 描述 |

|---|---|---|---|---|

| AWID(可选,仅但主机是AXI4而从机是AXI-Lite时需要此信号) | - | - | - | 当需要和主机的AXI4协议互联时,从机的AXI-Lite协议增加此信号 |

| AWADDR | 主 | 可变,协议未定义位宽, Xilinx使用12, 13, … 64,一般为32/64 | - | 要写入数据的内存地址同AXI4 |

| AWPORT | 主 | 3 | - | 写事务的保护属性:特权,安全级别和访问类型提供用于禁止非法传输事务的访问权限信号同AXI4 |

| AWVALID | 主 | 1 | - | - |

| AWREADY | 从 | 1 | - | - |

AxPORT

- AxPORT共3位,每一位的值代表不同的意义。一般可设置为3’b000,表示非特权且安全的数据访问

| AxPROT | 值 | 功能 | 描述 |

|---|---|---|---|

| [0] | 0 | Unprivileged access 非特权访问 | AXI主站可能支持多个级别的操作特权,并将这种特权概念扩展到内存访问。 AxPROT [0]将访问标识为非特权或特权 |

| [0] | 1 | Privileged access 特权访问 | - |

| [1] | 0 | Secure access 安全访问 | AXI主站可能支持安全和非安全操作状态,并将这种安全性概念扩展到内存访问。 AxPROT [1]将访问标识为安全或不安全。 AxPROT [1]可以视为定义了两个地址空间,一个安全地址空间和一个非安全地址空间。该信号可被视为附加地址位。安全和非安全地址空间之间的任何别名都必须正确处理。 |

| [1] | 1 | Non-secure access 非安全访问 | - |

| [2] | 0 | Data access 数据访问 | 该位指示事务是指令访问还是数据访问。 AXI协议将此指示定义为提示。并非在所有情况下都是准确的,例如,当事务包含指令和数据项的混合时。本规范建议主机将AxPROT [2]设置为LOW,以指示数据访问,除非已知该访问是指令访问。 |

| [2] | 1 | Instruction access 指令访问 | - |

3)写数据通道

| 信号 | 源 | 位宽 | 默认值 | 描述 |

|---|---|---|---|---|

| WDATA | 主 | 32/64 | - | 要写入的数据,大部分数据总线为32位。32位主机可访问64位丛机,通常使用64位中的低32位作为有效位宽 |

| WSTRB | 主 | 4/8 | 全0 | 写选通,指示哪些字节通道保存有效数据WSTRB为高表示数据总线的哪一/几字节是有效数据,具体的WSTRB [n]为高对应于WDATA [(8n+7:8n]这一字节的数据有效4位对应32位总线,8位对应64位总线 |

| WVALID | 主 | 1 | - | - |

| WREADY | 从 | 1 | - | - |

WSTRB

- AXI4-Lite协议支持写选通。这意味着可以实现多尺寸寄存器,如8位/16位寄存器

- 所有的主机接口和与主机互联的元件都必须支持写选通,而从机被允许:

- 充分利用写选通信号

- 忽略写选通信号并将所有写访问视为整个数据总线宽度(我的理解:无论写选通信号是多少,都将数据总线上的所有位视为有效位)

- 检测不支持的写选通信号并提供错误响应,如一个32位从机仅支持低8位写选通,如果WSTRB为4‘b1000表示高8位写选通,则此时从机不支持并报错。

- 特殊的:提供内存访问的从站必须完全支持写选通。存储器映射中的其他从机可能支持更有限的写选通选项。

4)写响应通道

| 信号 | 源 | 位宽 | 默认值 | 描述 |

|---|---|---|---|---|

| BID可选,仅但主机是AXI4而从机是AXI-Lite时需要此信号) | 从 | - | - | 从机接收到AWID,写响应返回BID,主机的AXI4协议需要BID才能识别从机的写响应 |

| BRESP | 从 | 2 | 2‘b00 | 写响应,指示写事务状态2’b00 OKAY 正常访问成功2’b01 EXOKAY 无意义,在AXI4中表示独占访问成功,但AXI4-Lite不支持独占访问2‘b10 SLVERR 从机反映错误2’b11 DECERR 互连模块无法成功解码从属访问 |

| BVALID | 从 | 1 | - | - |

| BREADY | 主 | 1 | - | - |

5)读地址通道

| 信号 | 源 | 位宽 | 默认值 | 描述 |

|---|---|---|---|---|

| ARID(可选,仅但主机是AXI4而从机是AXI-Lite时需要此信号) | 主 | - | - | 接收主机AXI4协议的ARID |

| ARADDR | 主 | 可变,协议未定义位宽, Xilinx使用12, 13, … 64,一般为32/64 | - | 要读取的内存地址同AXI4 |

| ARRPOT | 主 | 3 | - | 写事务的保护属性:特权,安全级别和访问类型提供用于禁止非法传输事务的访问权限信号,同AWRPOT同AXI4 |

| ARVALID | 主 | 1 | - | - |

| ARREADY | 从 | 1 | - | - |

6)读数据通道

| 信号 | 源 | 位宽 | 默认值 | 描述 |

|---|---|---|---|---|

| RID(可选,仅但主机是AXI4而从机是AXI-Lite时需要此信号) | 从 | - | - | 从机接收到ARID,读数据返回RID,主机的AXI4协议需要RID才能识别从机的读数据 |

| RDATA | 从 | 32/64 | - | 读数据 |

| RRESP | 从 | 2 | 2‘b00 | 读响应,指示读事务状态,同BRESP同AXI4 |

| RVALID | 从 | 1 | - | - |

| RREADY | 主 | 1 | - | - |

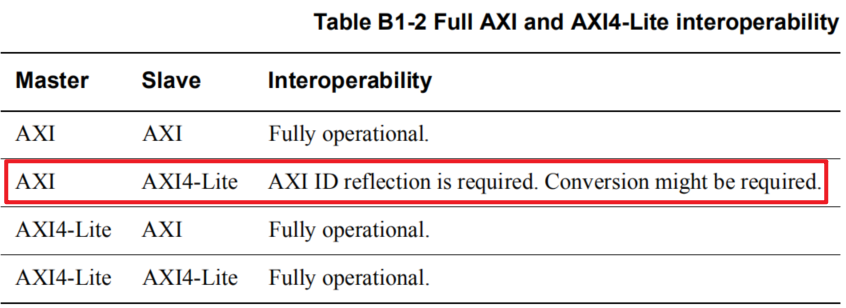

2.3 AXI4与AXI4-Lite的互联

AXI4协议和AXI4-Lite是可以互联的,唯一需要注意的是当主机是AXI4且从机是AXI4-Lite时,从机的AXI4-Lite协议需增加AXI ID信号以匹配主机的AXI ID

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!