AMBA2.0学习

1 AMBA总线概述

系统总线简介

- 系统芯片中各个模块之间需要有接口来连接

- 总线作为子系统之间共享的通信链路

- 优点:低成本方便易用

- 缺点:会造成件能瓶颈

- 补充:AXI4.0提高了数据传输率(读信号写信号分为了5个channel)

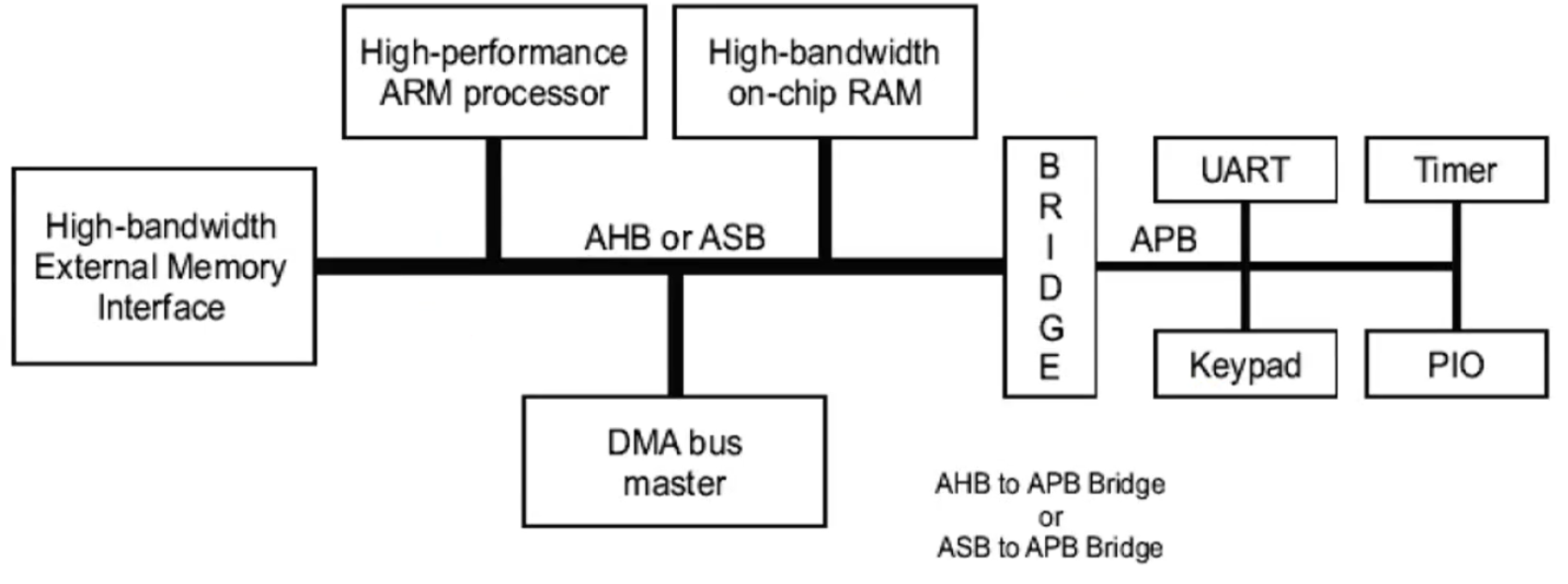

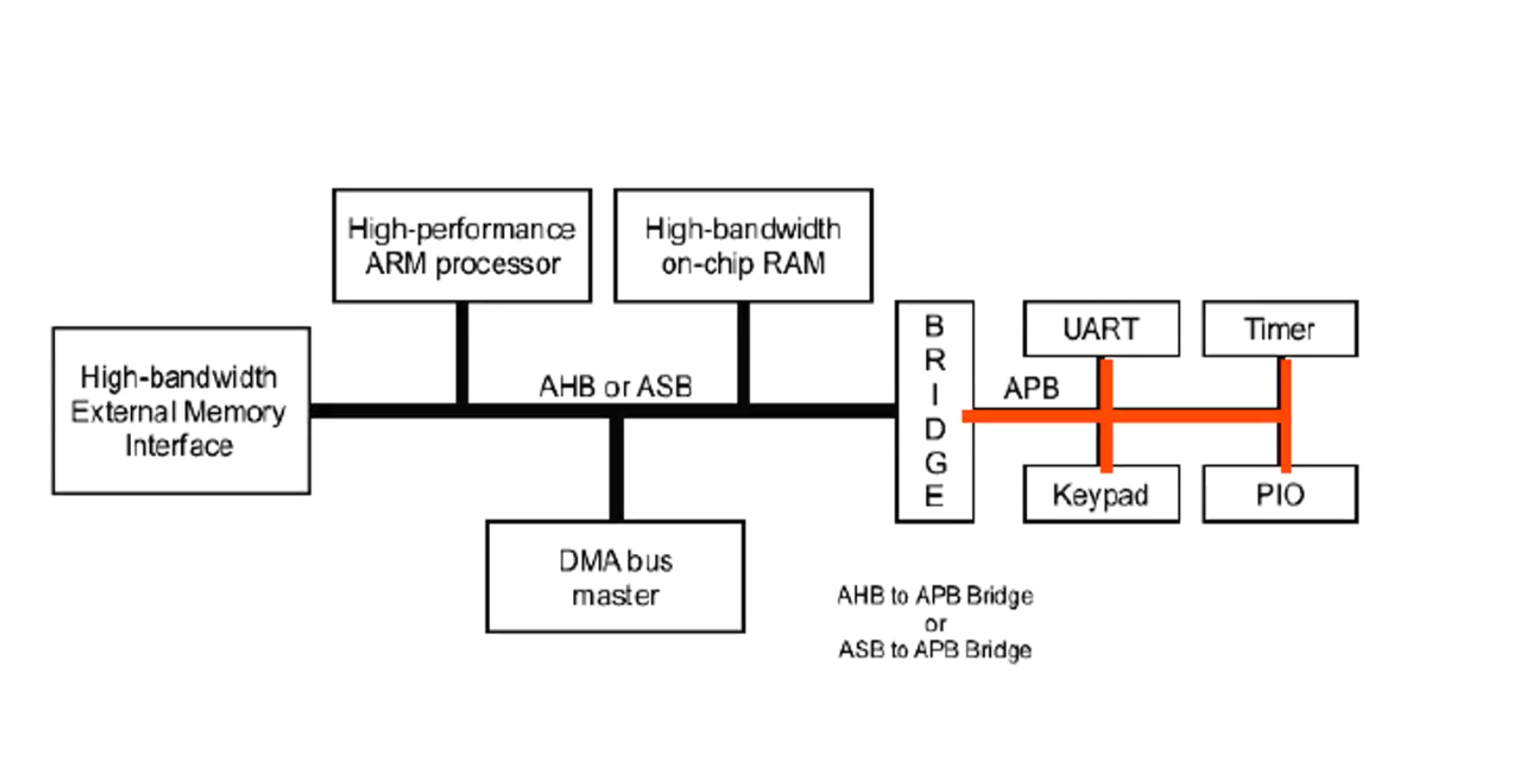

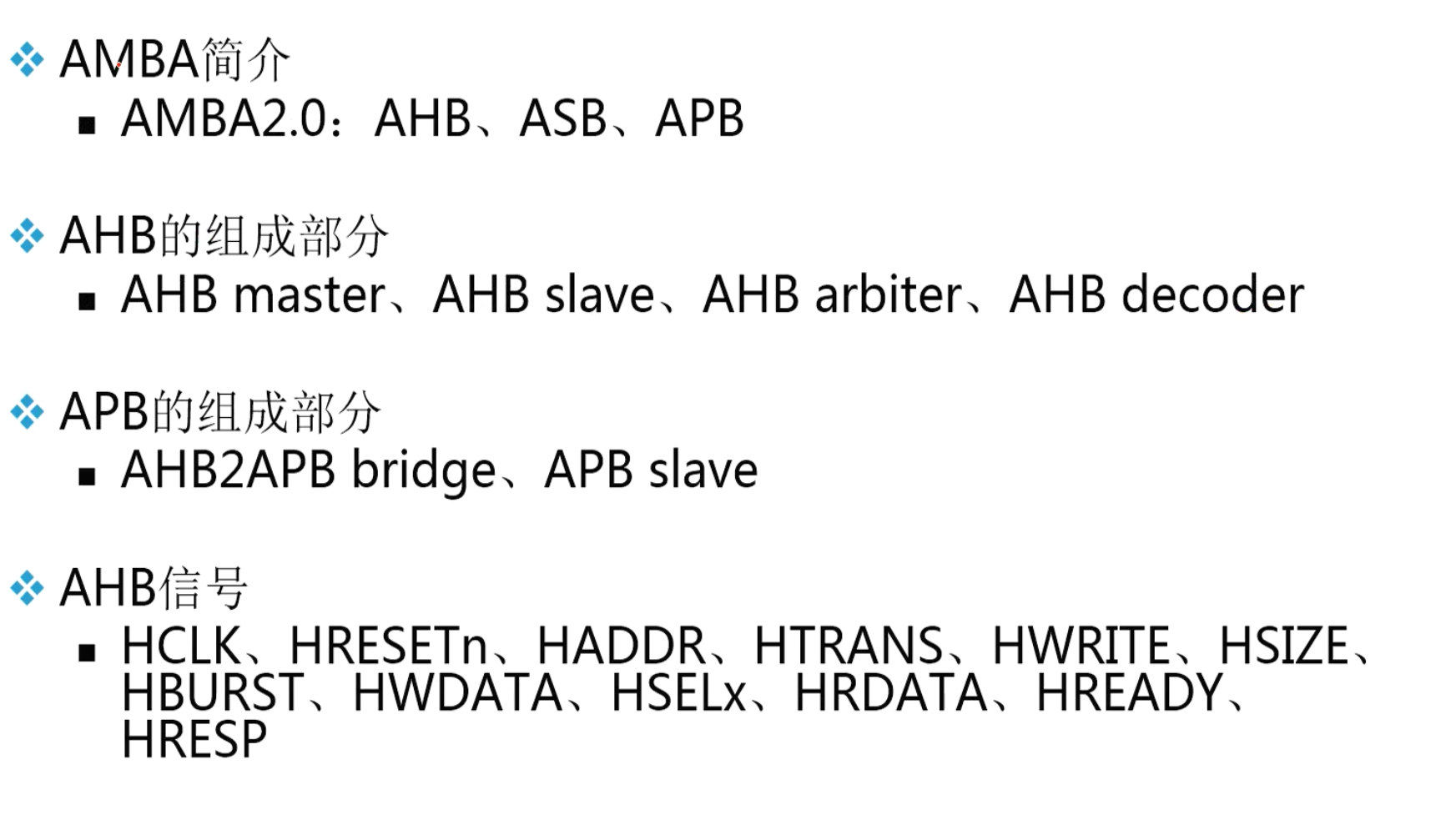

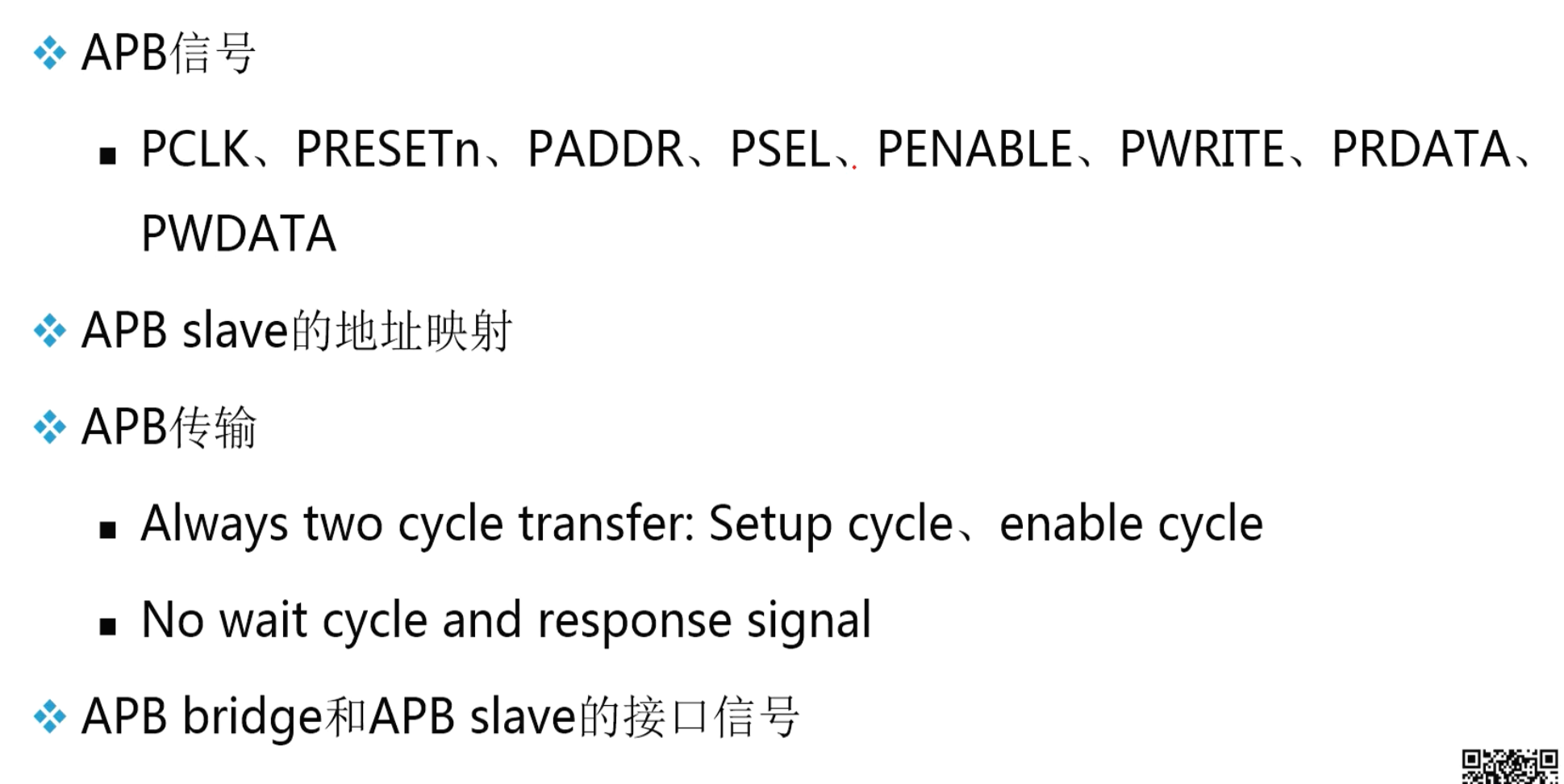

AMBA2.0

Advanced Microcontroller Bus Architecture

- 片上总线的标准

定义了三种总线

- AHB (Advanced High-performance Bus) 主要学习

- ASB (Advanced System Bus) 很少人用

- APB (Advanced Peripheral Bus) 主要学习

发展历史

AMBA 1.0

- ASB和APB

AMBA2.0

- AHB,ASB和APB

AMBA3.0

- AMBA Advanced eXtensible Interface (AXI)

AMBA4.0

- ….

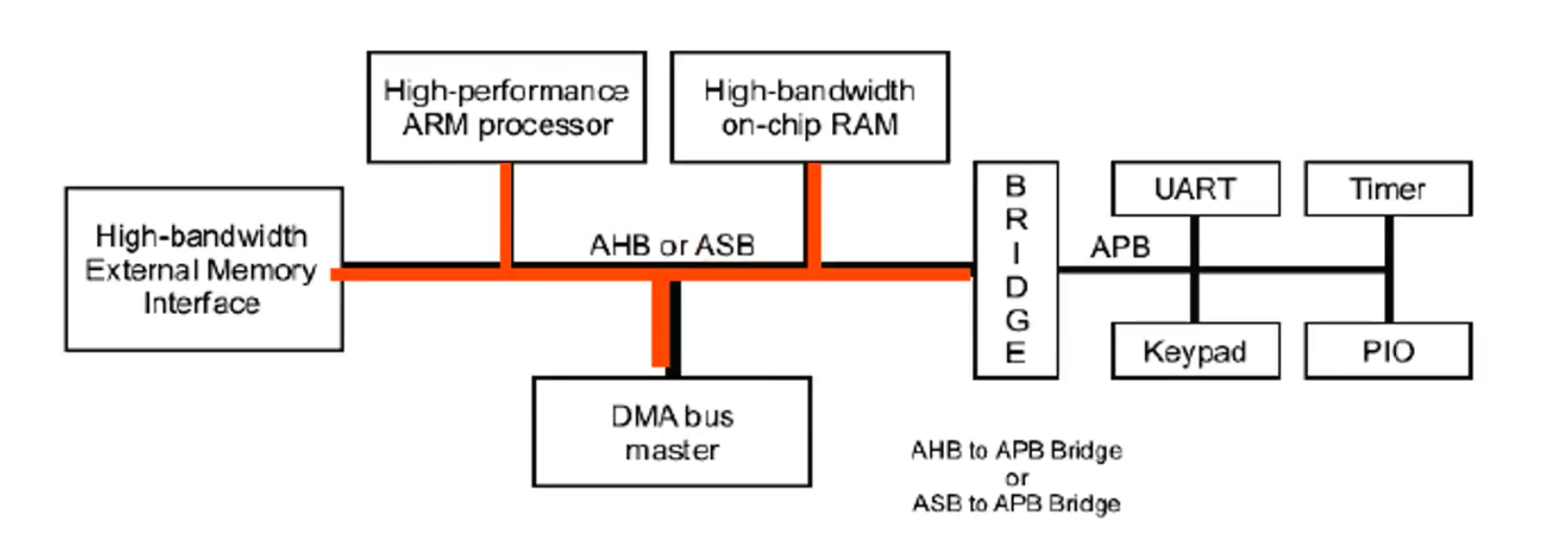

一个典型的AMBA系统

注:处理器和其它主设备/从设备都是可以替换的

特性feature

AHB

- 高速总线,高性能

- 2及流水线操作(一个地址周期,一个数据周期)

- 可支持多个总线主设备最多16个

- 支持burst传输

- burst传输是传一串数据

- 总线带宽:8、 16、32、64、128bits

- 上升沿触发操作

- 对于一个新设计建议使用AHB

ASB

- 高速总线

- 流水线澡作

- 支持多个总线主设备

- 支持burst专输

- 总线带宽: 8、 16、 32bits

- 三态、双向总线

- (不适于做DFT)

- 下降沿或者上升沿触发

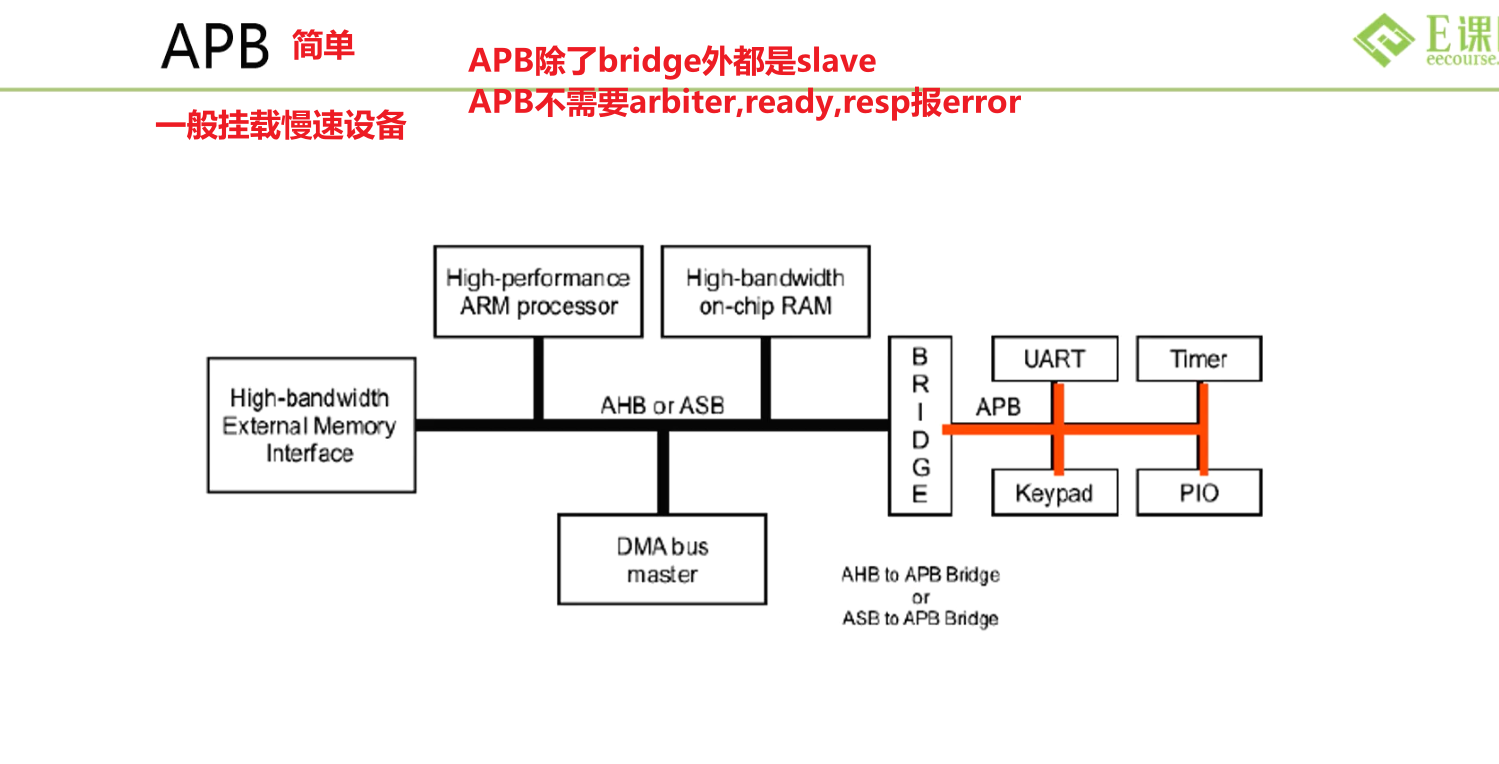

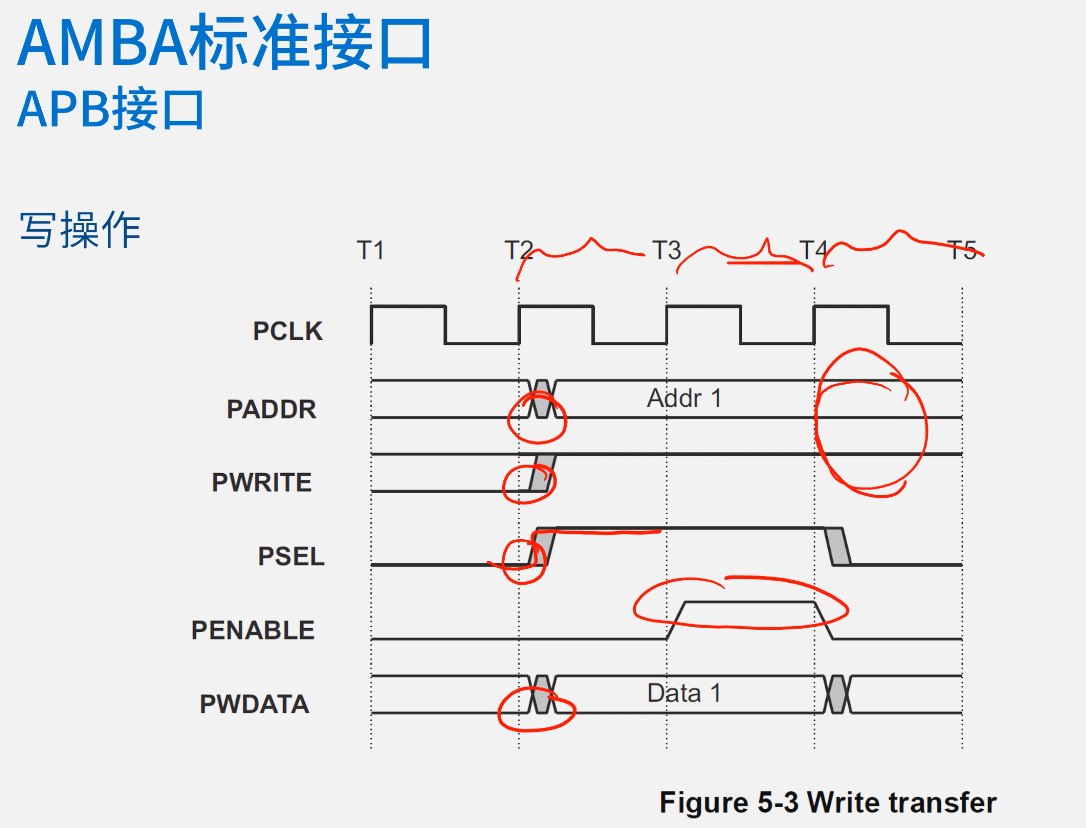

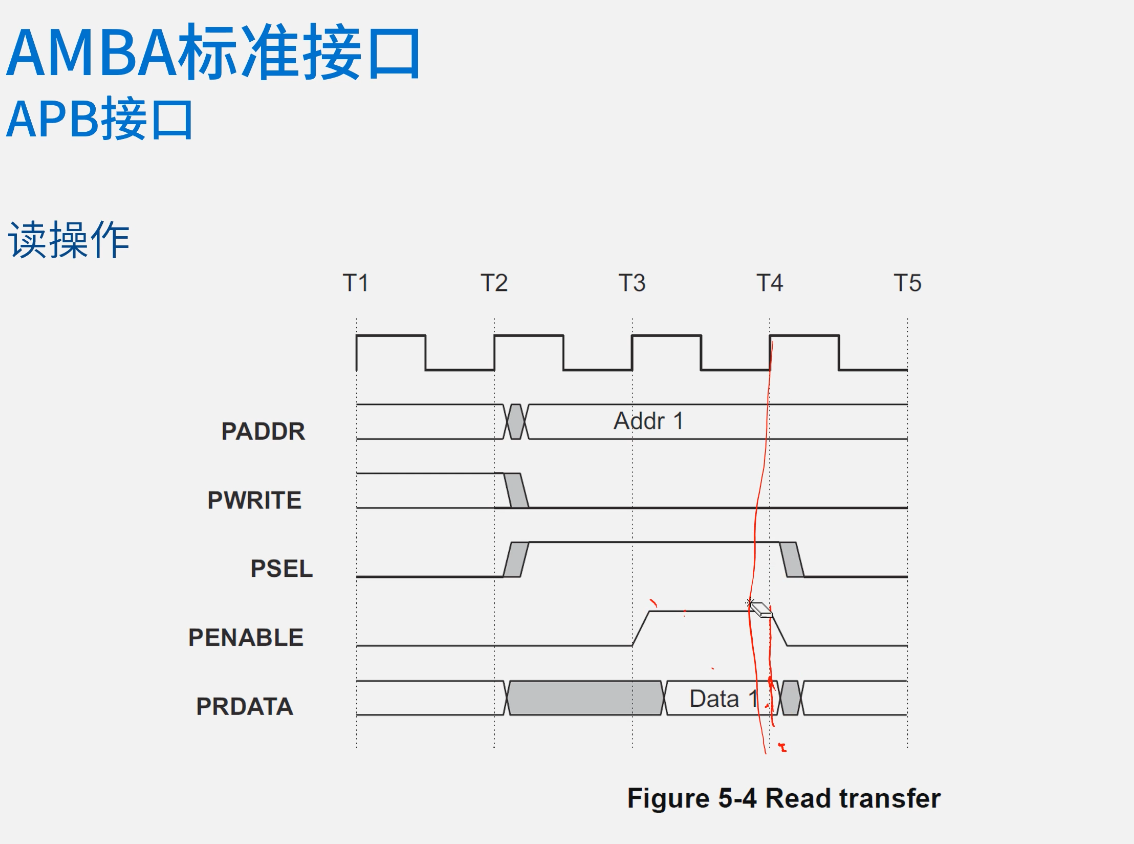

APB

- 低速总线、低功耗(功耗大部分来自门的翻转)

- 接口简单

- 在Bridge中锁存地址信号和控制信号

- 适用于多种外设

- 上升沿触发

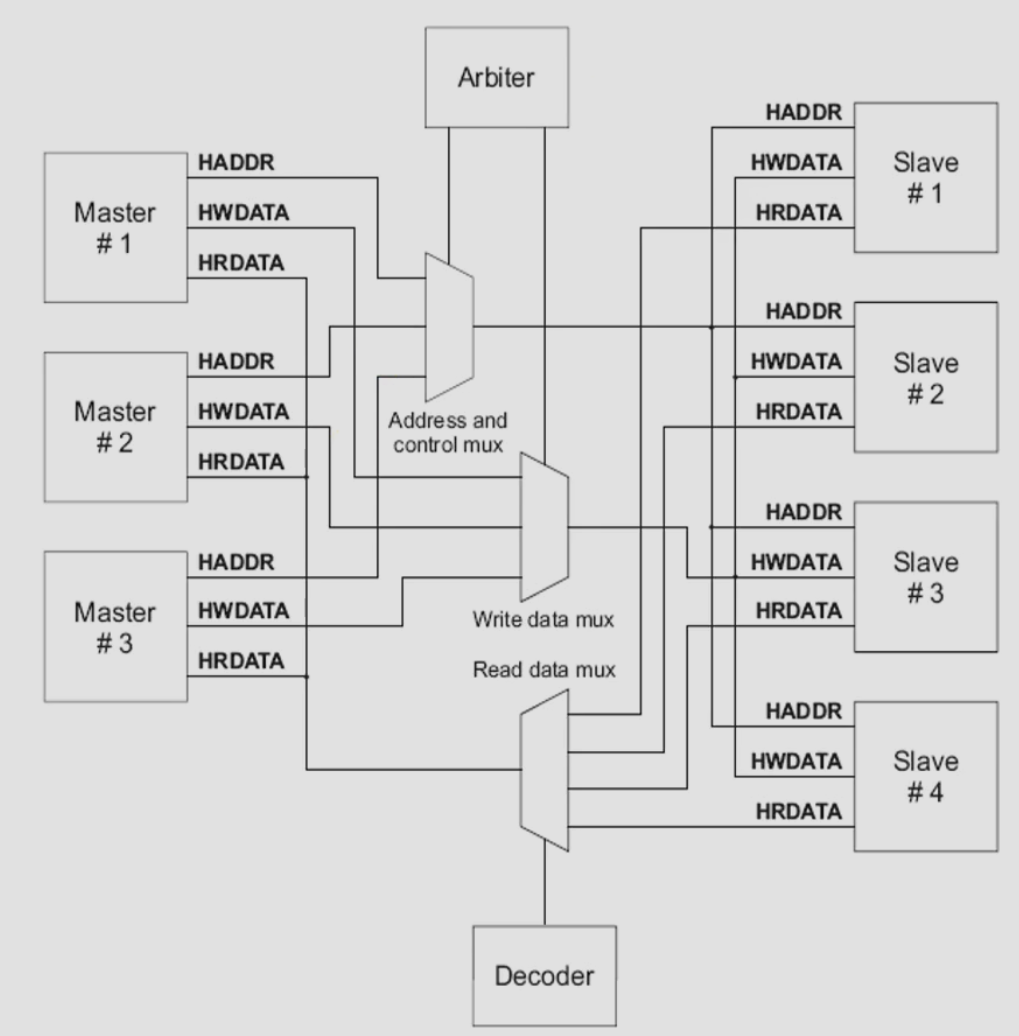

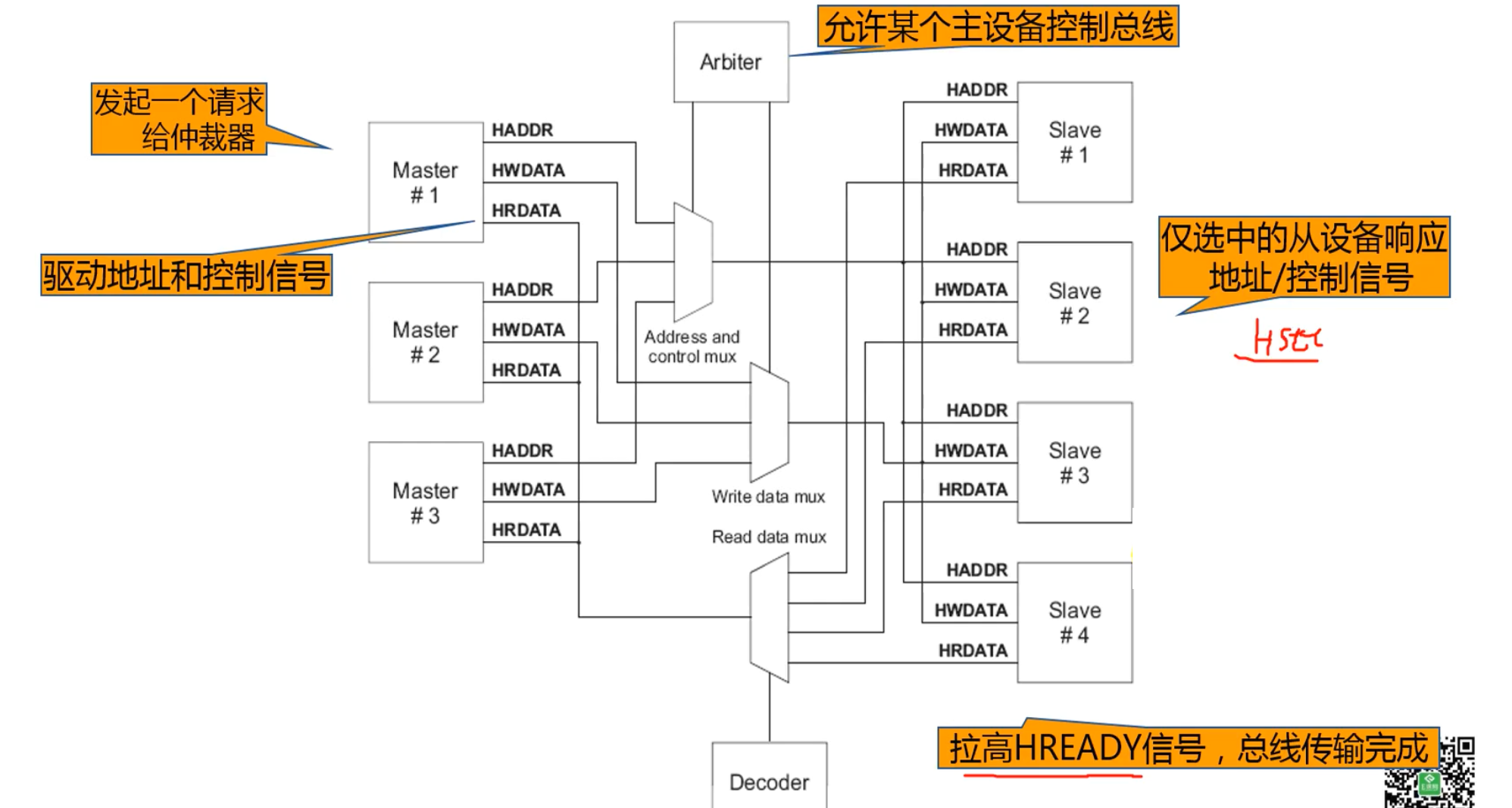

AHB的组成部分

- AHB 主设备(master)

- 初始化一次读/写操作

- 某一时刻只允许一个主设备使用总线

- CPU、DMA(可m可s)、DSP、LCDC(显示器控制器)

- AHB从设备(slave)

- 响应一次读/写操作

- 通过地址映射来选择使用哪一个从设备

- 外部存储器控制器EMI、 APB bridge

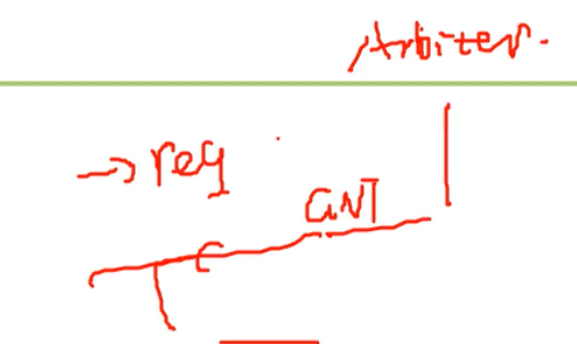

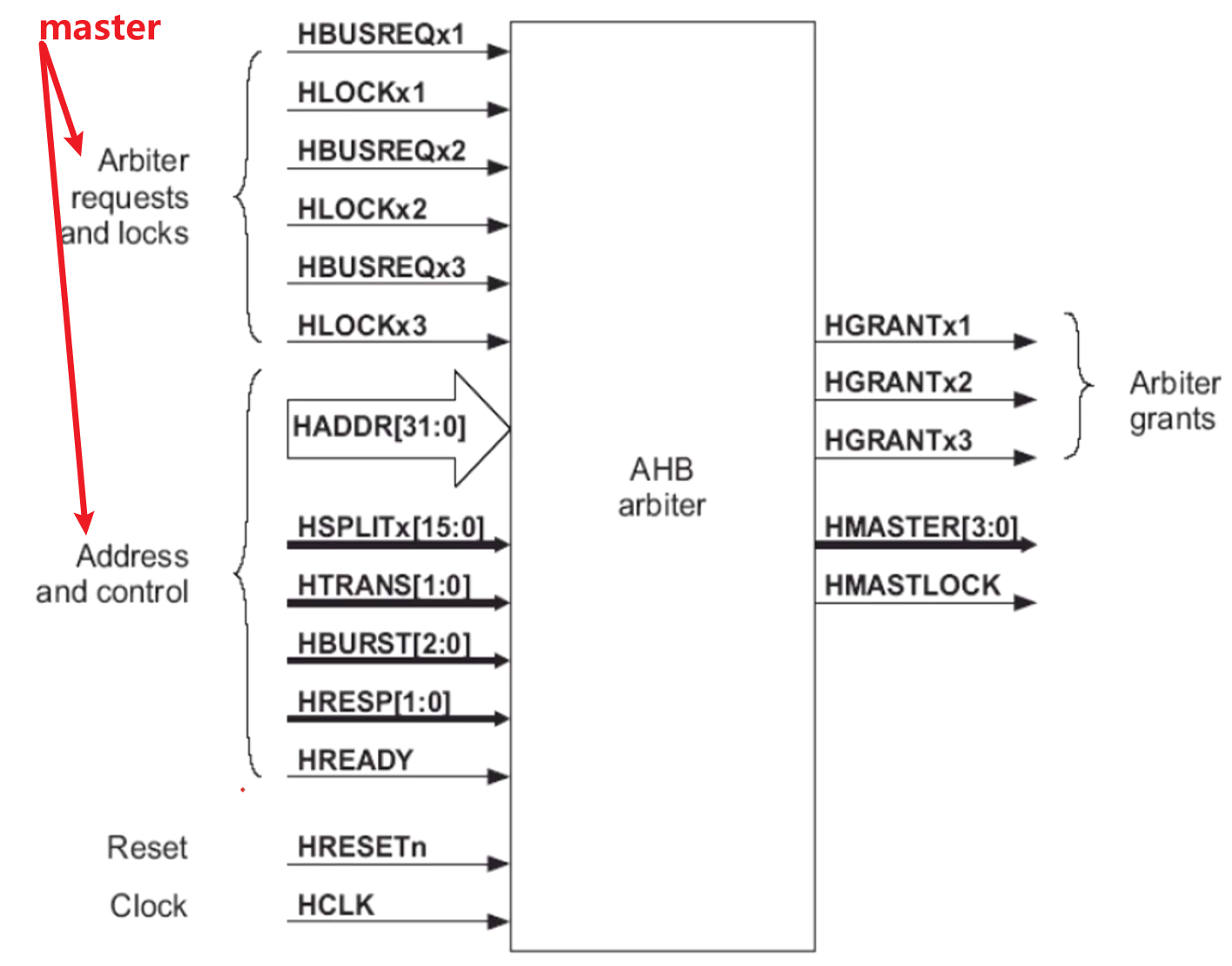

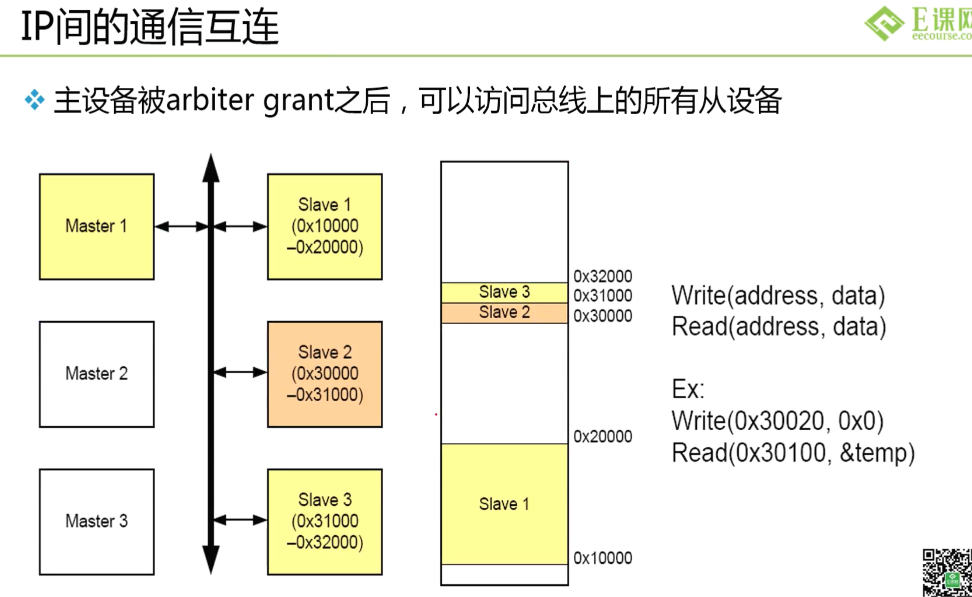

- AHB仲裁器(arbiter)

- 允许某一个主设备控制总线

- 在AMBA协议中没有定义仲裁算法,需要由我们实现人自己设计

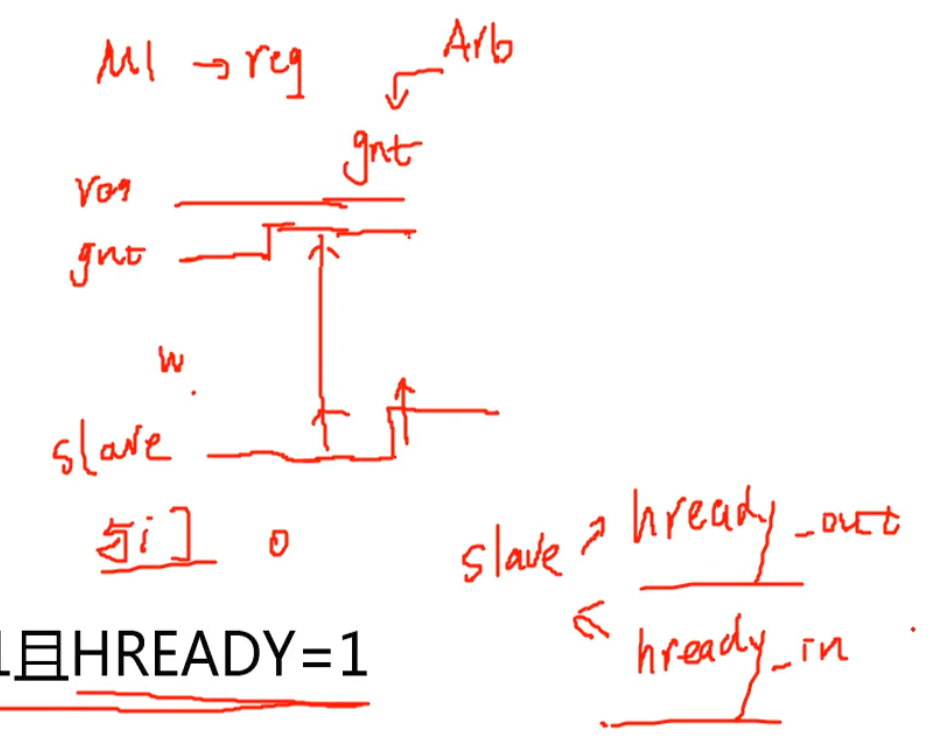

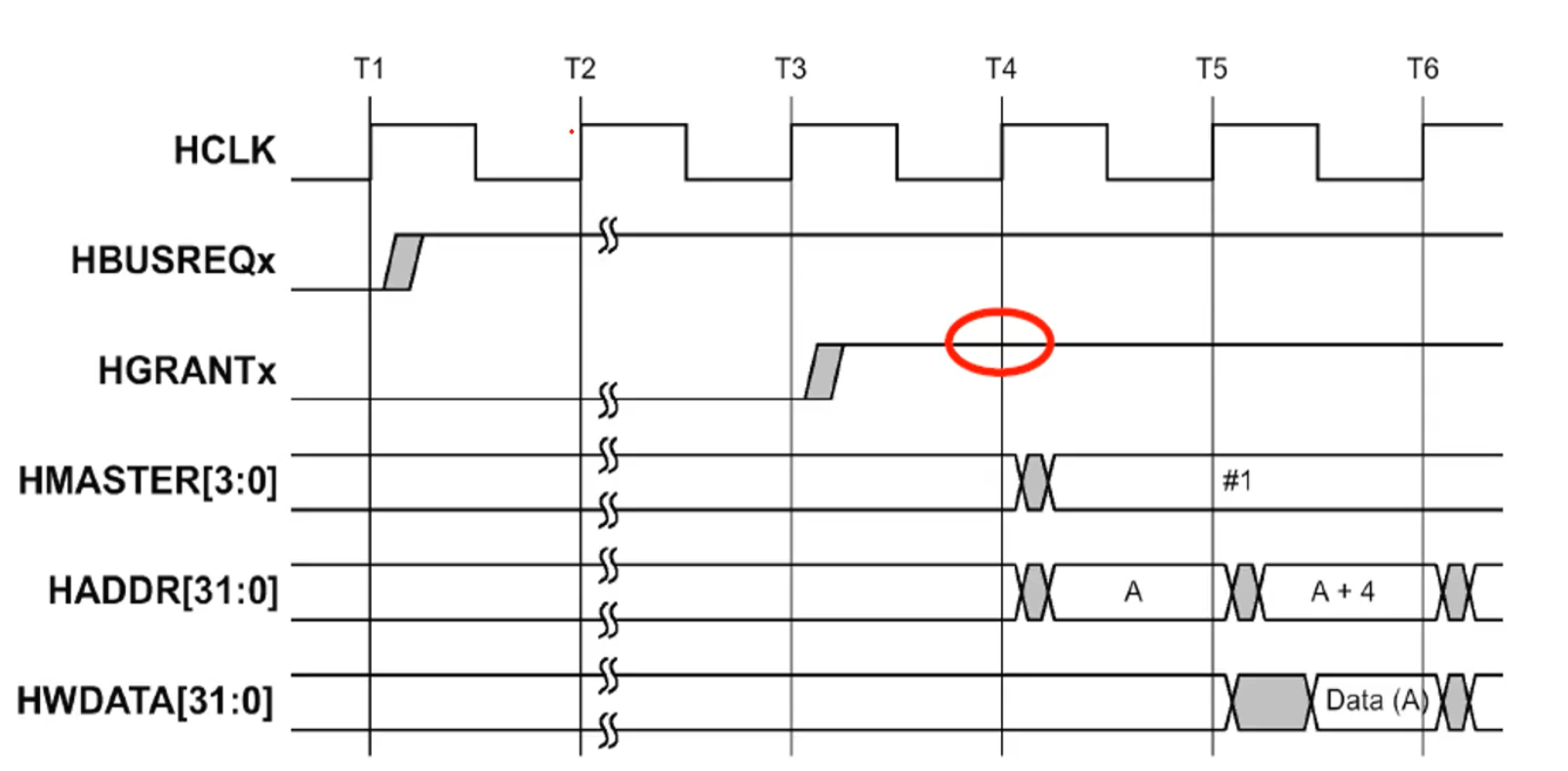

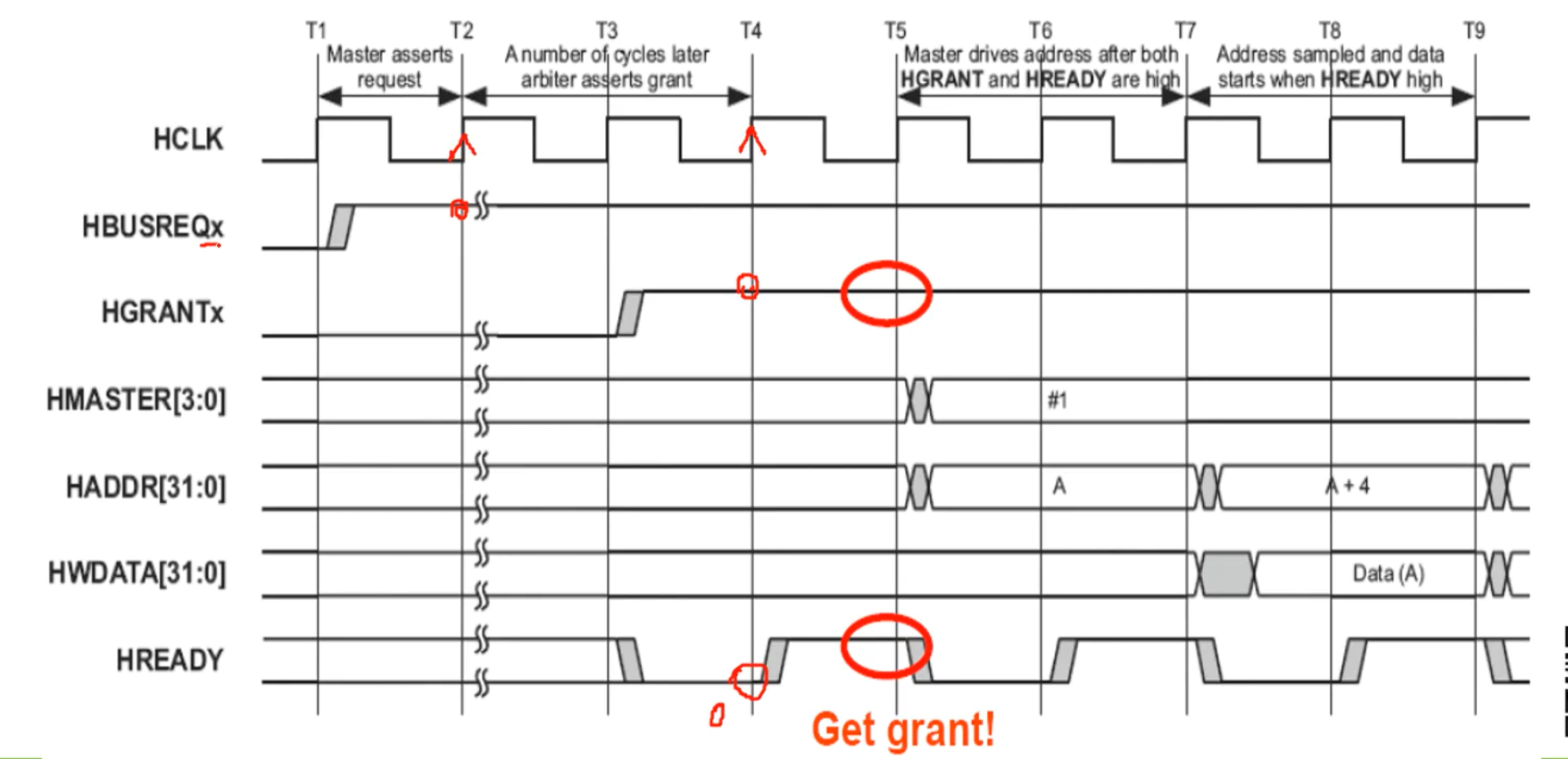

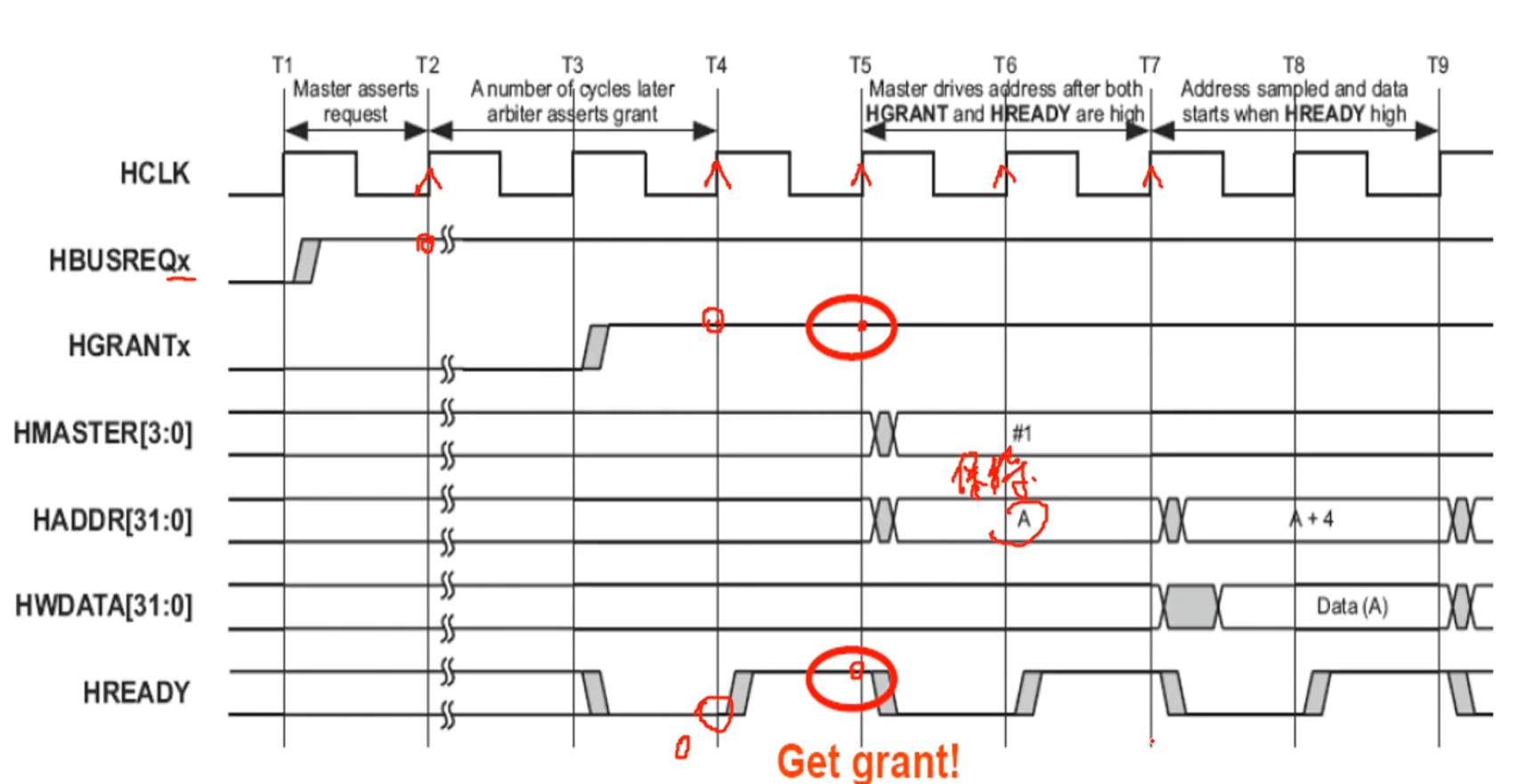

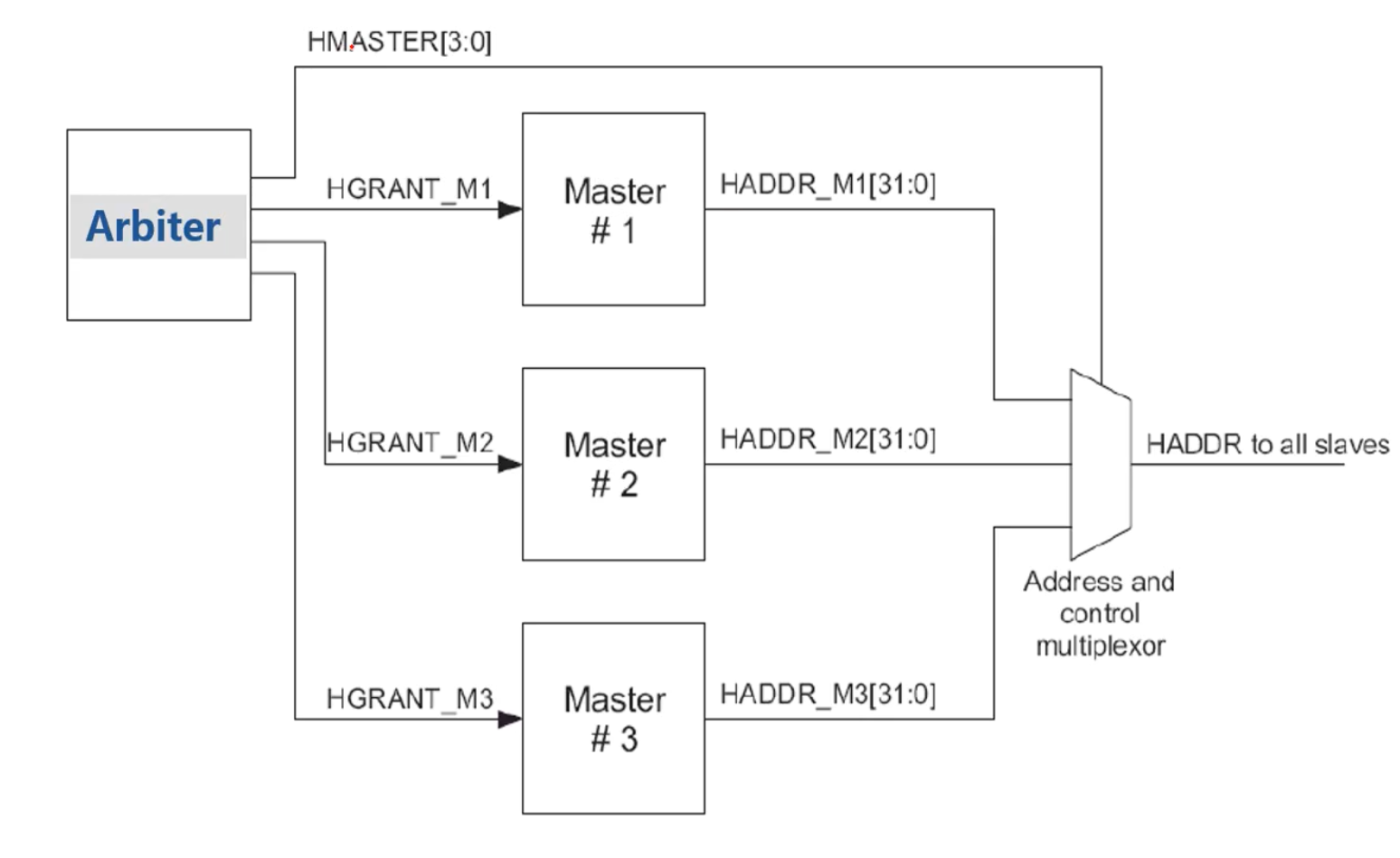

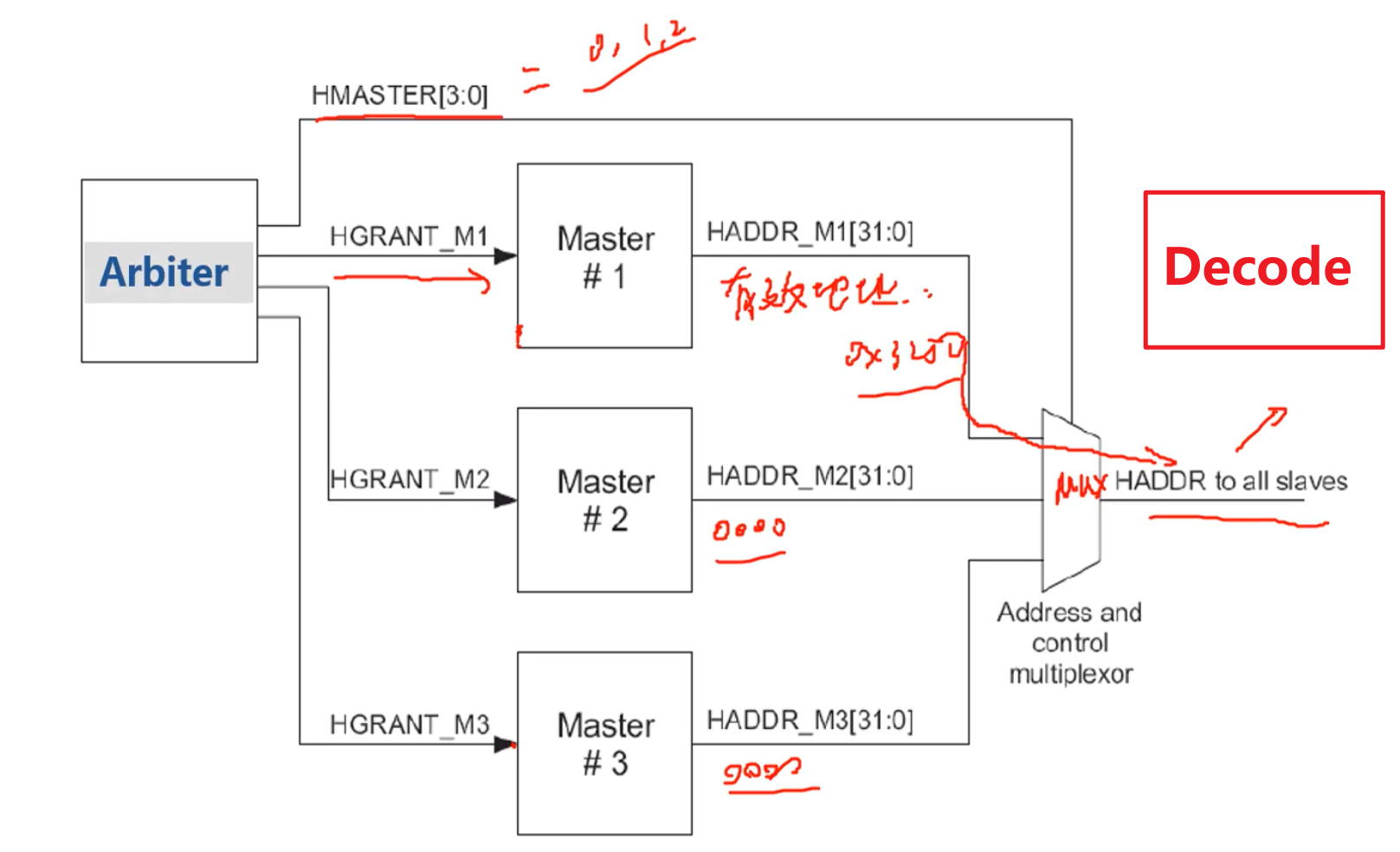

- master req来请求总线,arbiter返回GNT来相应请求,如下图

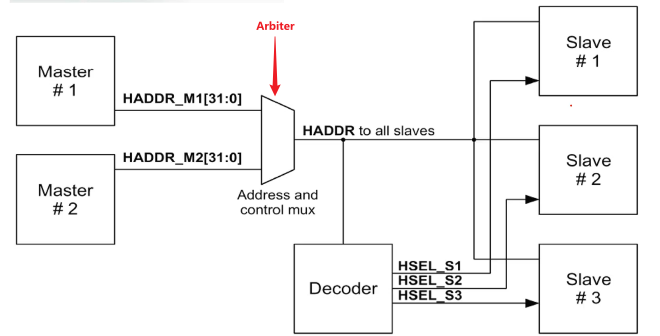

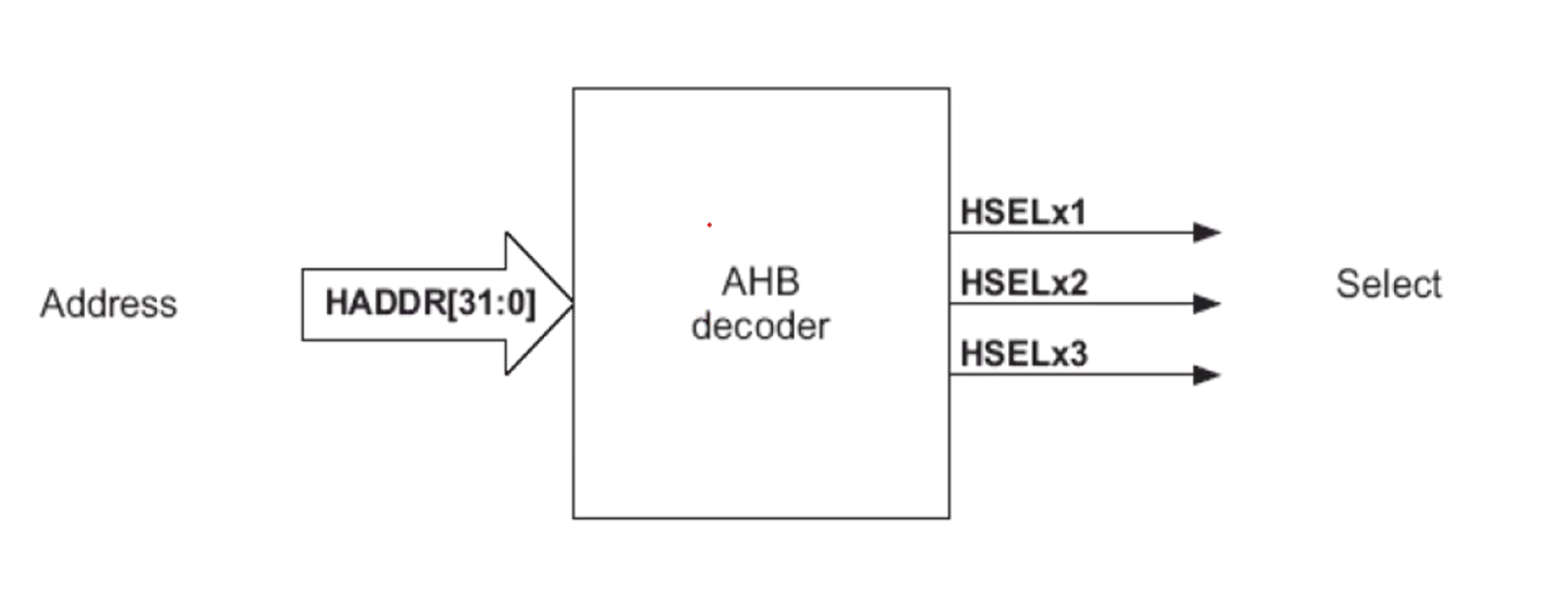

- AHB译码器 (decoder)

- 通过地址译码来决定选择哪一个从设备

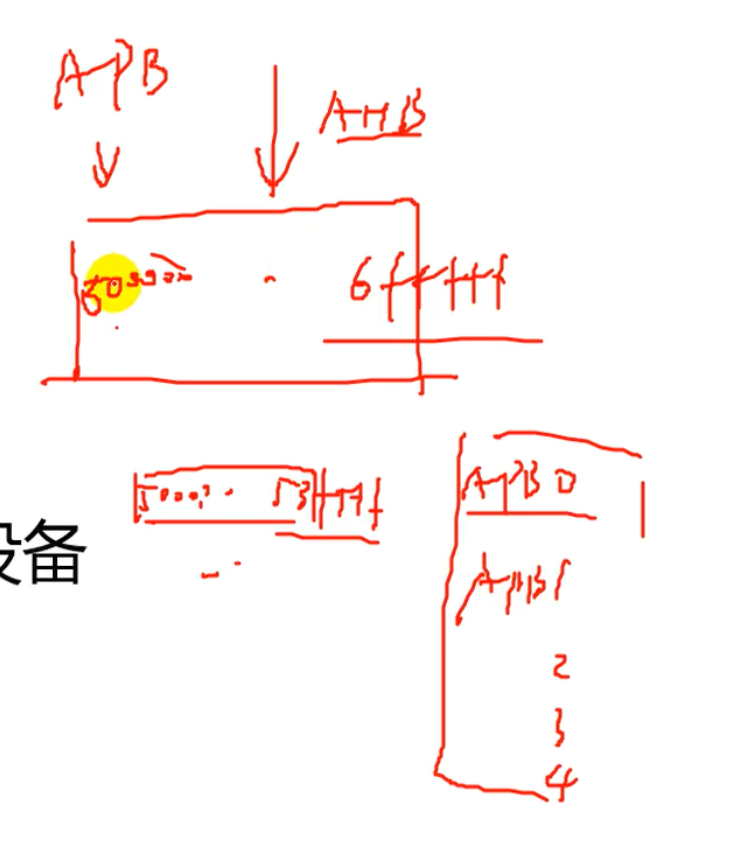

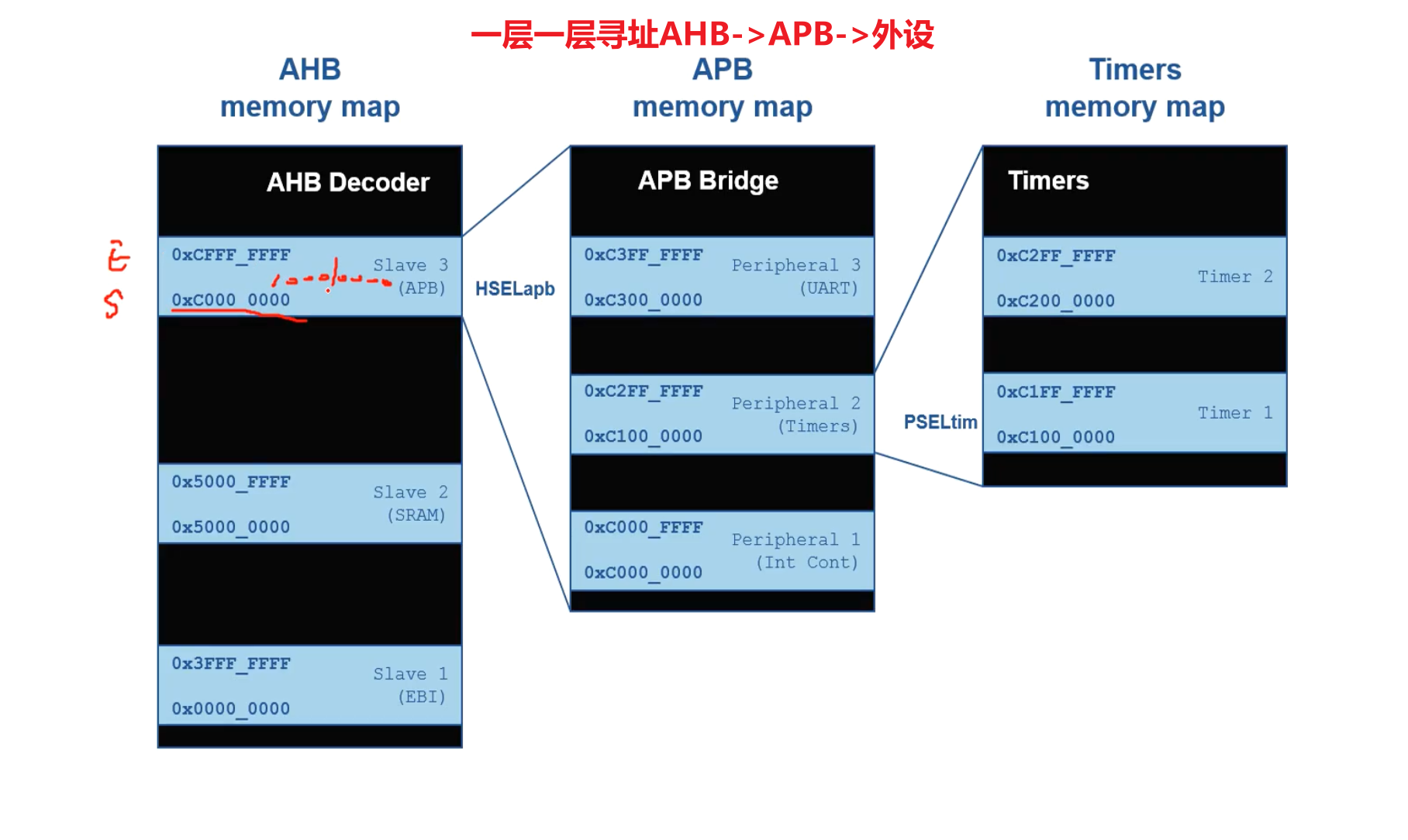

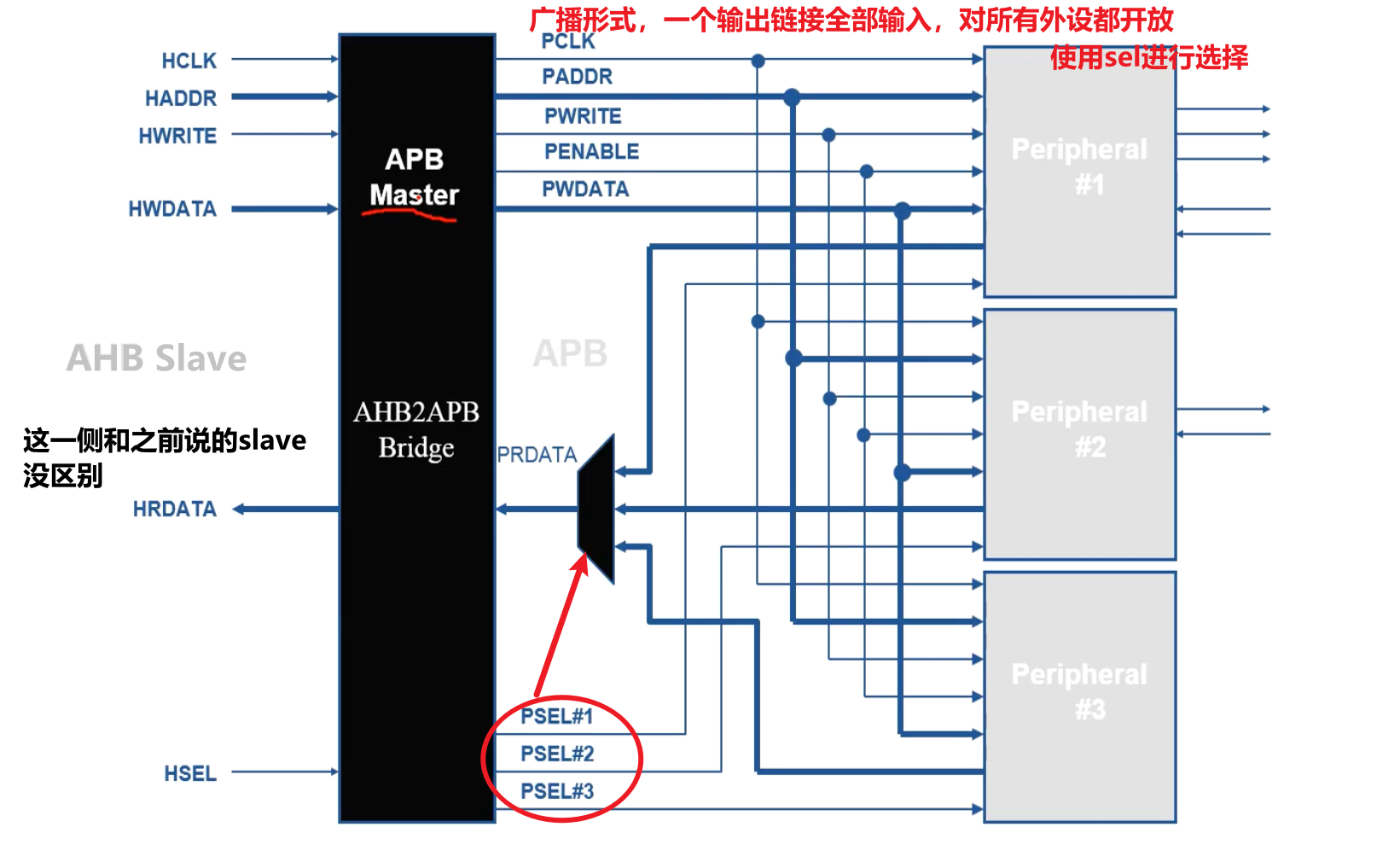

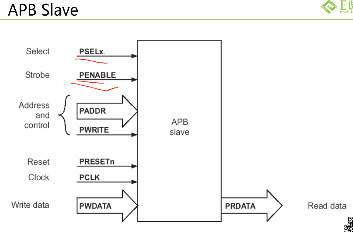

APB的组成部分

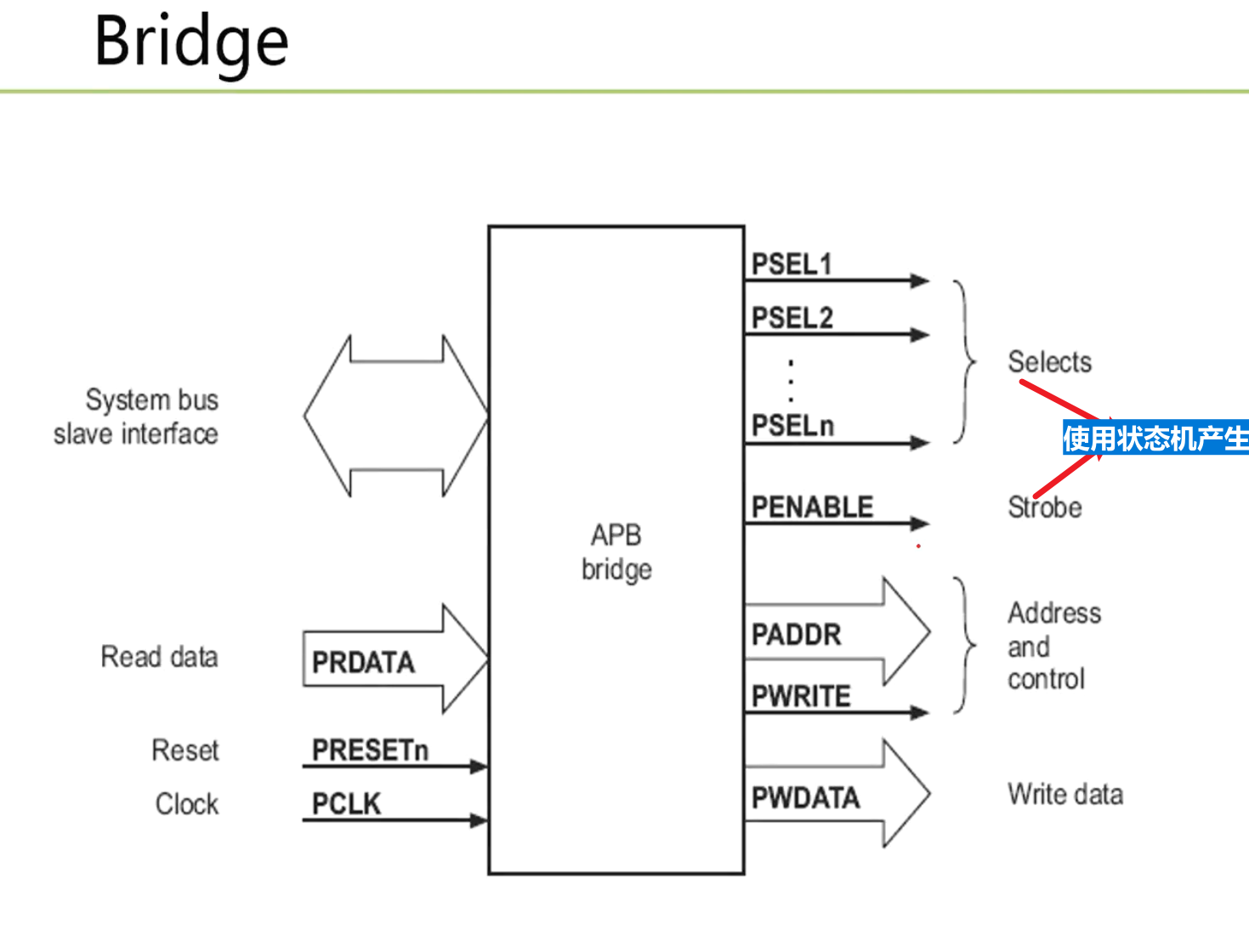

AHB2APB Bridge

- 可以锁存所有的地址、数据和控制信号

- 进行二级译码来产生APB从设备选择信号。如下图所示,AHB信号进来在进行二级译码

APB总线上的所有其他模块都是APB从设备

AMBA协议其他有关问题

- 与工艺无关

- 没有定义电气特性

- 仅在时钟周期级定义时序

- 提取时序参数依赖于所采用的工艺和工作频率

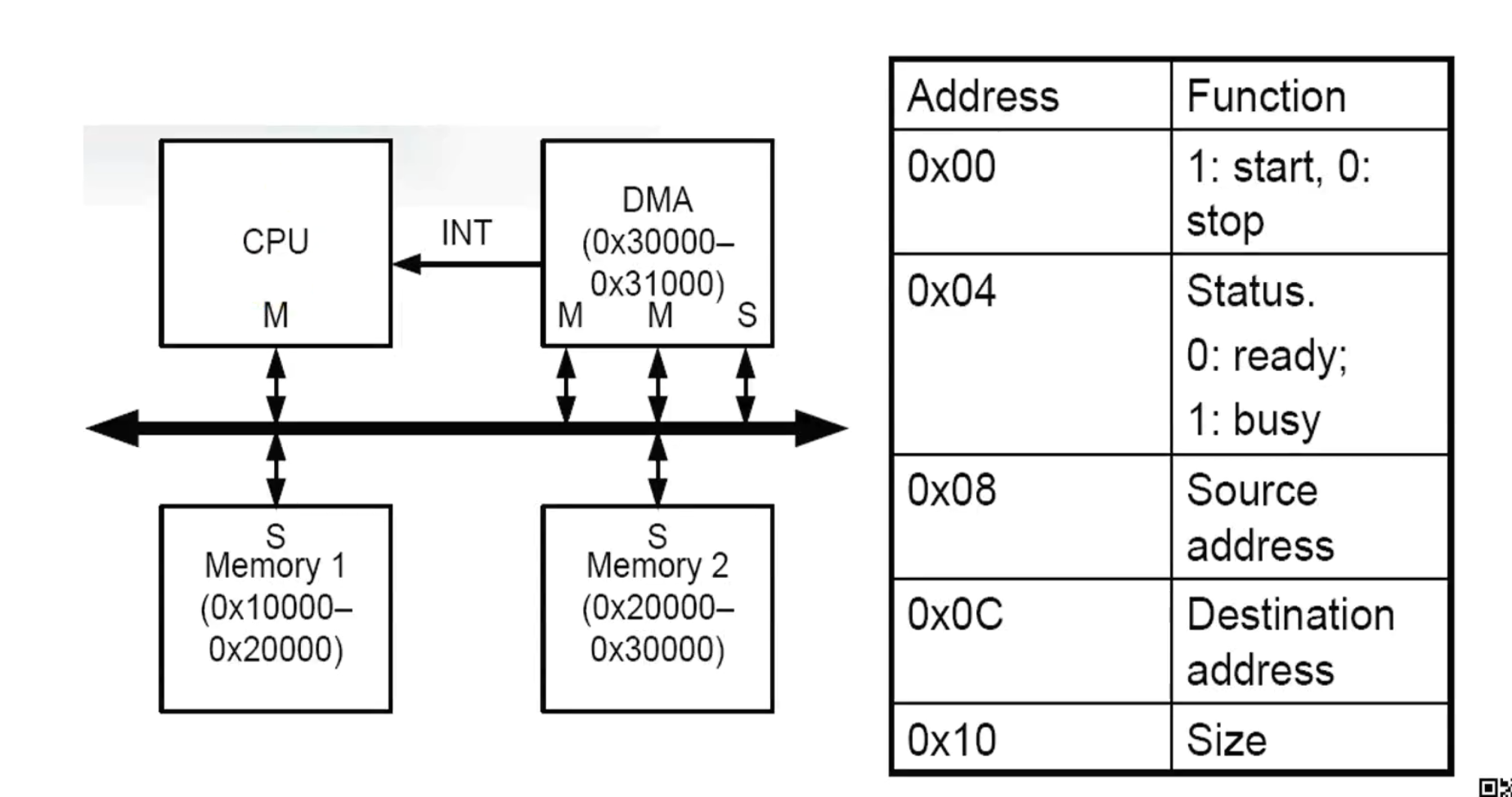

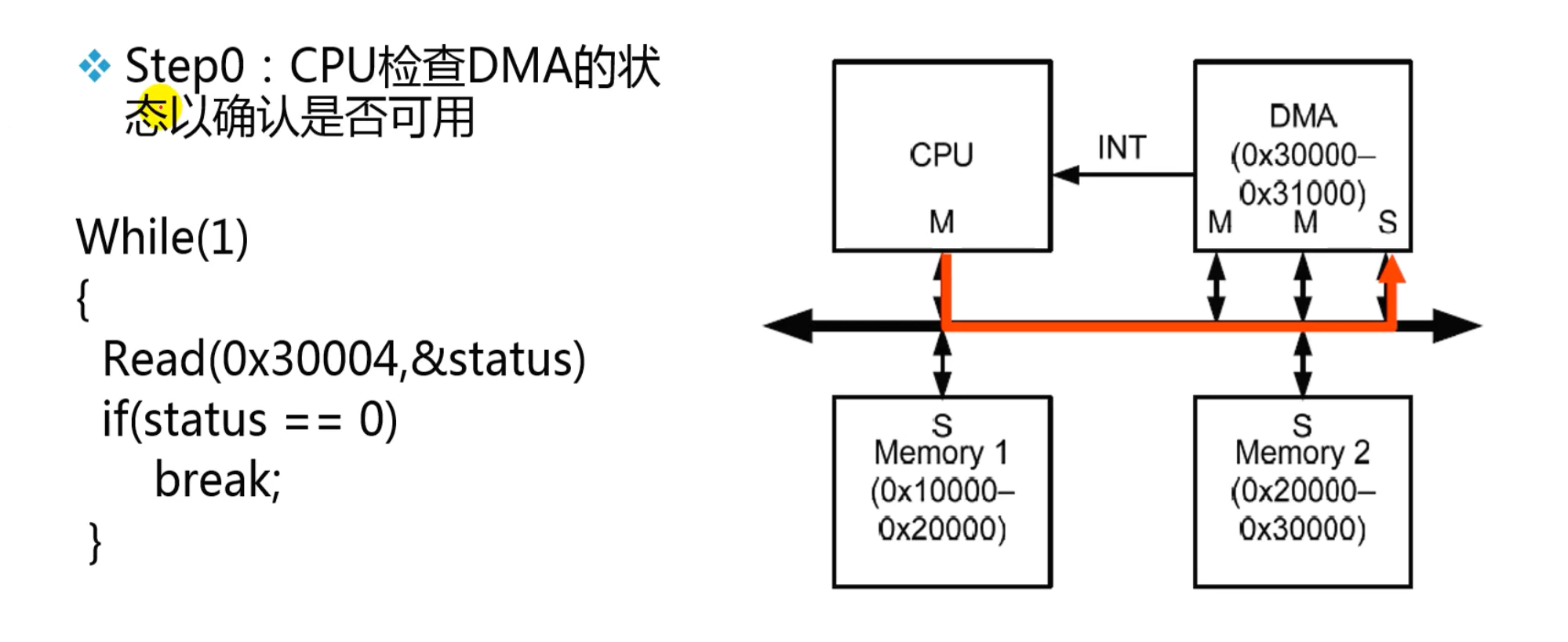

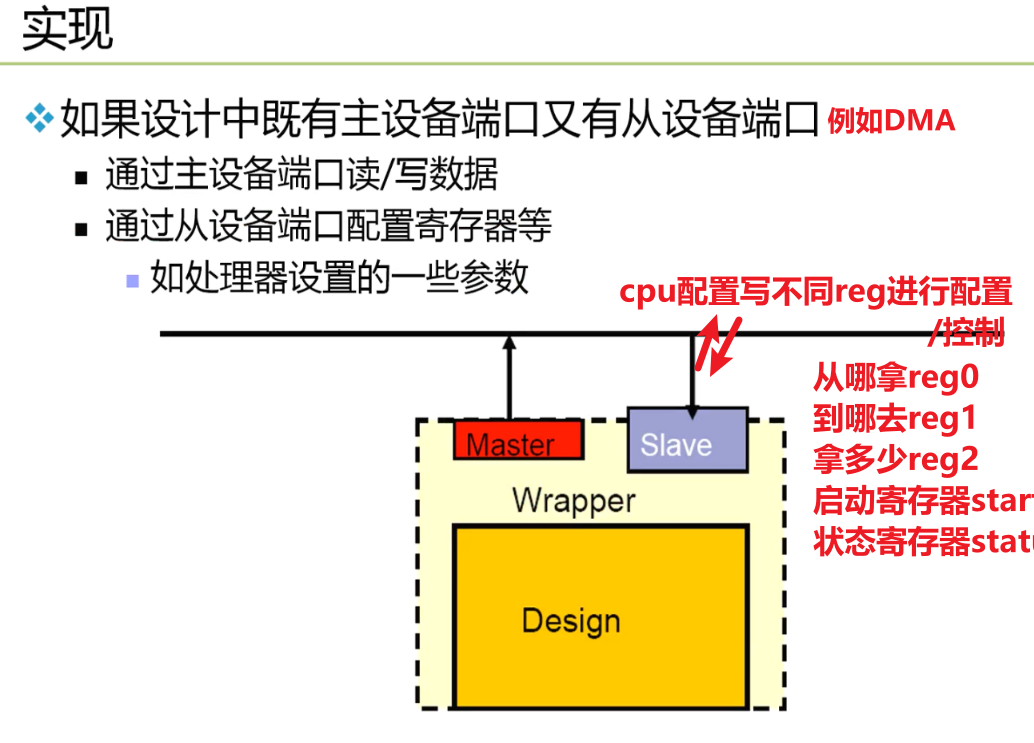

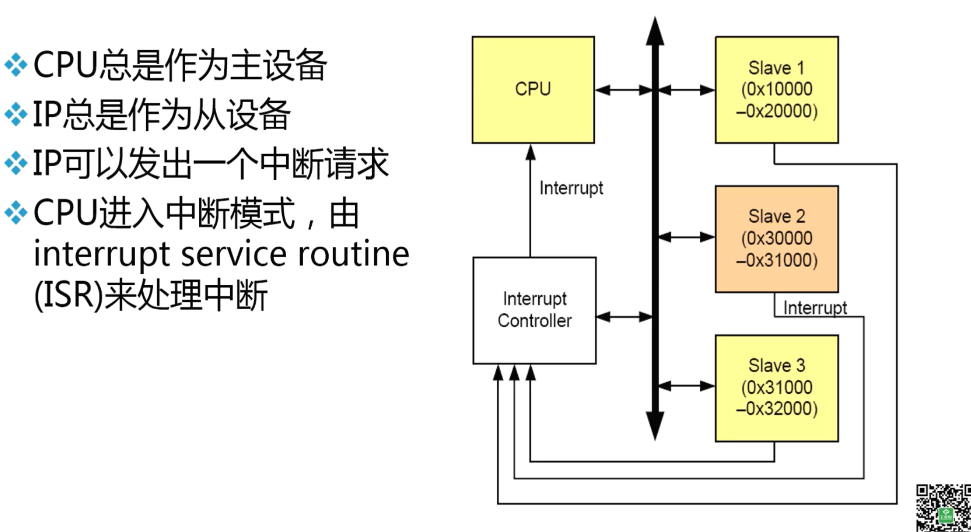

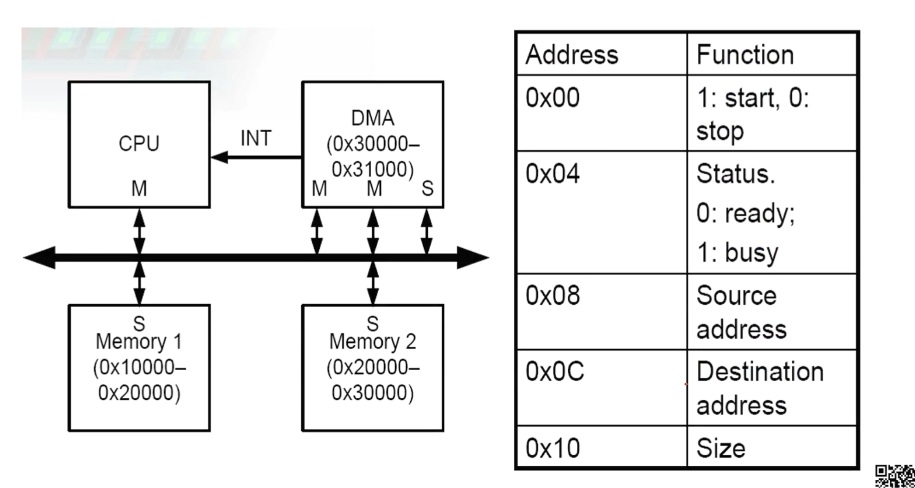

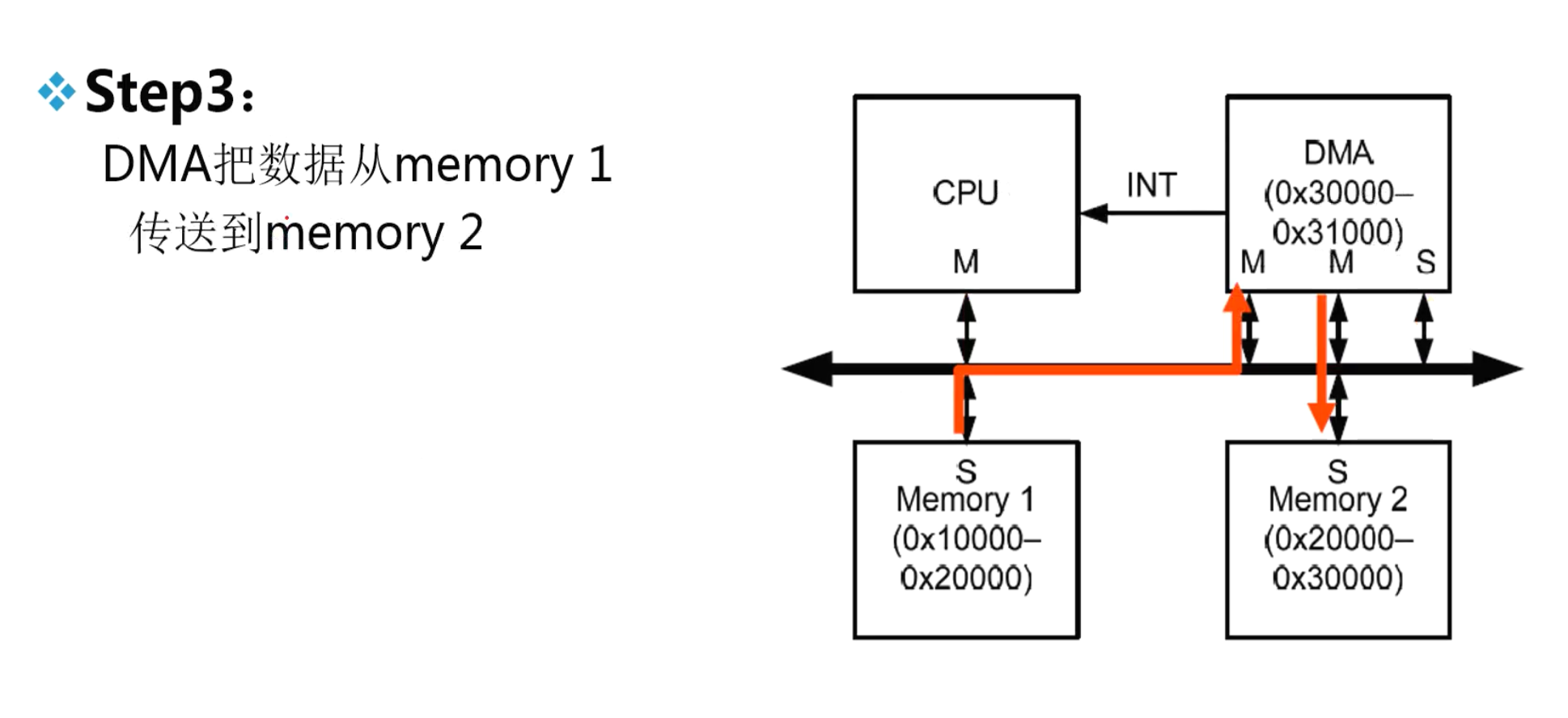

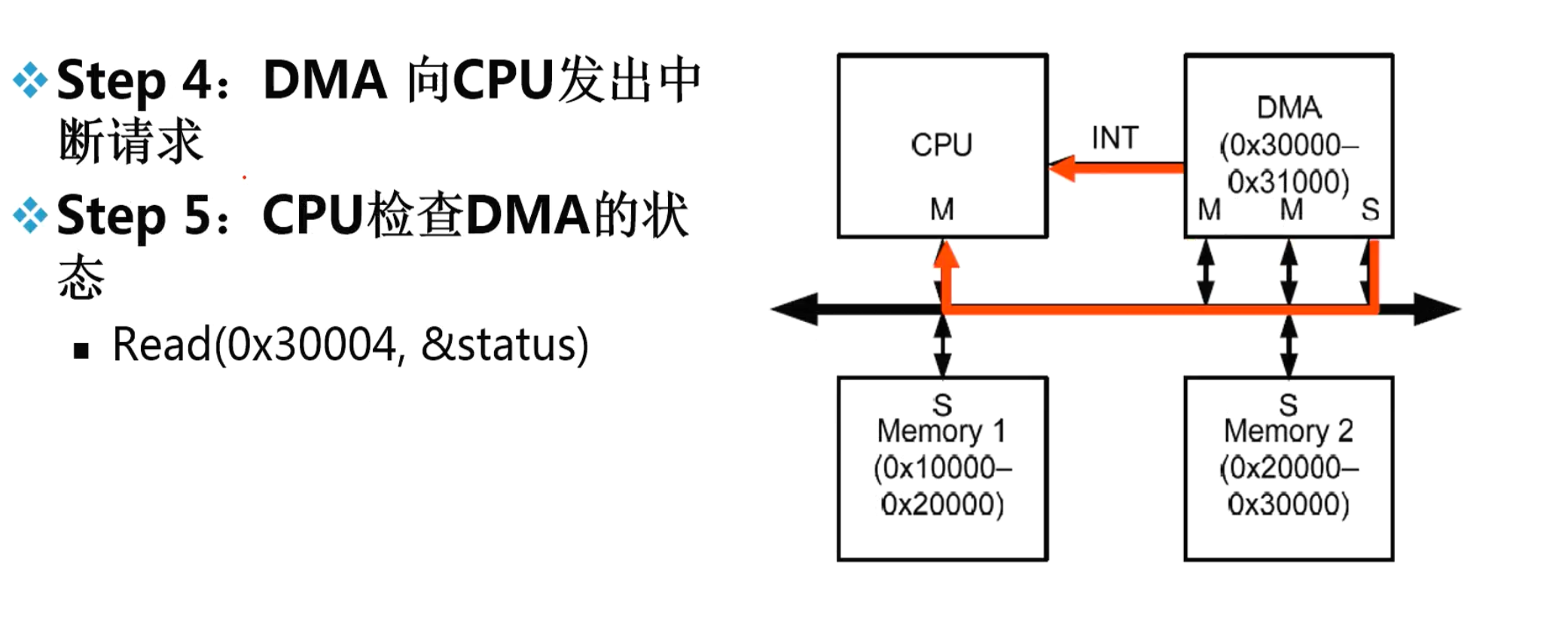

DMA

INT为中断,每当DMA读完数据会给CPU发送一个中断

*右表为DMA基础寄存器地址及其作用

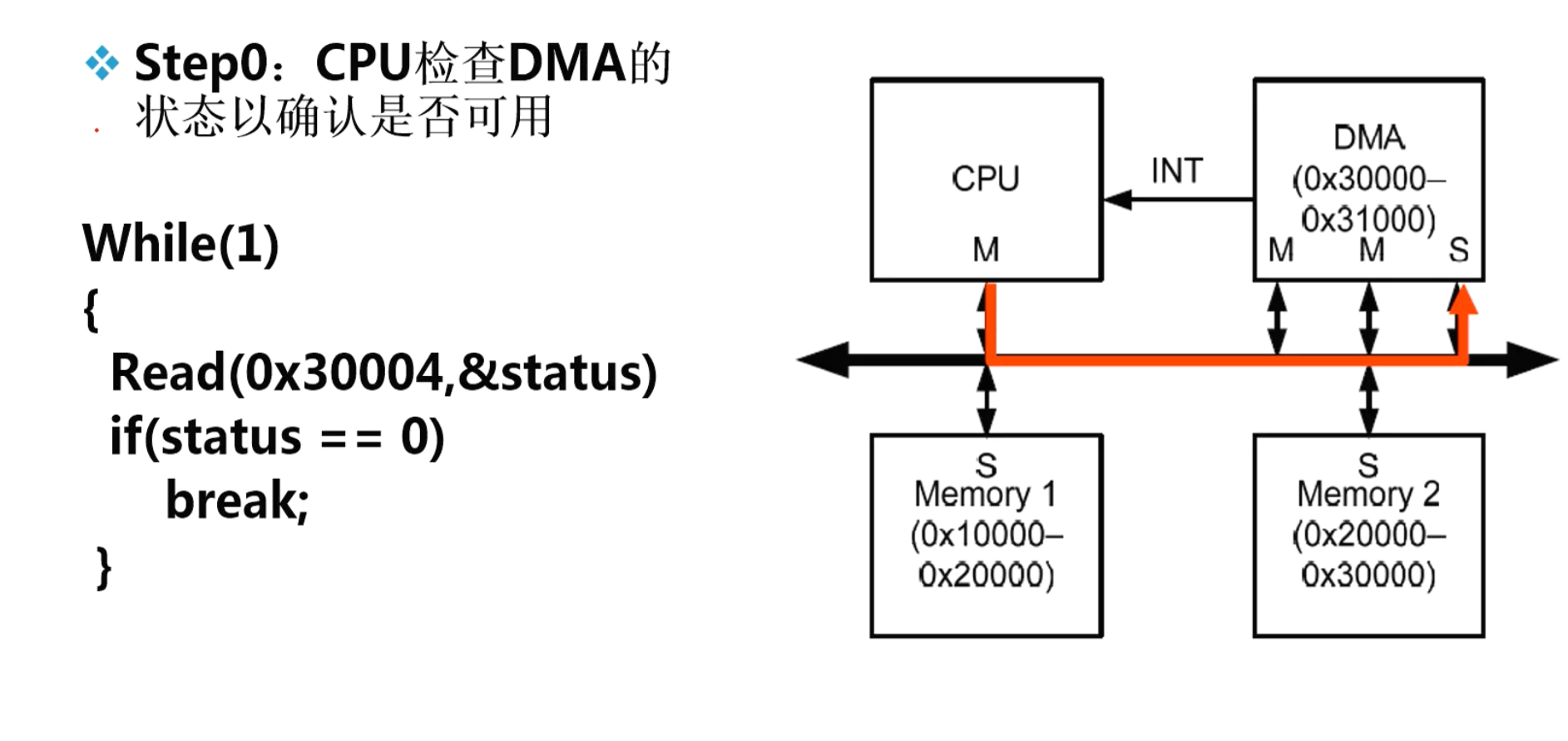

Step0: CPU检查DMA的状态以确认是否可用

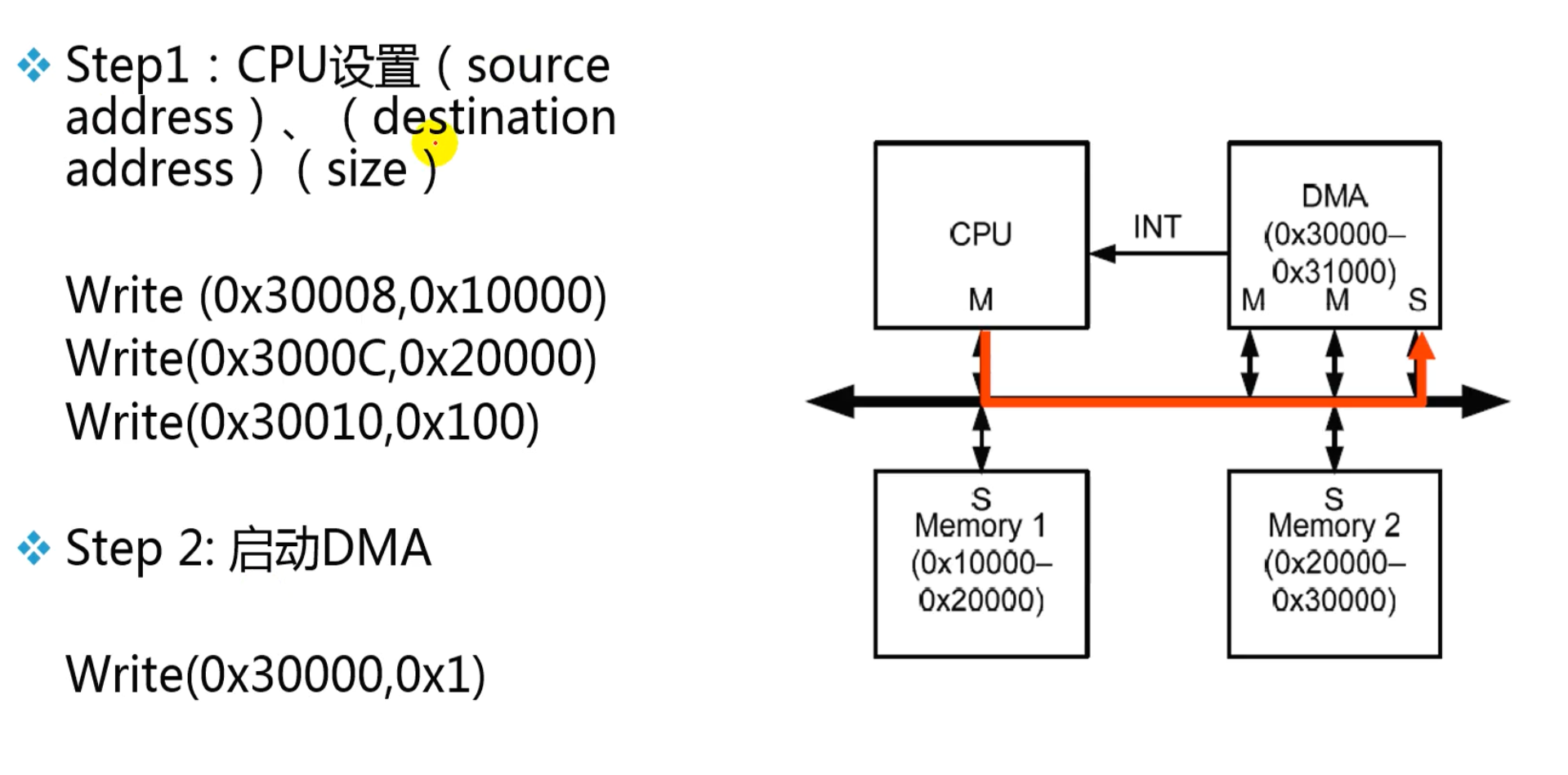

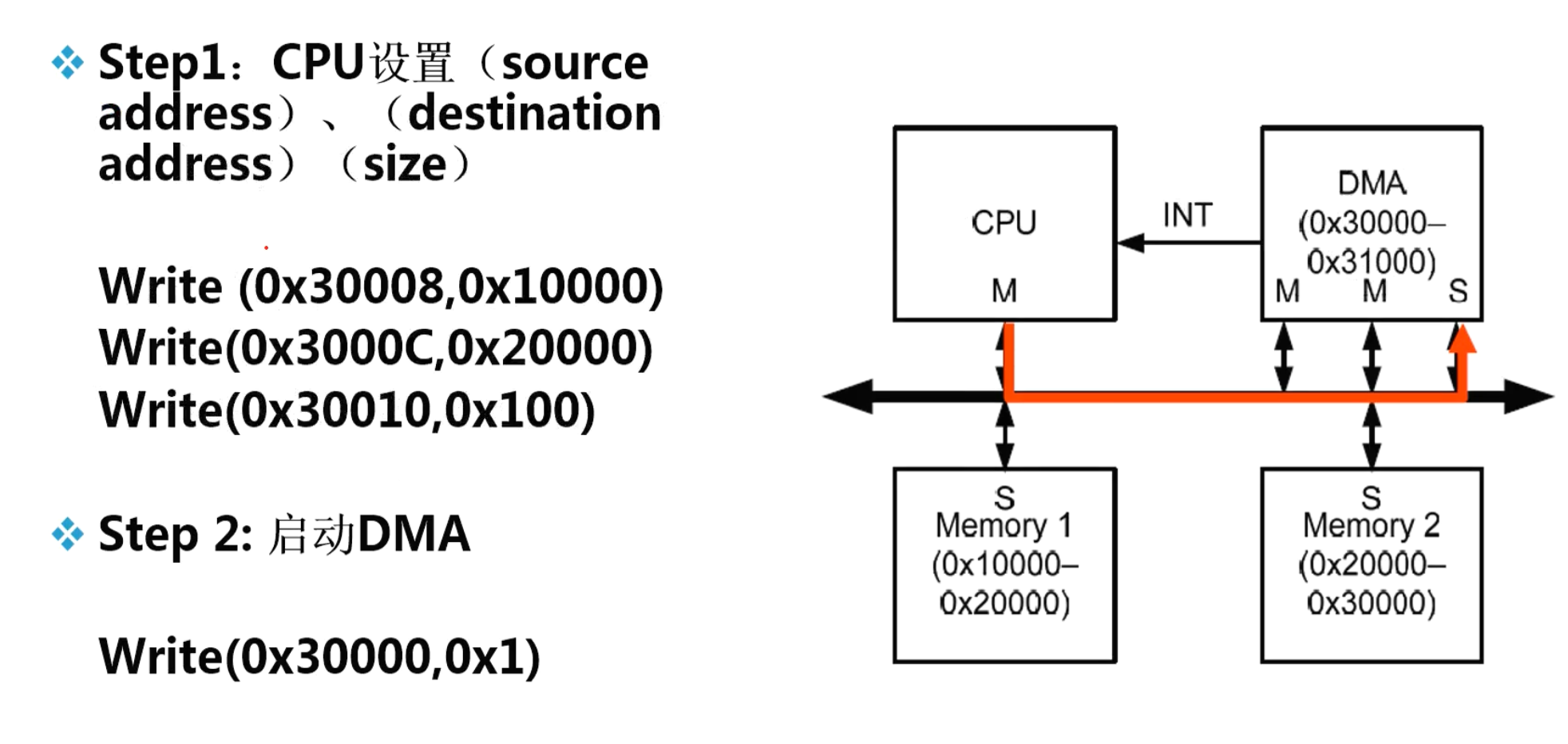

Step1: CPU设置(source address)(destination address)(size)

Step2: 启动DMA

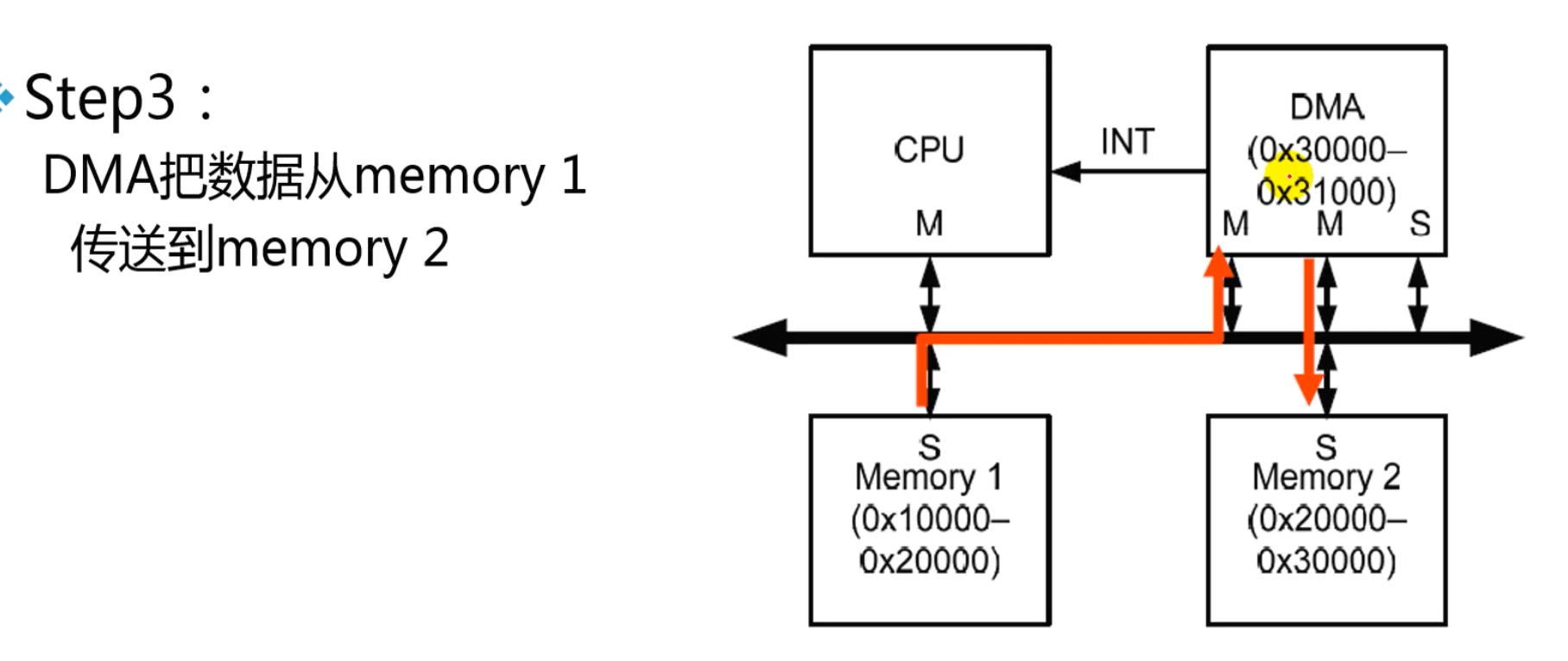

Step3: DMA把数据从memory 1传送到memory 2

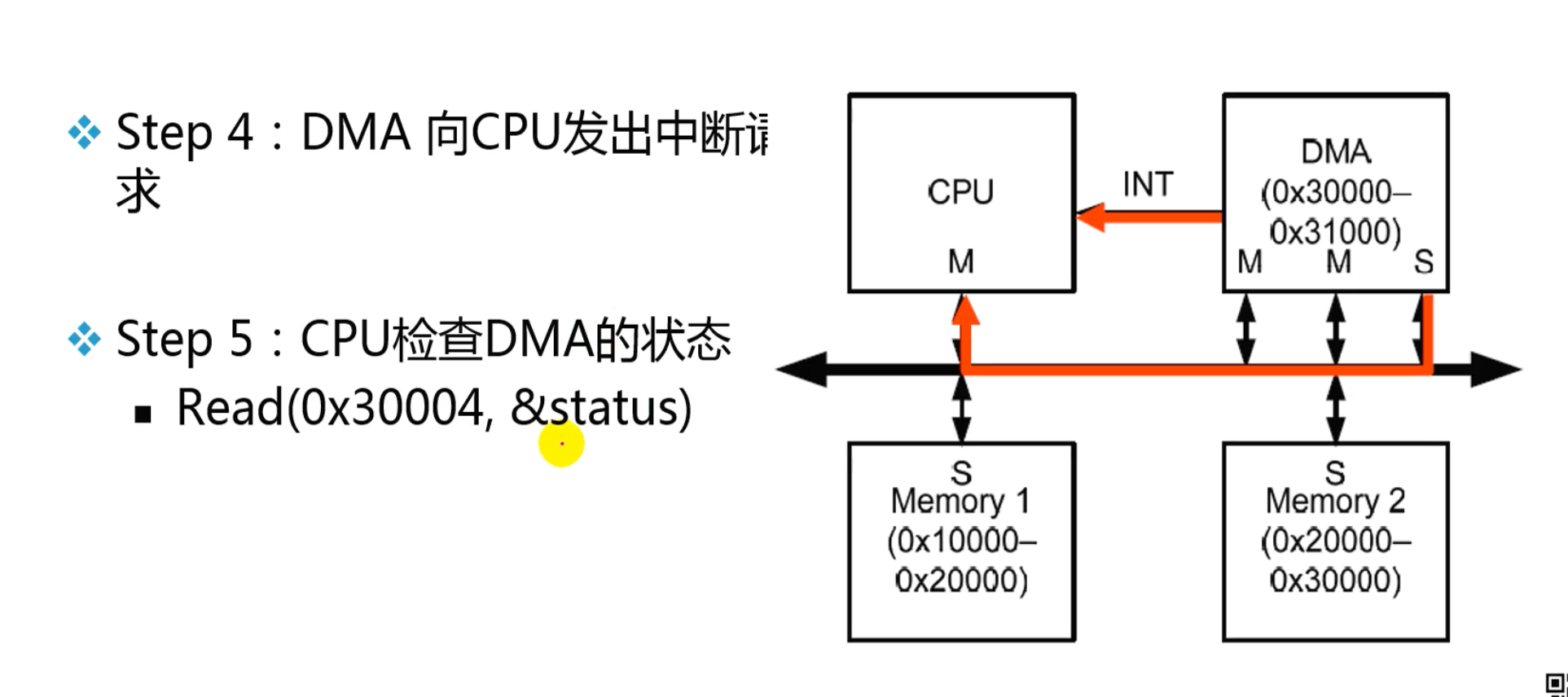

Step4: DMA向CPU发出中断请求

Step5: CPU检查DMA的状态 Read(Ox30004, &status)

2 AHB

一个典型的AMBA总线系统:

一个完整的AHB系统:

无效Master和默认Master

Dummy Master:所有master不工作SPLIT

- Granted when all masters SPLIT

- Generates IDLE cycles only

- Typically Master #0

- Granted when Locked master gets SPLIT response

- Implement as part of Address/Control Mux

Default:所有的master都没有在总线上是默认的master

- Granted when no master requires bus

Generally master most likely to require bus

Generates IDLE cycles when not requesting bus

- Avoids minimum 2 cycle Arbitration period

- Immediate access to bus

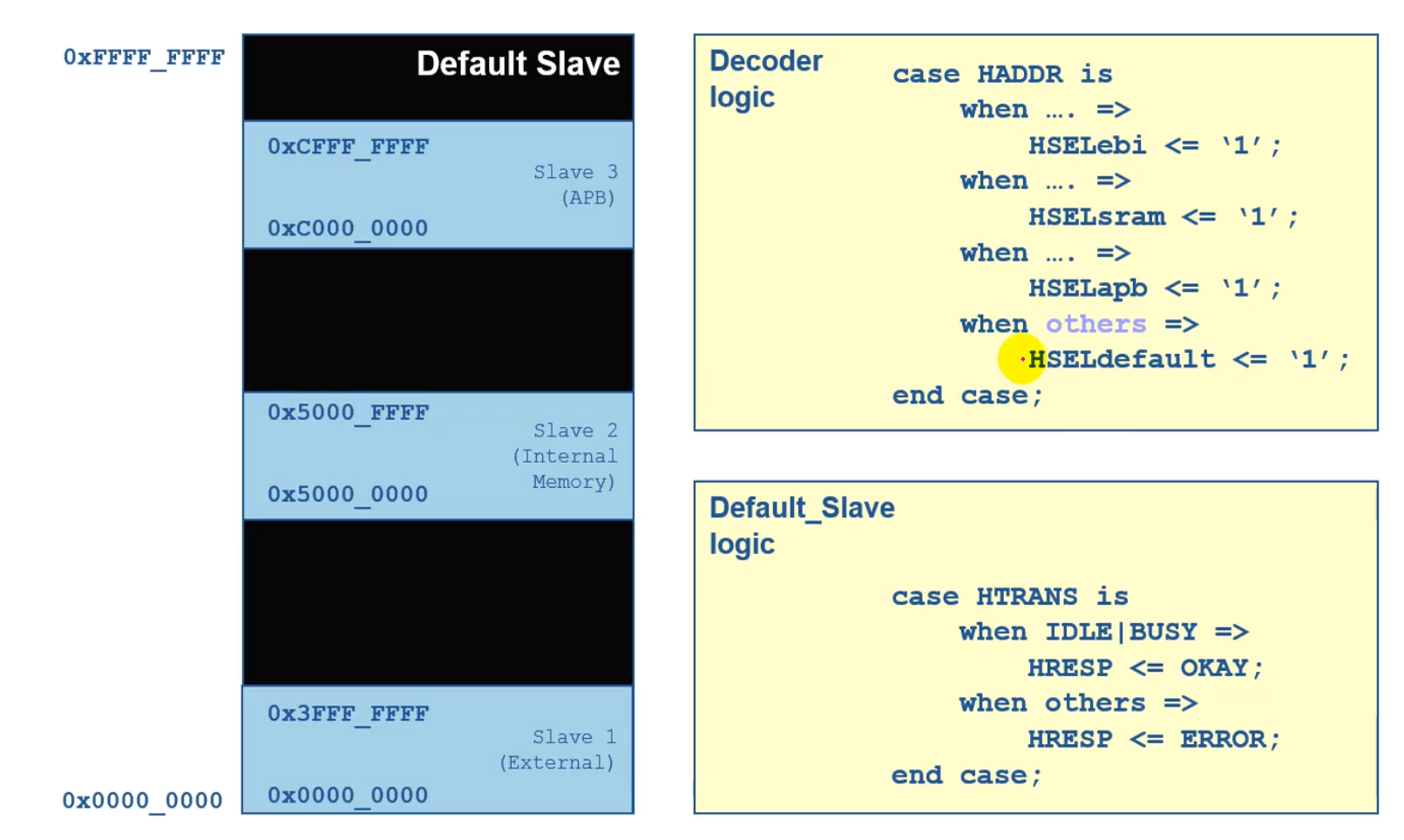

Default Slave

右边代码为默认解析逻辑

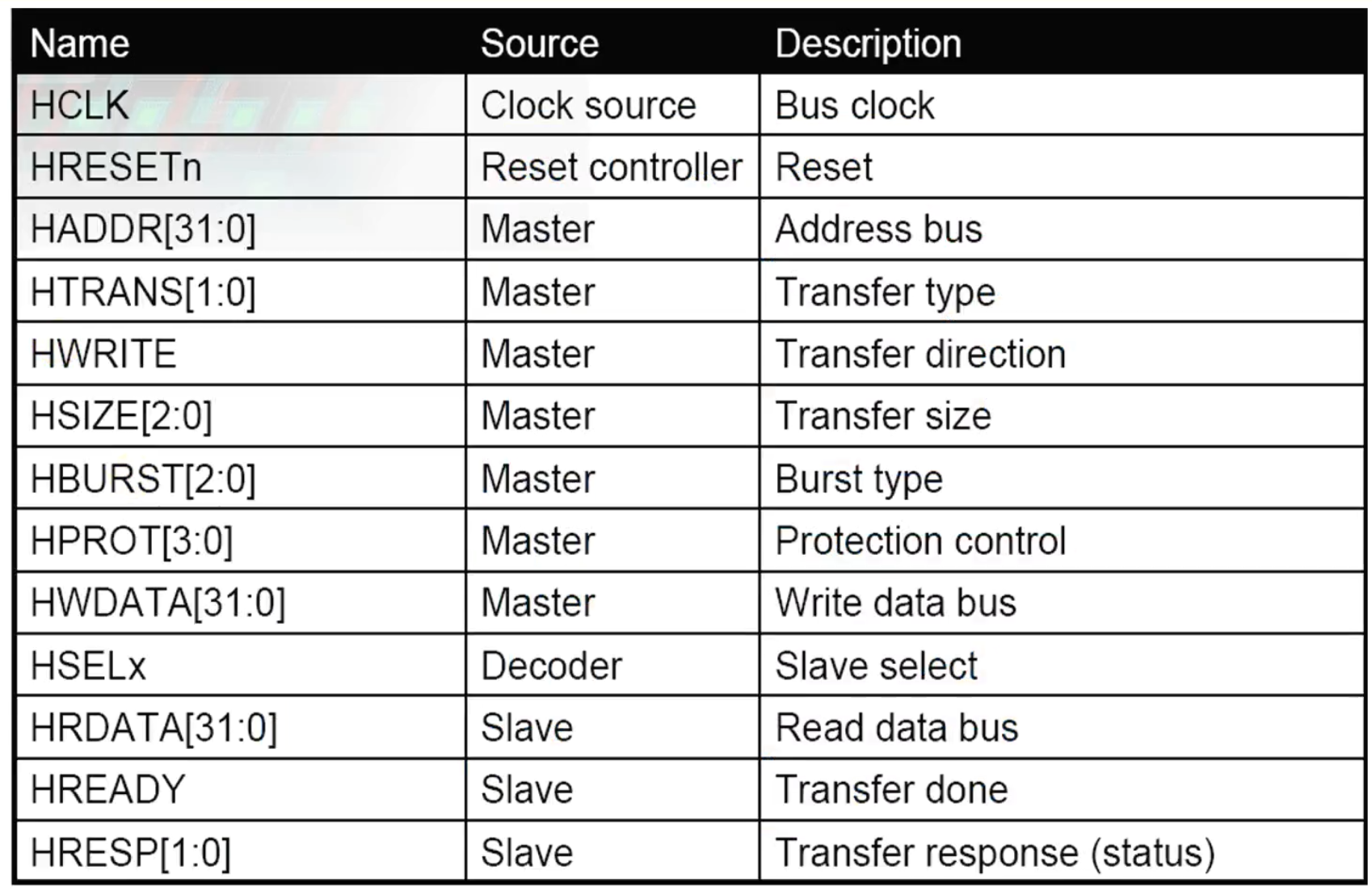

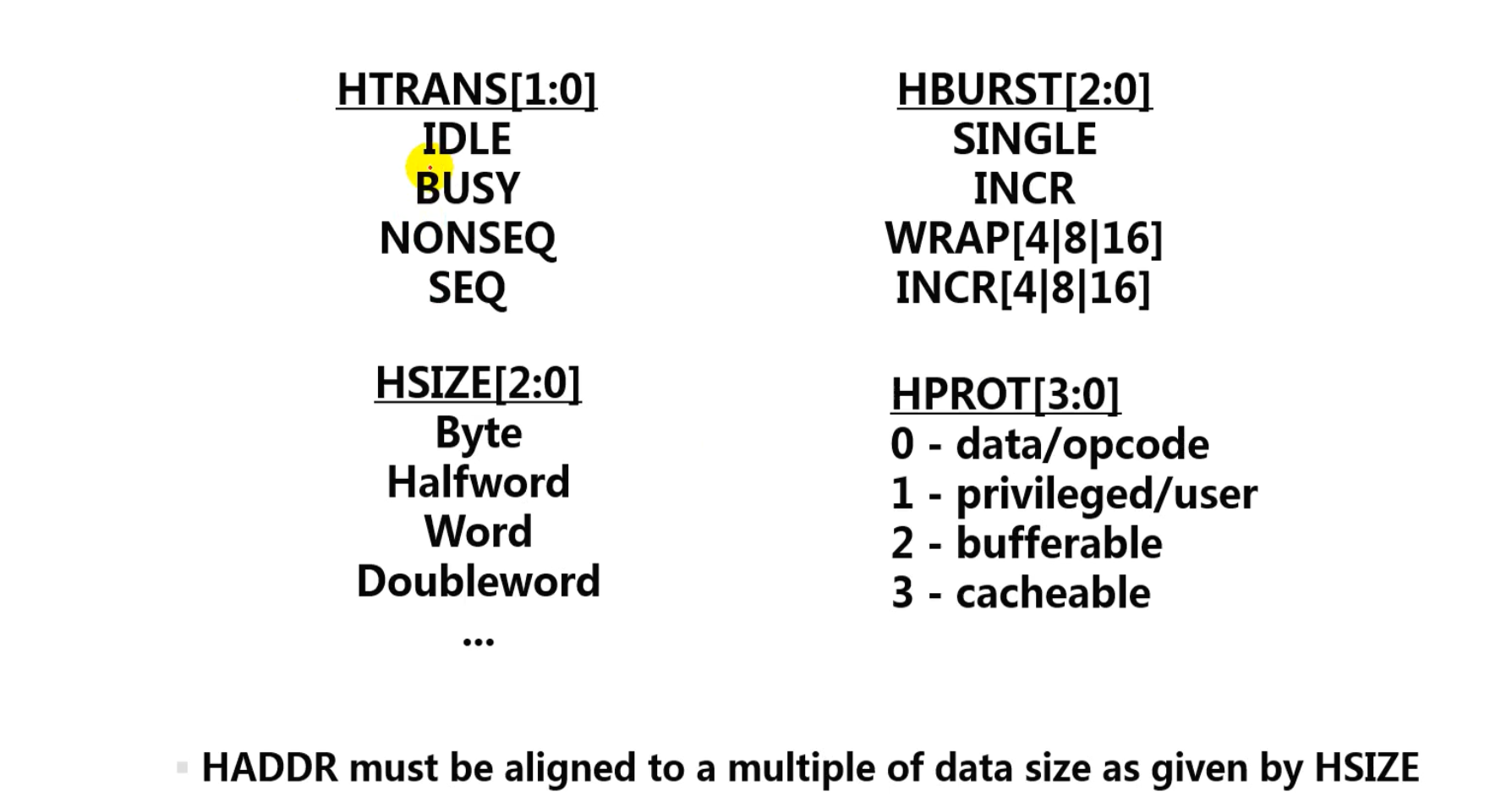

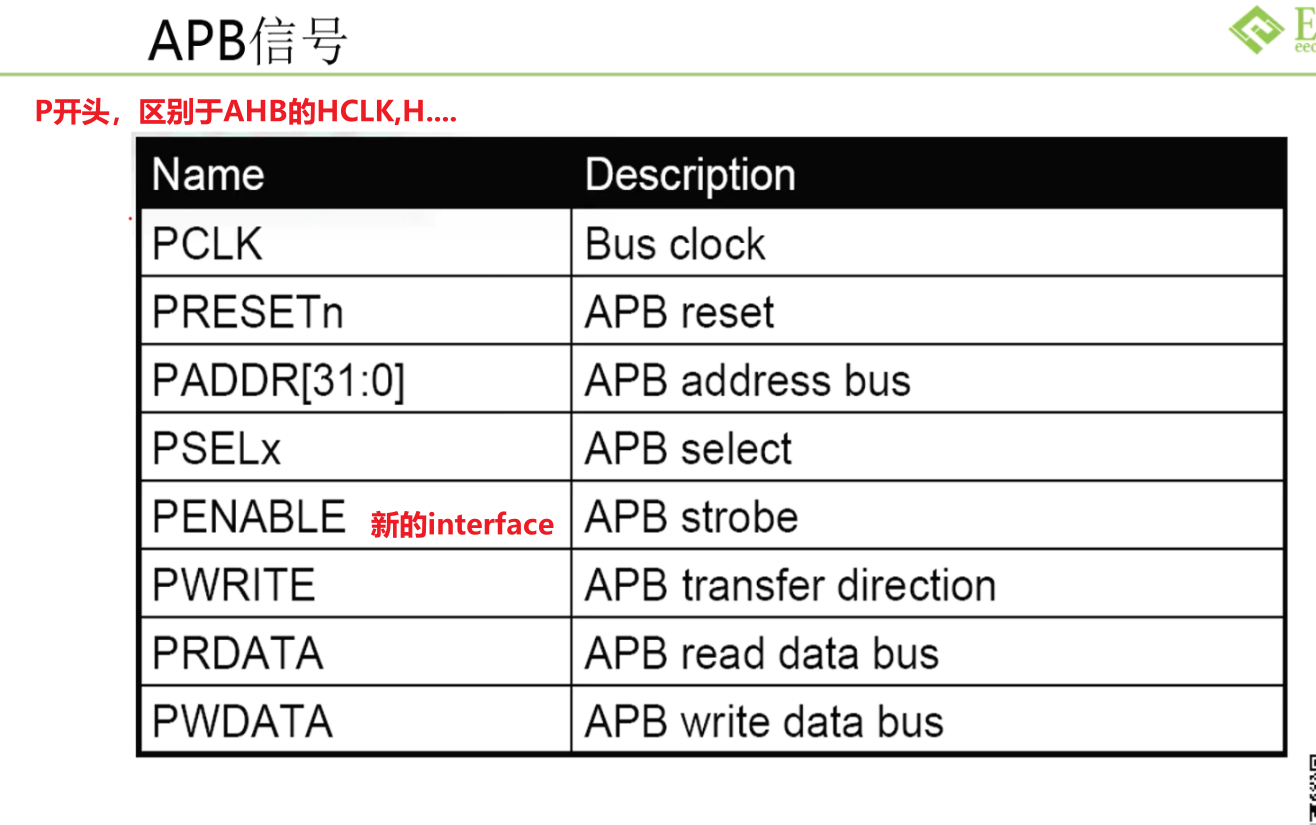

AHB信号

AHB信号是H开头,APB信号是P开头

- HCLK,AMBA是一种同步协议

- HRESETn,低电平有效

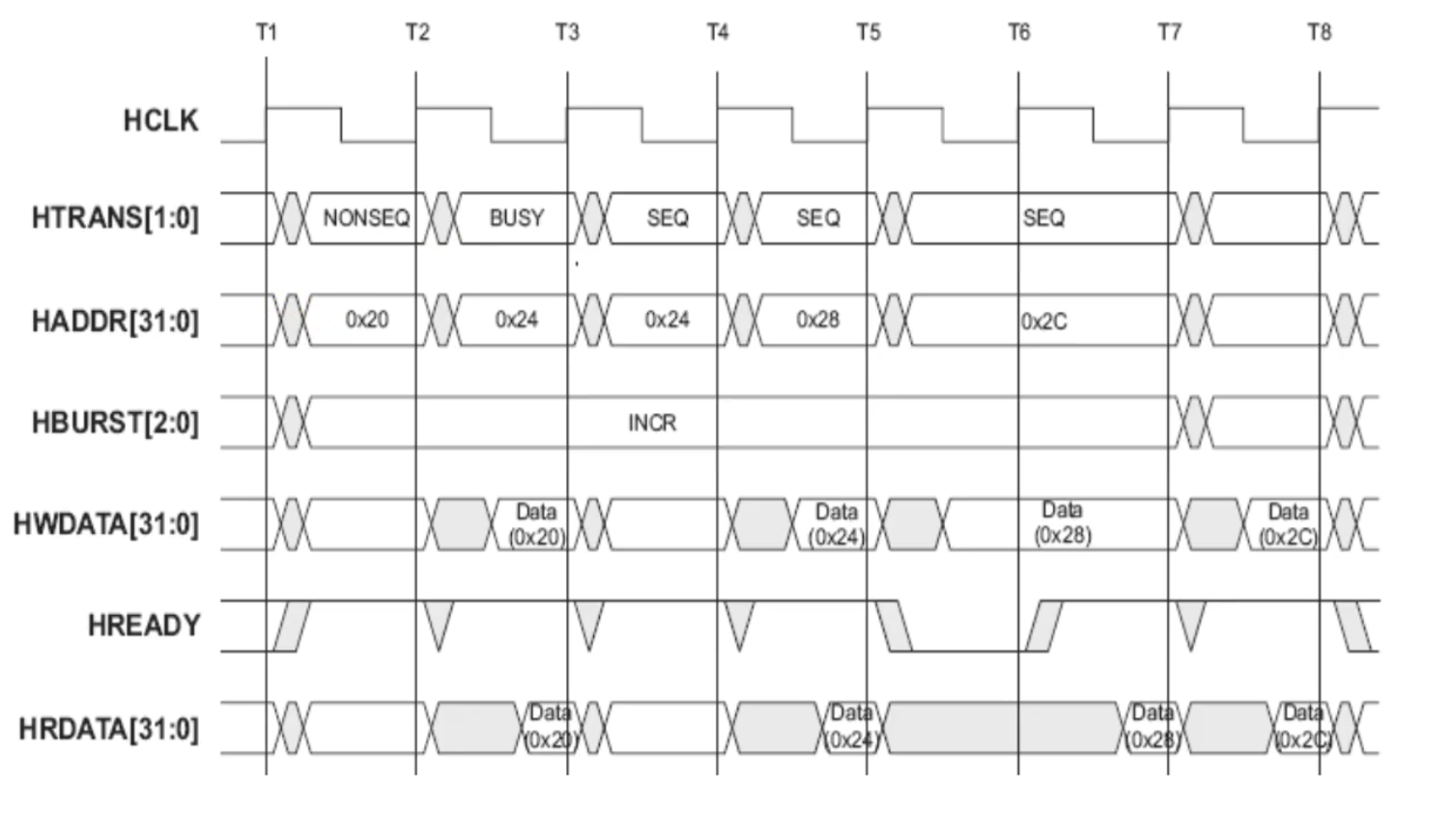

- HTRANS,四种类型:IDLE BUSY NONSEQ SEQ

- HWRITE,1为写0为读

- HSIZE,BUS的宽度,以字节为单位(0为8位,1为16位,2为32位)

- HBURST

- HPROT,一般情况不用

- HSELx,注意每个HSELx是1位的,由x指定某个slave被选中

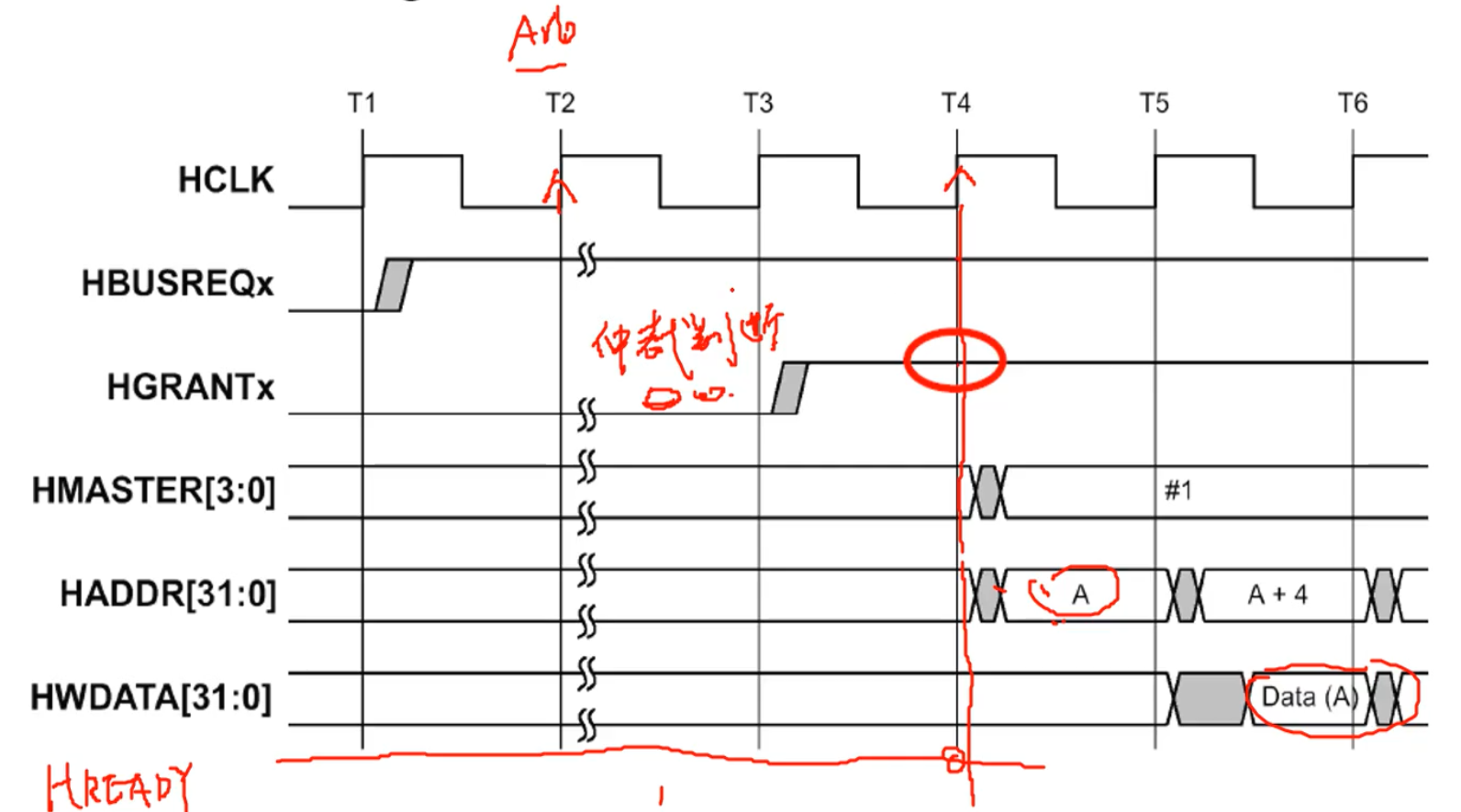

- HREADY,slave提供给master使其进行判断为高才能工作

- HRESP,slave提供给master

具体解释

- HRESETn

- 低电平有效

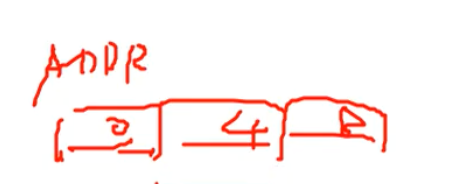

HADDR[31:0]

- 32位系统地址总线

HWDATA[31:0]

- 写数据总线,从主设备写到从设备

- HRDATA[31:0]

- 读数据总线,从从设备读到主设备

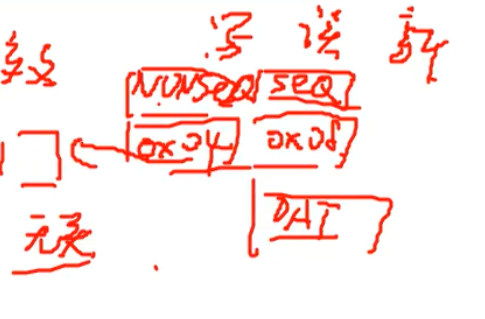

- HTRANS

- 指出当前传输的状态

- NONSEQ、 SEQ、 IDLE、 BUSY

- IDLE和BUSY时,ADDR与DATA无效

- NONSEQ,表达开启了一次新的写

- SEQ,在NONSEQ后的数据

- NONSEQ表示ADDR与之前地址无关,SEQ表示ADDR与之前地址有关

- NONSEQ、 SEQ、 IDLE、 BUSY

- 指出当前传输的状态

- HSIZE

- 指出当前传输的大小

- HBURST(重要)

- 指出传输的burst类型,有八种

- HRESP (slave output)

- 从设备发给主设备的总线传输状态

- OKAY、ERROR、RETRY、SPLIT

- RETRY不影响被拒绝的master的优先级

- SPLIT会让arbiter降低master优先级

- OKAY、ERROR、RETRY、SPLIT

- 从设备发给主设备的总线传输状态

- HREADY (slave output)

- 高:从设备指出传输结束

- 低电平:从设备需延长传输周期

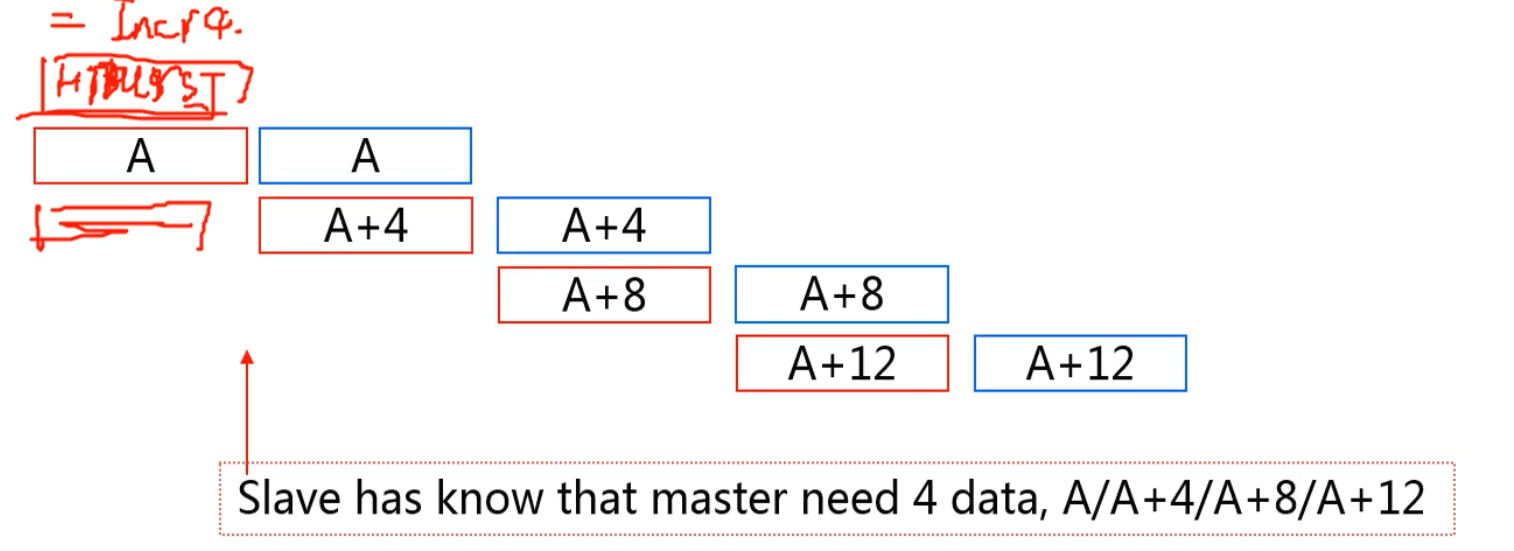

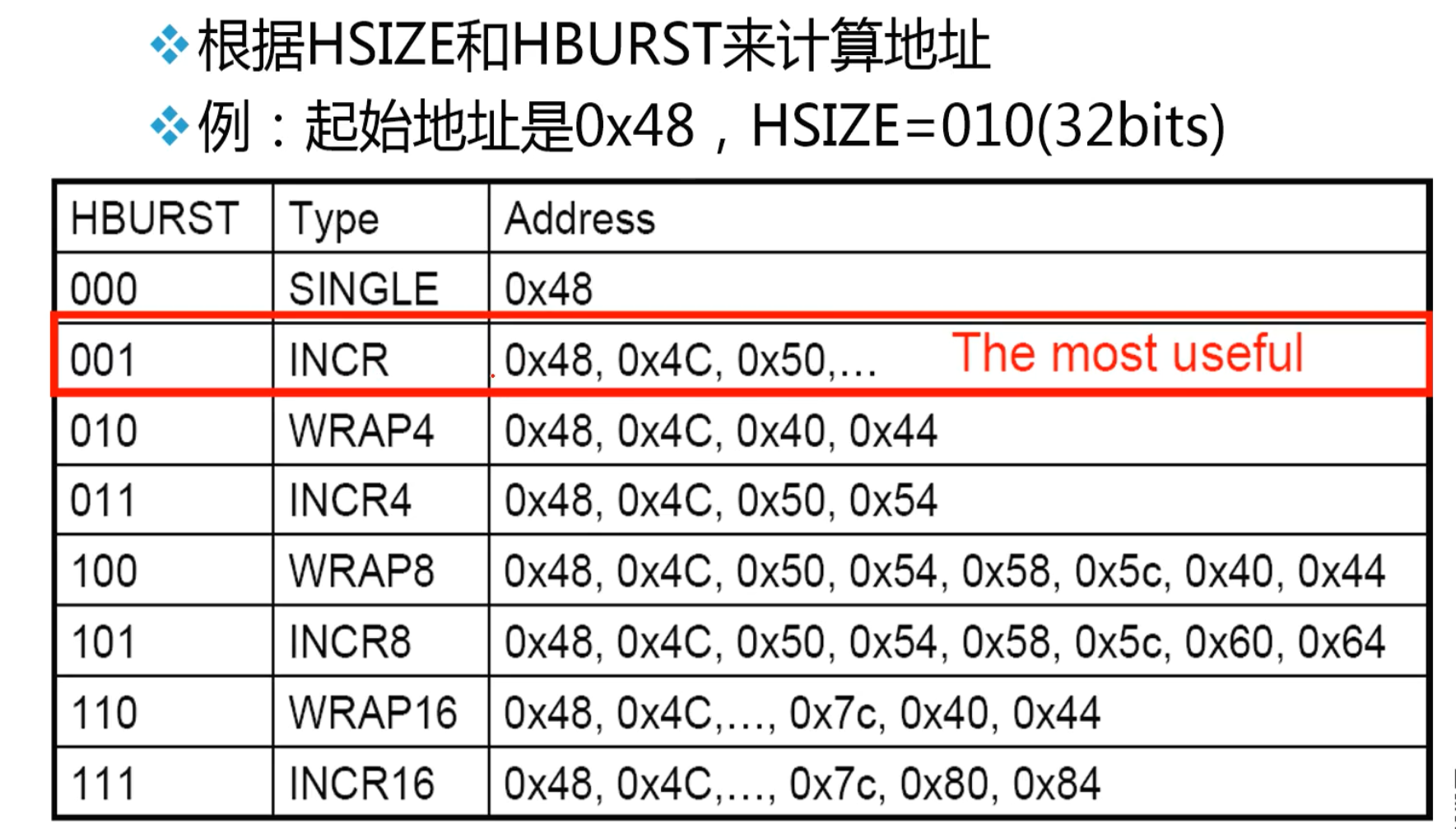

补充:为什么addr是4byte4byte加的?

当HSIZE=010时,数据是32bit的,每次写入32bit,因此4byte的加

更进一步,其实是和HSIZE有关,HADDR must be aligned to a multiple of data size as given by HSIZE

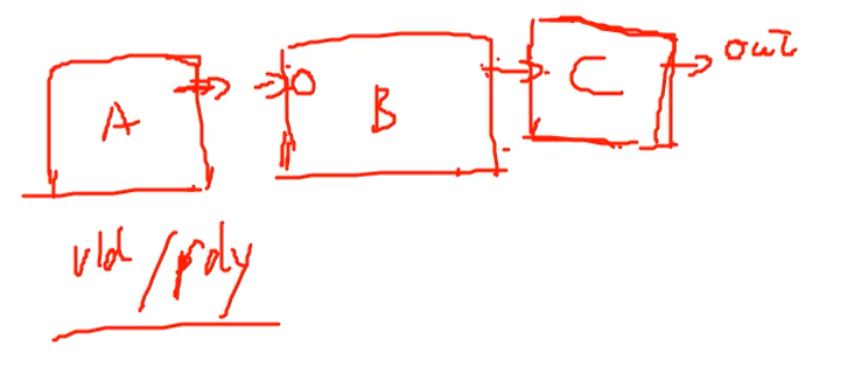

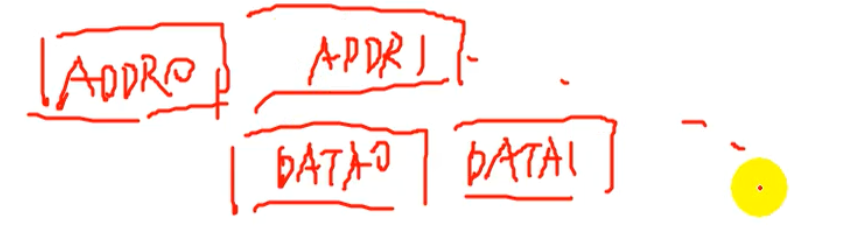

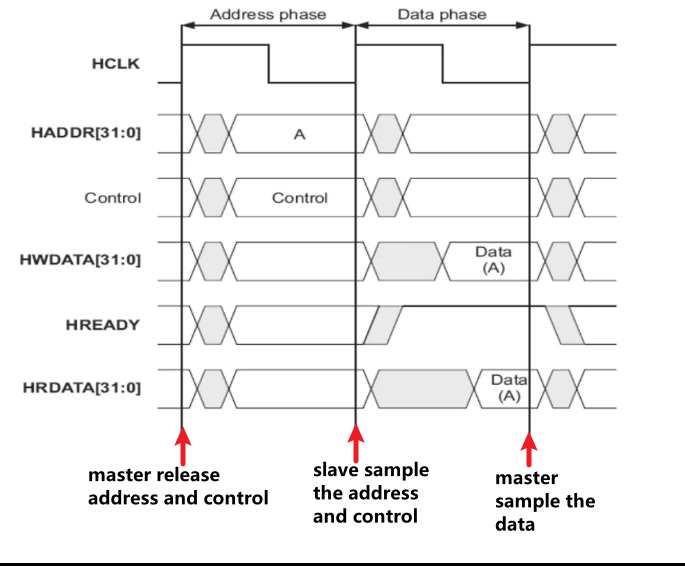

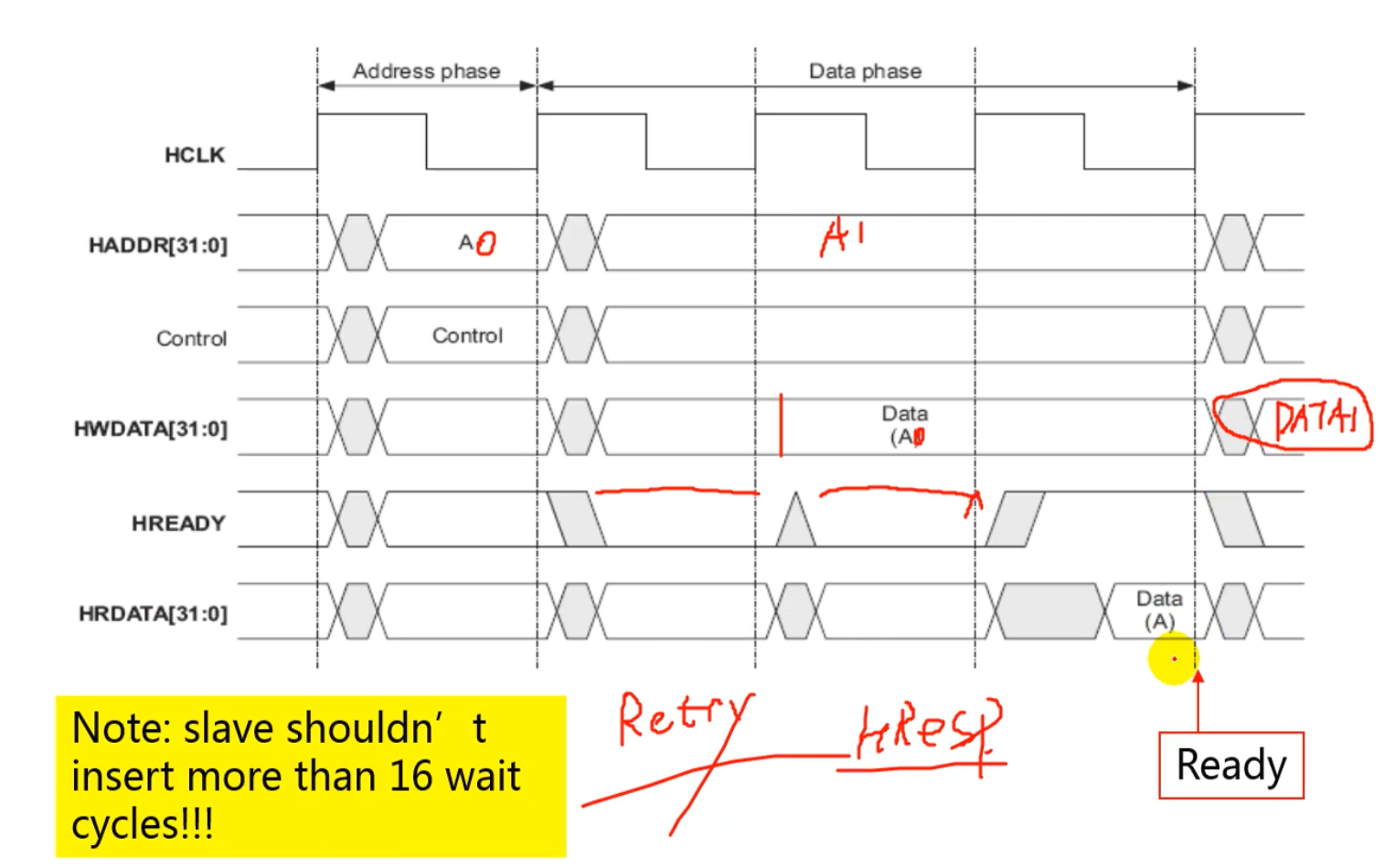

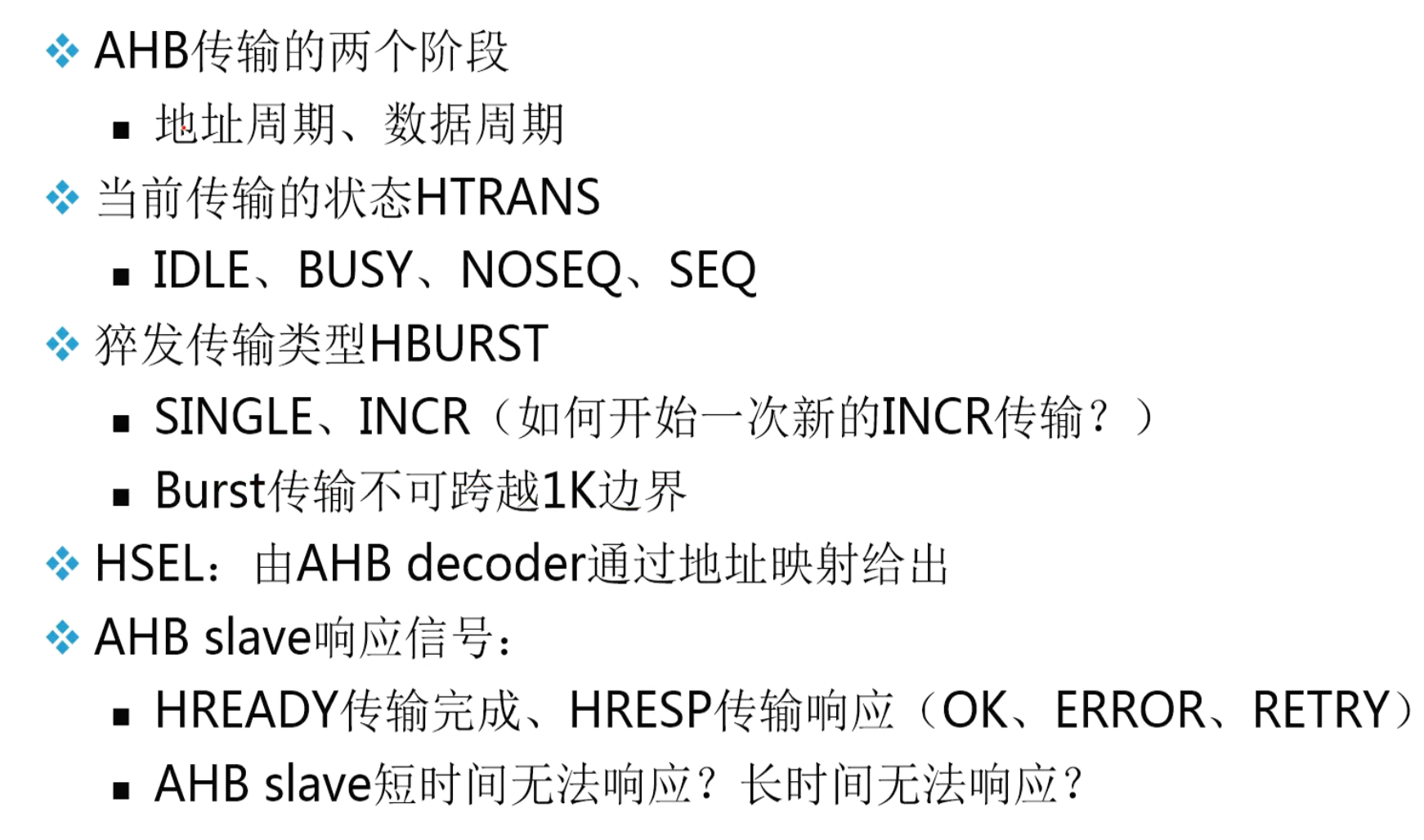

基本AHB传输

两个阶段

- 地址周期,由HREADY决定需要几个cycle

- 数据周期,由HREADY决定需要几个cycle

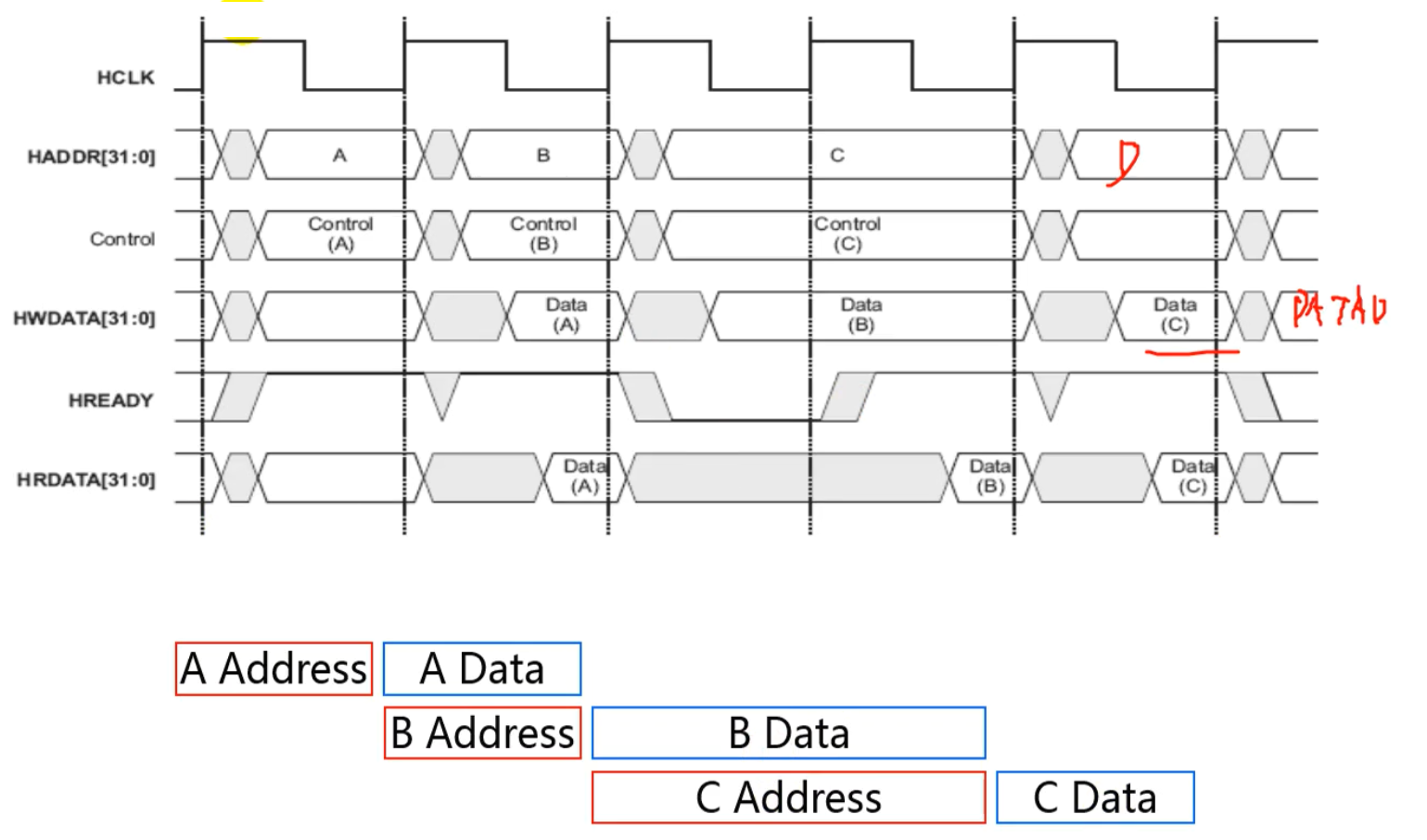

流水线传送

- 先是地址周期,后是数据周期,如下图所示

一次无需等待的简单传输(单周期读写)

需要两个等待周期的简单传输

slave不应该等待超过16个cycle,此时slave在HRESP返回一个RETRY

使用pipline进行改进

- 使用burst进行连续传输,减少Decode等待时间

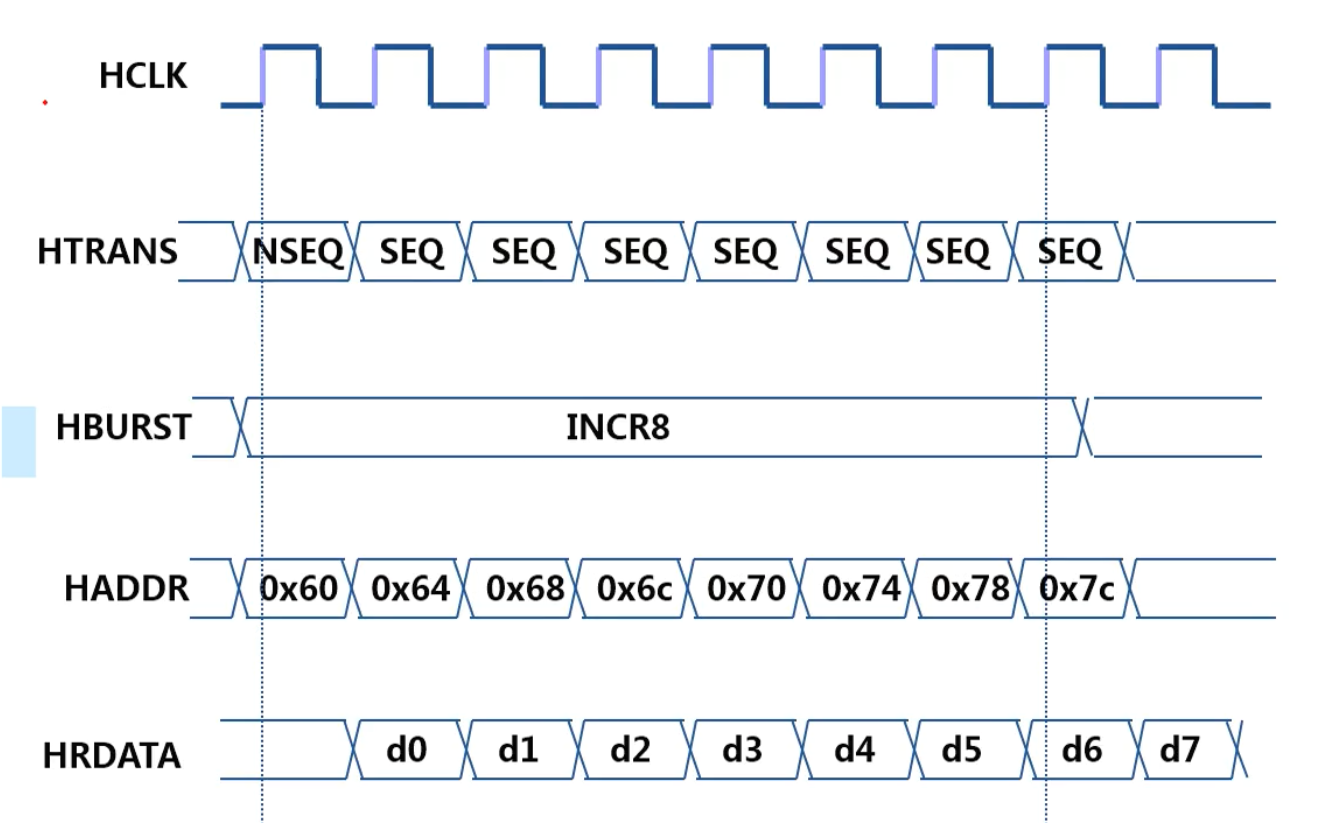

Burst Transfer [2 : 0]

- HBURST shows the burst types:

- 000 Single Transfer:只传输一次

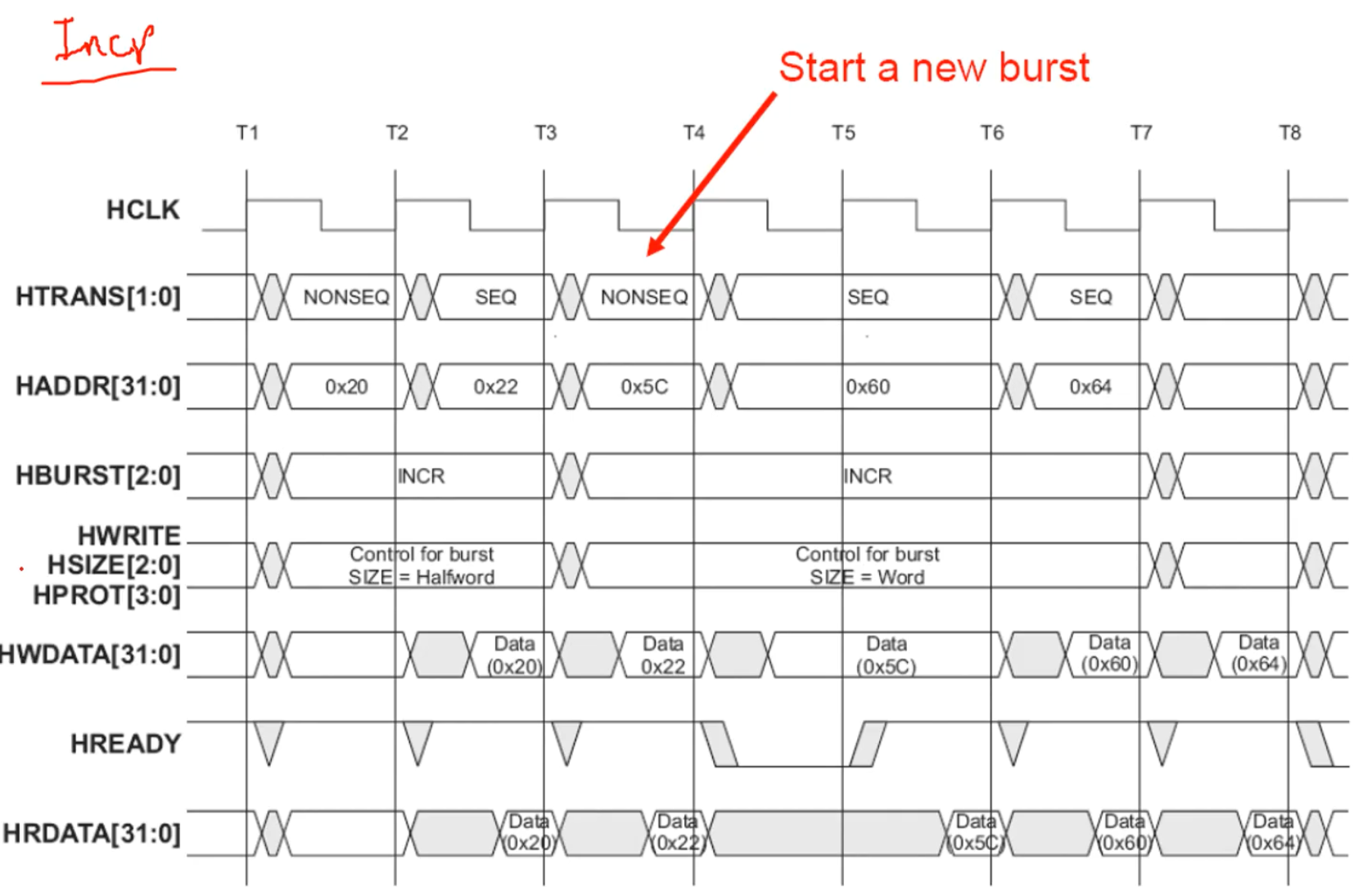

- 001 Incrementing transfer with unspecified length (INCR ):一直传输下去,且地址累加的

- 4-beat:连续传四次,且地址累加的

- 8-beat:连续传八次,且地址累加的

- 16-beat:连续传十六次,且地址累加的

第一个cycle就输出了burst=4-beats

传输类型

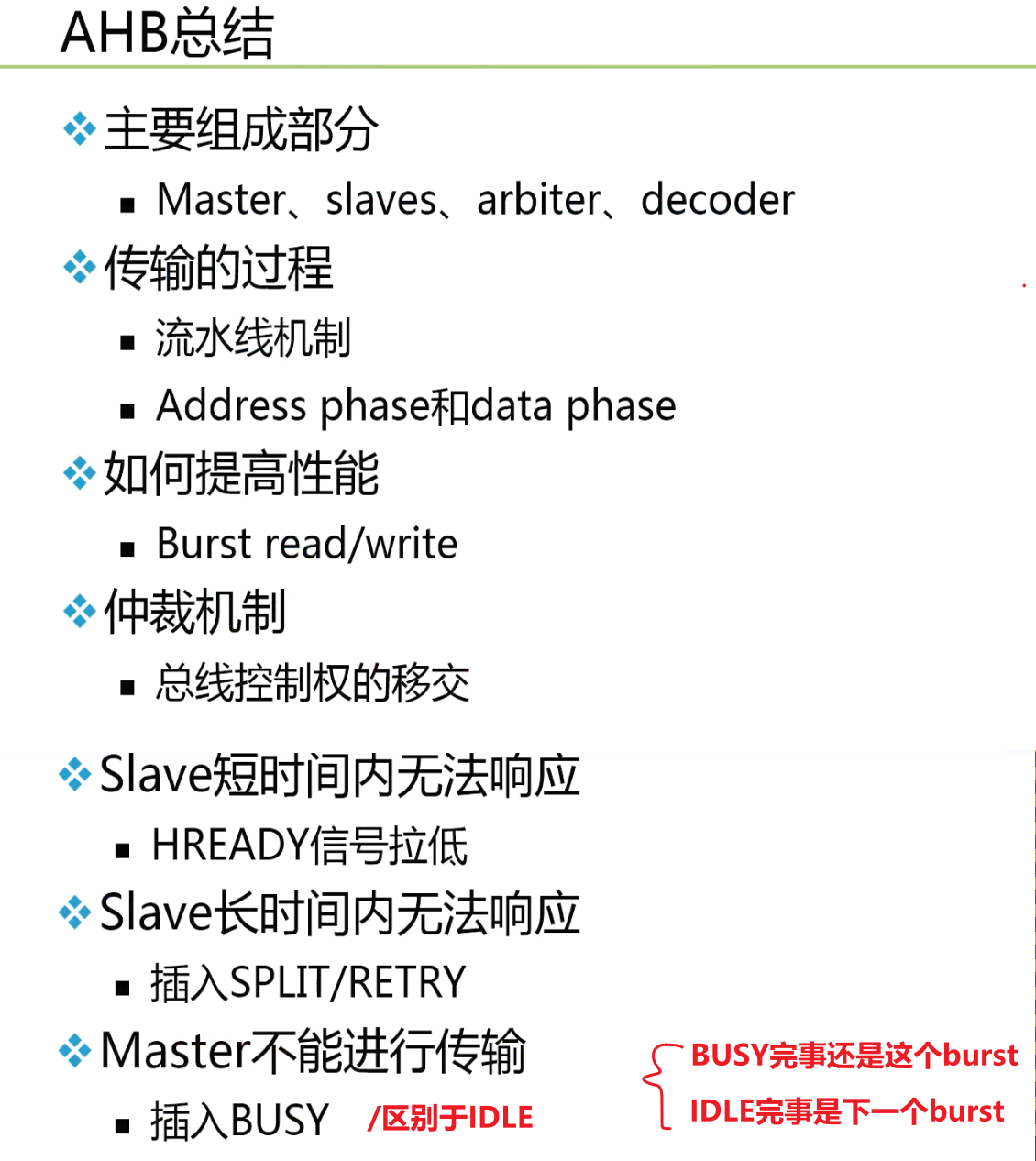

没准备好的几种情况

- If slave not ready, then HREADY=0

- If master is not ready, then HTRANS 插入IDEL 或者 BUSY

HTRANS[1 : 0] 当前传输的状态

- IDLE、 BUSY、NONSEQ、SEQ

- 00 : IDLE

- 主设备占用总线,但没进行传输

- 两次burst传输中间主设备发IDLE

- 01: BUSY

- 主设备占用总线,但是在burst传输过程中还没有准备好进行下一次传输

- 一次burst传输中间主设备发BUSY

- 10:NONSEQ

- 表明一次单个数据的传输

- 或者一次burst传输的第一个数据

- 地址和控制信号与上一次传输无关

- 11:SEQ

- 表明burst传输接下来的数据

- 地址和上一次传输的地址是相关的

传输类型举例

其他AHB控制信号

HWRITE

- 高电平:写

- 低电平:读

HSIZE[2:0]

- 000:8bits

- 001:16bits

- 010:32bits

- 011:64bits

- 100:128bits

- 101:256bits

- 110:512bits

- 111:1024bits

- 最大值受总线的配置所限制

- 通常使用32bits (010)

HPROT [3 : 0]

- HPROT[0] : OPCODE/DATA

- HPROT[1] : USER/PRIVILGED

- HPROT[2] : Bufferable/Non-Bufferable

- HPROT[3] : Cacheable/Non-Cacheable

控制信号小结:

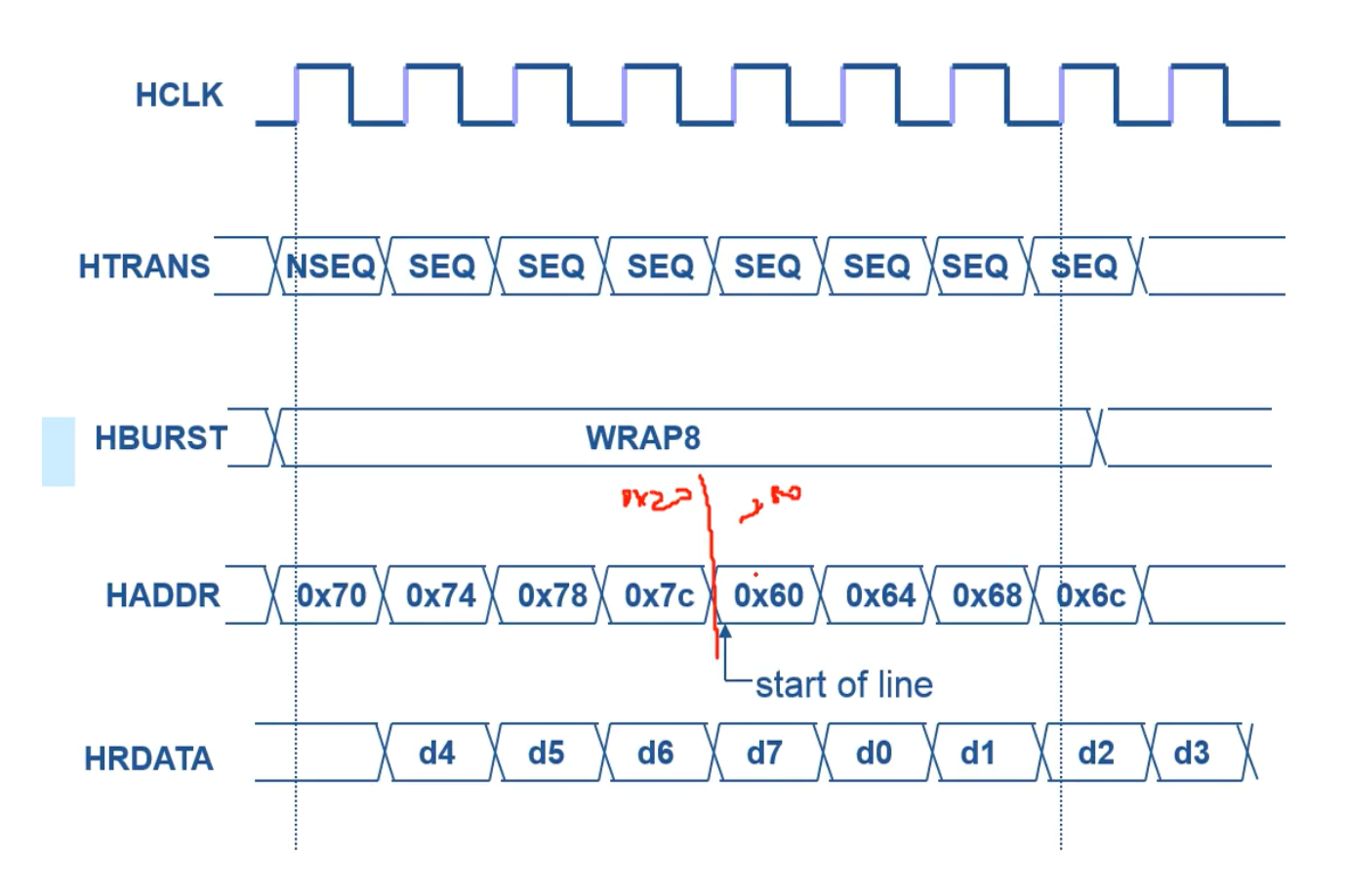

- WRAP是回环

BURST 传输

1)BURST的不同类型

AHB Burst操作

4beat、8beat、16beat、 单个字节传输、未定义长度的传输

支持incrementing和wrapping两种burst传输

Incrementing burst

- 地址是上一次的传输地址加1

Wrapping burst

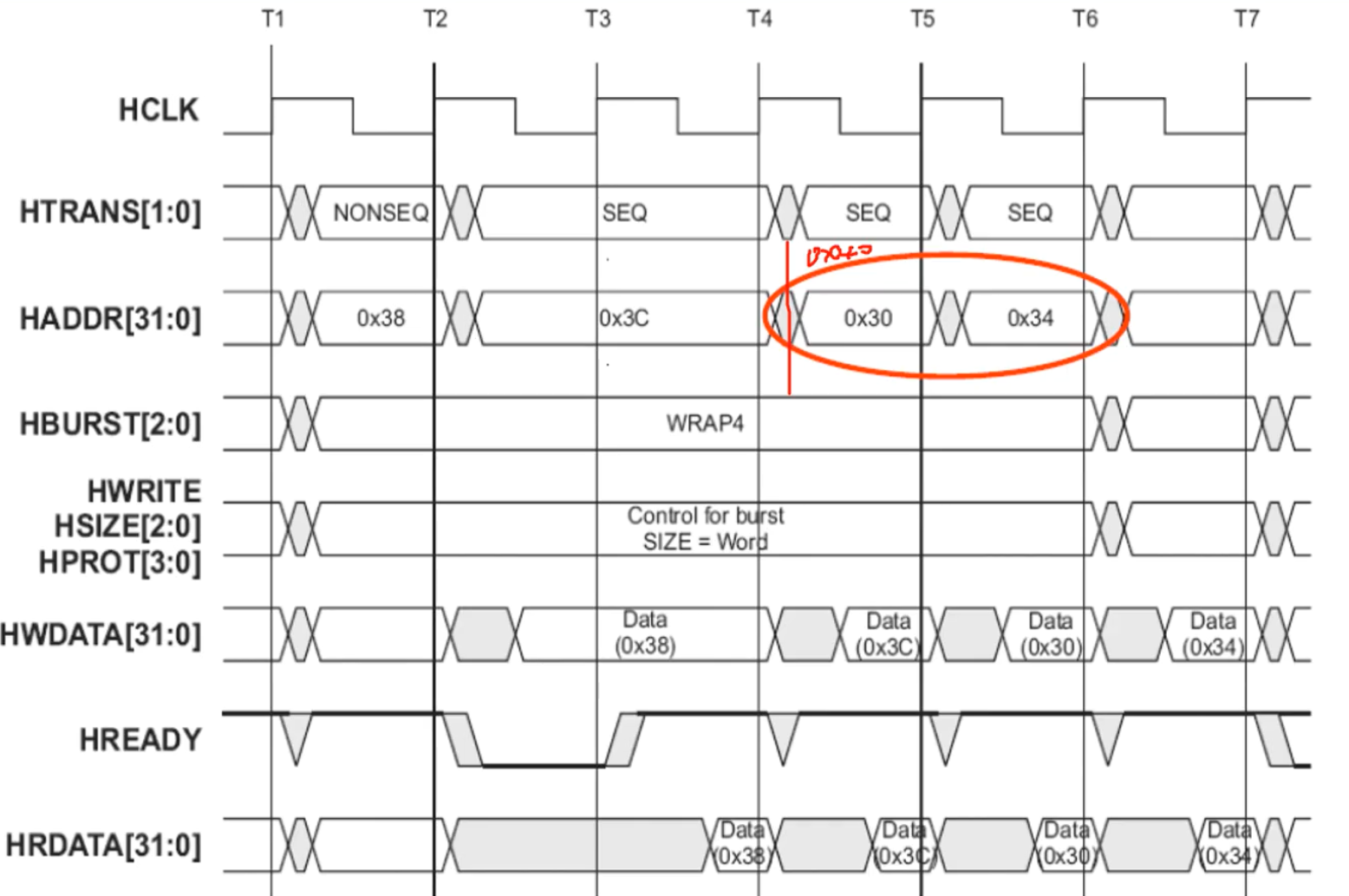

- 例: 4beat的wrapping burst 字传输 ( 4byte) :

0x34-> 0x38 -> 0x3C -> 0x30 - 应用场合: Cache填充

Wrapping burst,到达n-beat的n时反弹

例如:

- 4-beats:0x34 -> 0x38 -> 0x3C -> 0x30

- 4-beats:0x30 -> 0x34 -> 0x38 -> 0x3C

- 8-beats:0x34 -> 0x38 -> 0x3C -> 0x20 -> 0x24 -> 0x28 -> 0x2C -> 0x30

BURST地址计算示例

- 跟HSIZE和HBURST有关

2)几种Burst实例

INCR8 Burst 波形图示例

WRAP8 Burst 波形图示例

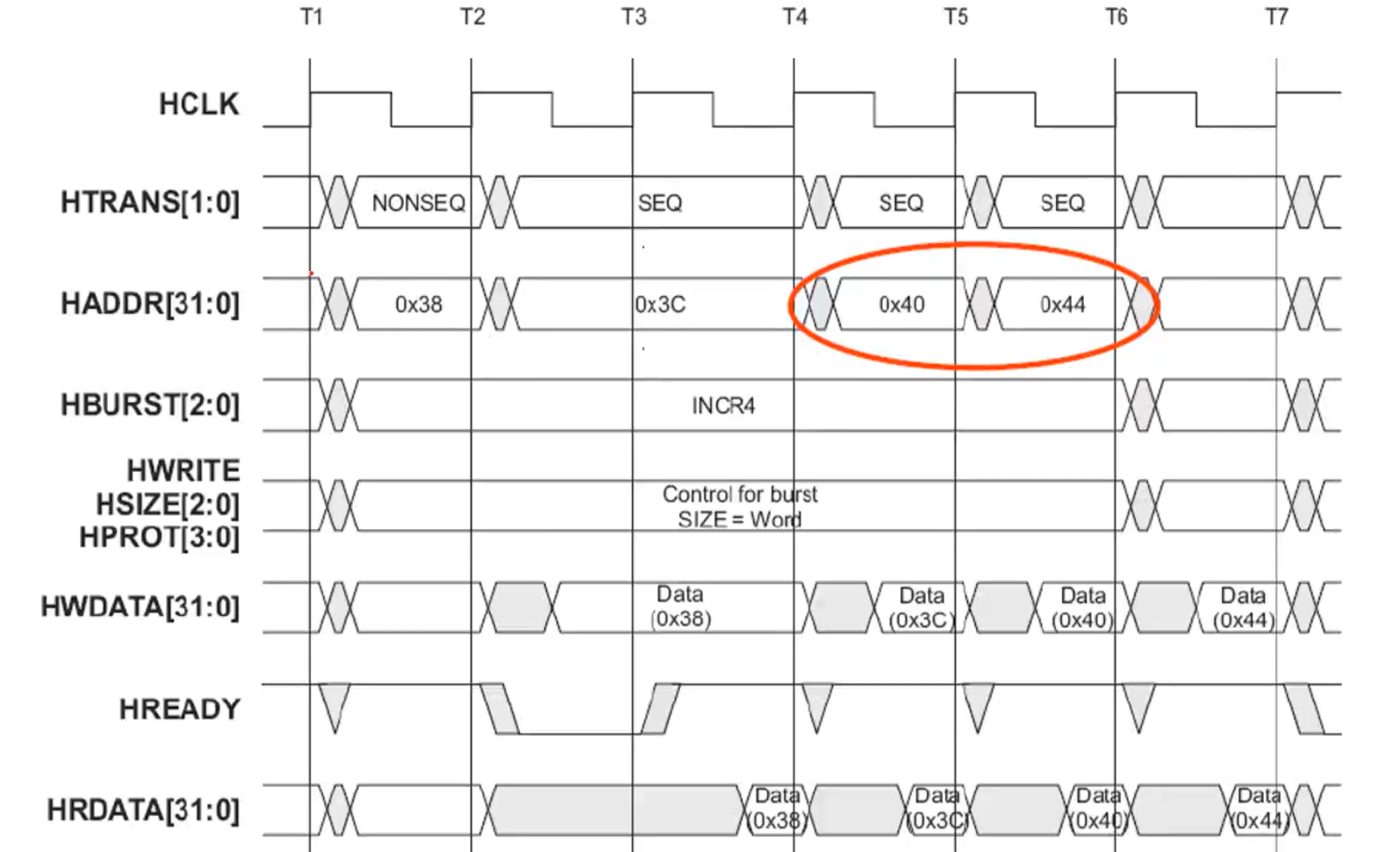

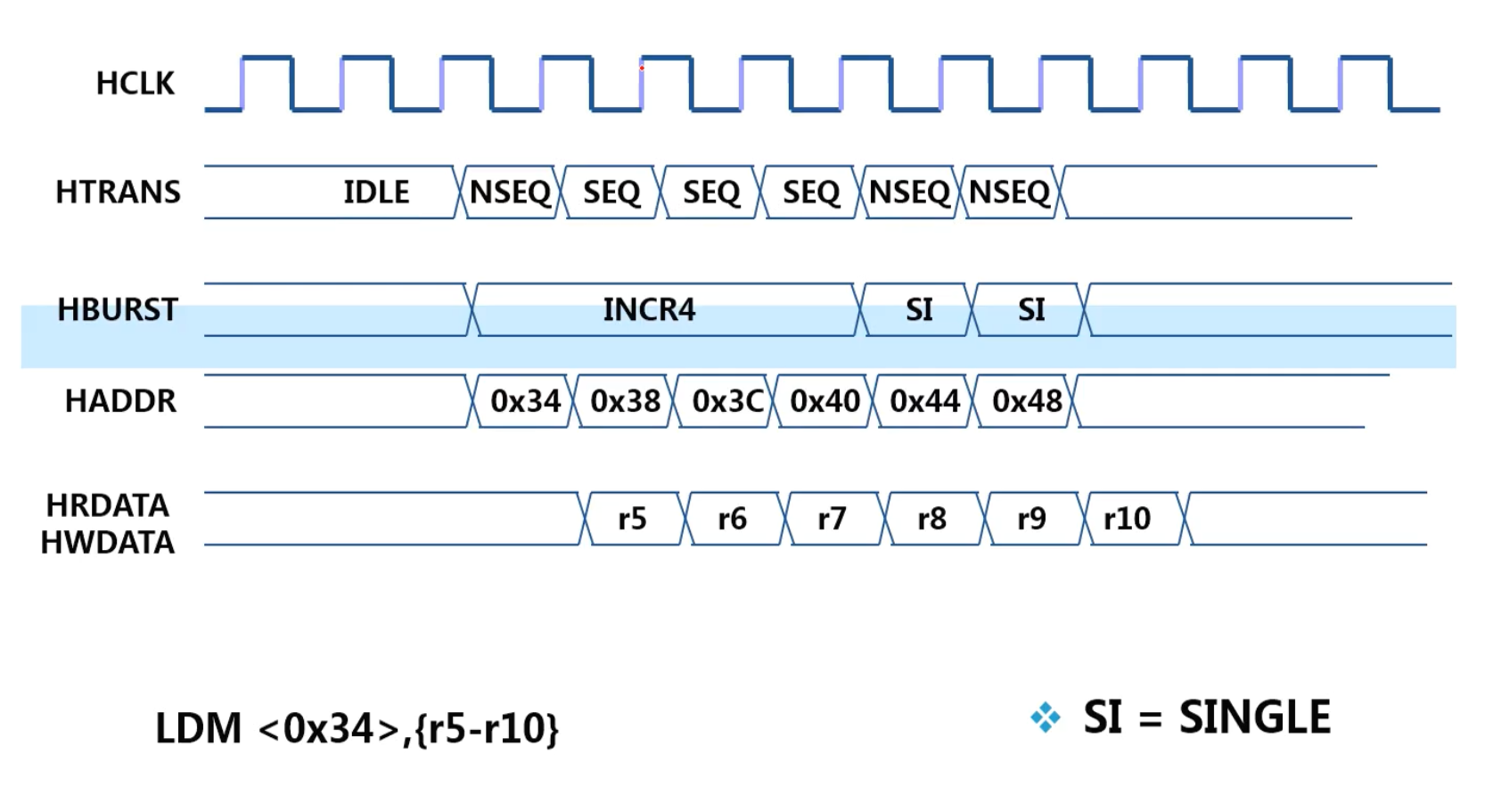

INCR4 Burst 波形图(全)

- 使用了pipeline,数据在地址后

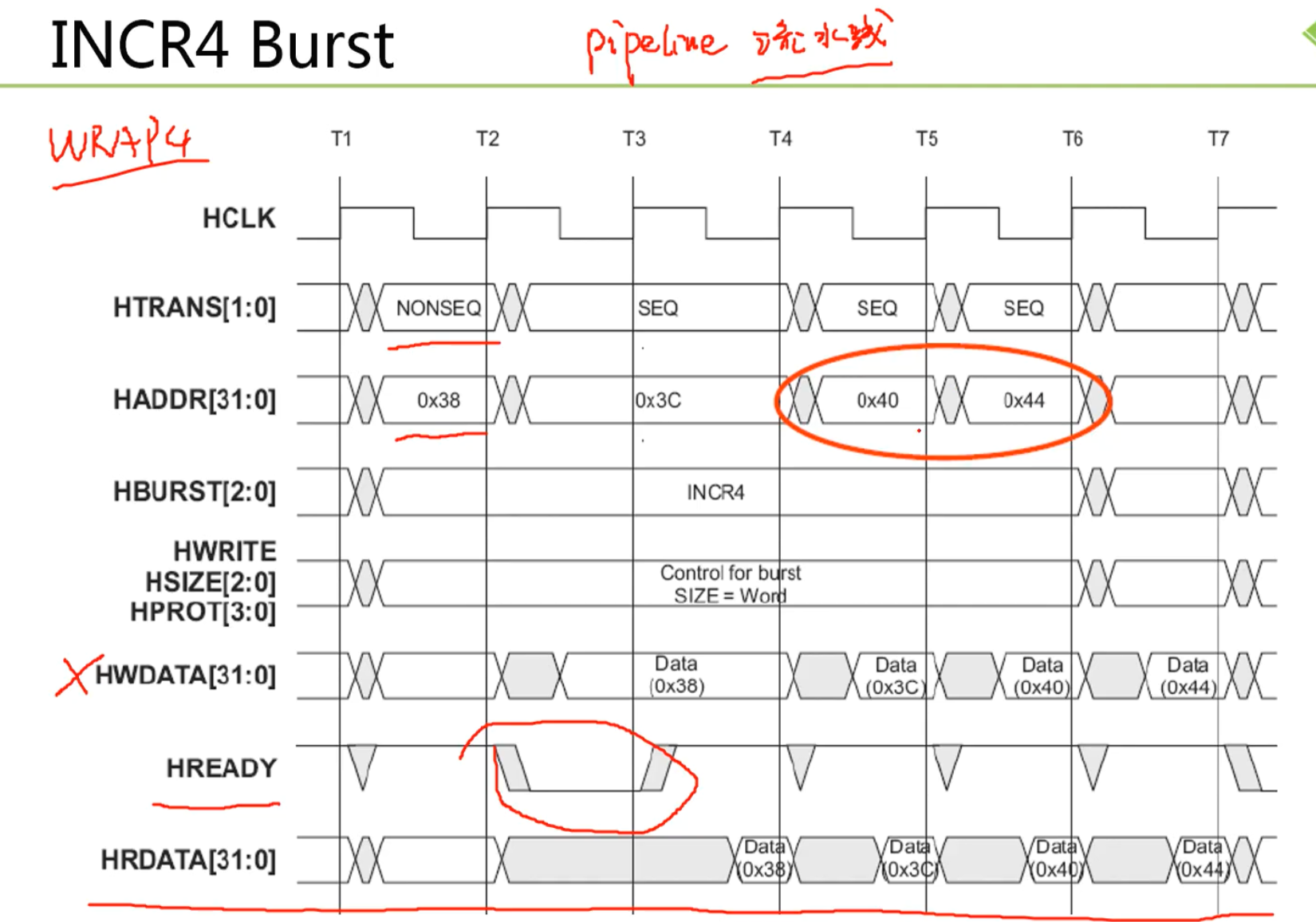

WRAP4 Burst

未定义长度的Burst(普通的INCR)

LDM AHB Activity(交换的传输)

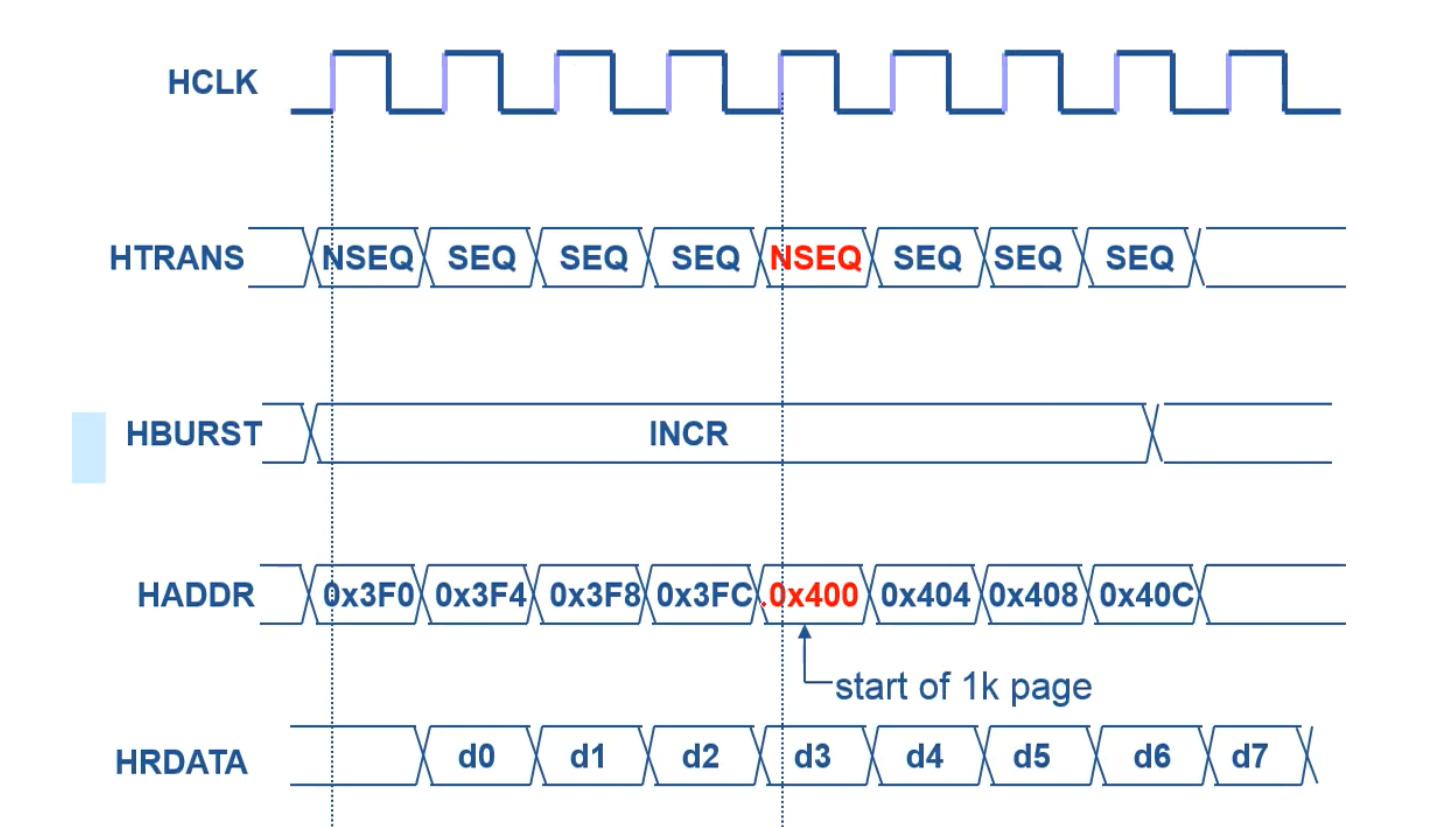

3)1K的边界

Burst传输不能穿越1K边界(1K=1x10^10),解决方法:下一个地址是0x400时,来一个NONSEQ就可以了

- 一个从设备最小的地址间隙是1KB

- NONSEQ -> SEQ -> 1KB Boundary ->

- NONSEO -> SEQ

主设备不能试图开始一个可能穿越1K边界的固定长度的incrementing burst传输

波形图如下所示:

HSELx地址译码

1)概述

- HSELx :选择从设备

- 指出由主设备所选择的从设备

- 由地址译码器来提供选择信号

- 一个从设备应该至少占用1KB的存储空间

- End - Start + 1 >= 100

- 需要一个额外的缺省从设备来映射其他的存储地址

2)从设备响应的要点

所访问的从设备必须响应这次传输

从设备可能返回的响应:

- 完成文次传输

- 插入等待状态(HREADY信号)

- 发出错误信号表示这次传输失败

- 延迟传输,便得总线可用于其他传输(split)

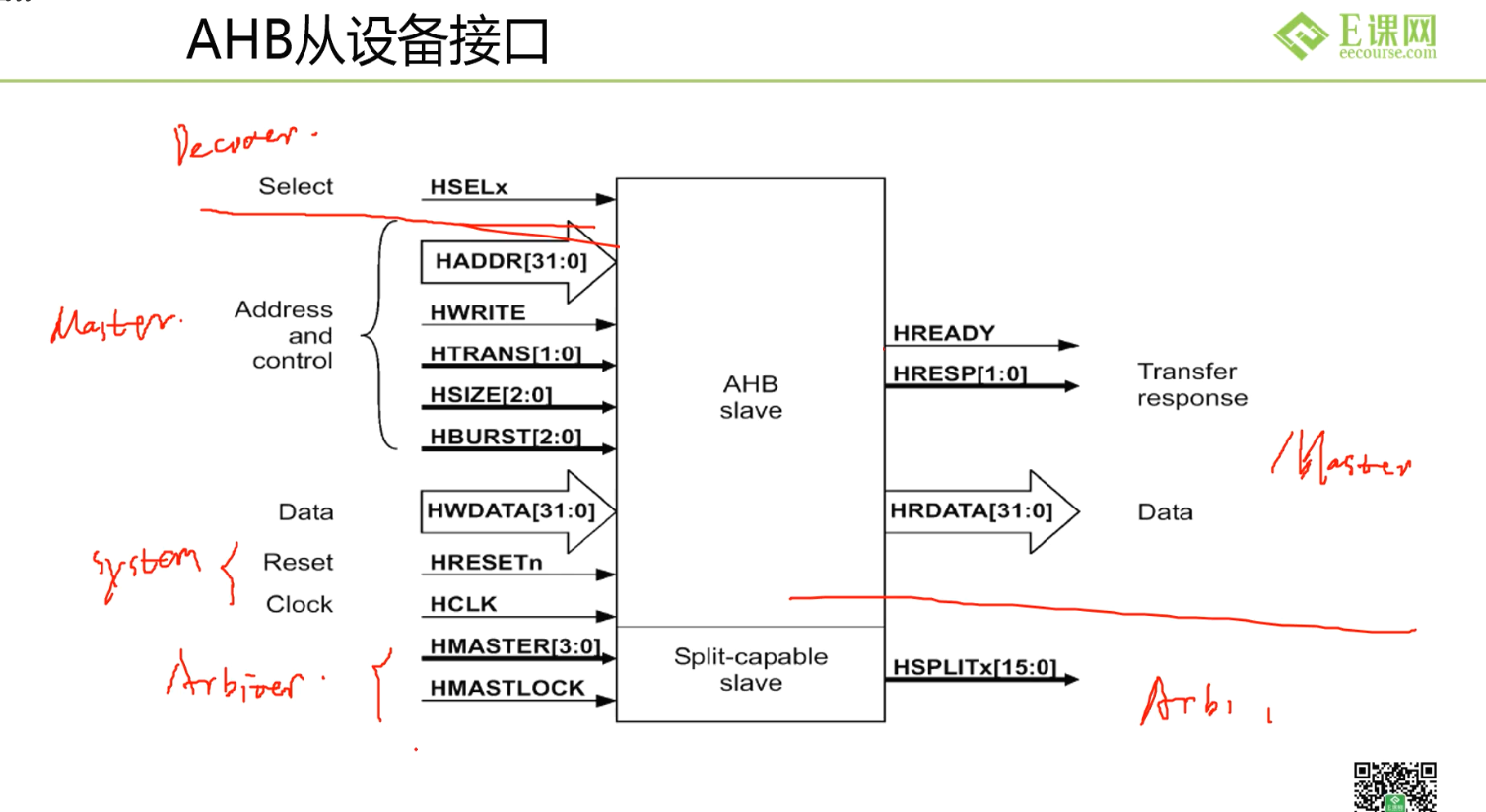

3)从设备响应信号

响应信号:

- HREADY : transfer done

- HRESP[1 : 0] : transfer response

- 00:OKAY 成功

- 01:ERROR 失败

- 10:RETRY 传输未完成,请求主设备重新开始一个传输

- 11:SPLIT 传输未完成,请求主设备分离一次传输(可以理解为让master过一会retry而不是立刻retry)

响应周期:

- HRESP[1 : 0]

- OKAY 单周期响应

- ERROR 两周期响应

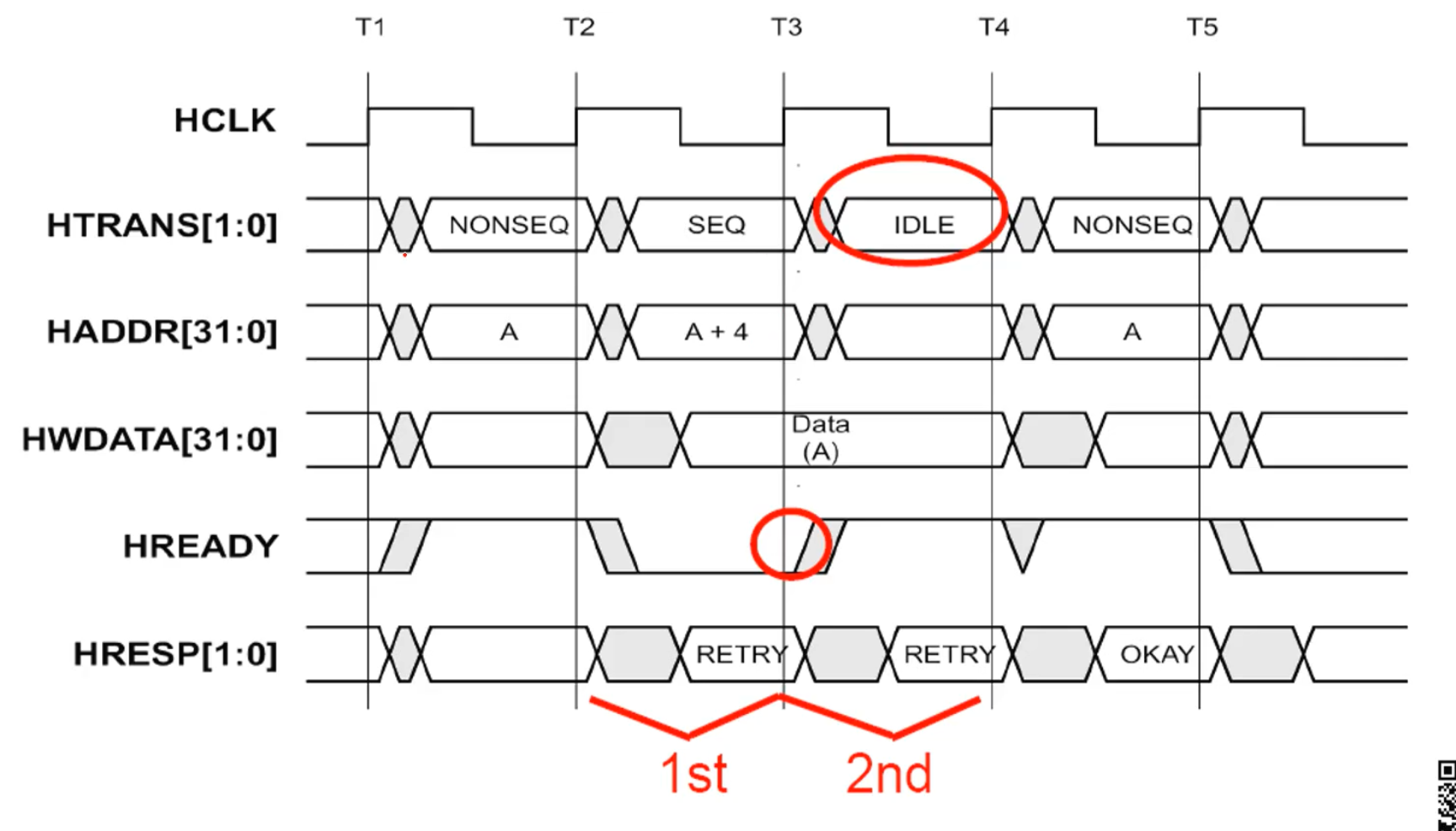

- RETRY 两周期响应

- SPLIT 两周期响应

- 总线的流水特性需要从设备两个周期的响应。可以使得主设备有足够的时间处理下一次传输

4)响应示例(使用到了IDLE)

RETRY响应

5)RETRY与SPLIT的不同

主要区别在于仲裁的方式

- RETRY:arbiter会继续使用通常的优先级

- SPLIT:arbiter会调整优先级方案以便其他请求总线的主设备可以访问总线

总线主设备应该用同样的方式处理RETRY响应和SPLIT响应

注意:在实现的时候SPLIT只会影响arbiter,在其他接口的实现上并无额外开销

数据总线

1)概述

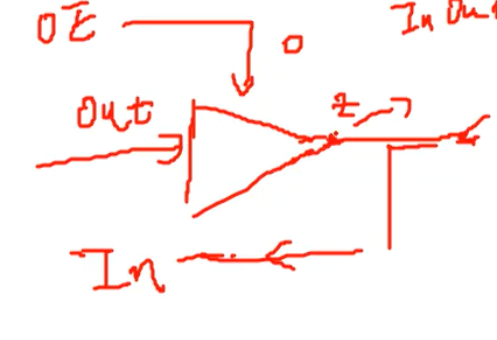

不是三态总线,读总线和写总线是分开的

三态:0 1 Z

SoC什么时候会需要高阻态?

答:PAD的时候,使用inout的PAD时候

印第安序

- 在AMBA协议中没有定义,自己定义

- 主设备和从设备应该采用同样的印第安序

- 不支持动态印第安序

对于IP设计,只有应用面比较广泛的应用程序才支持两种印第安序

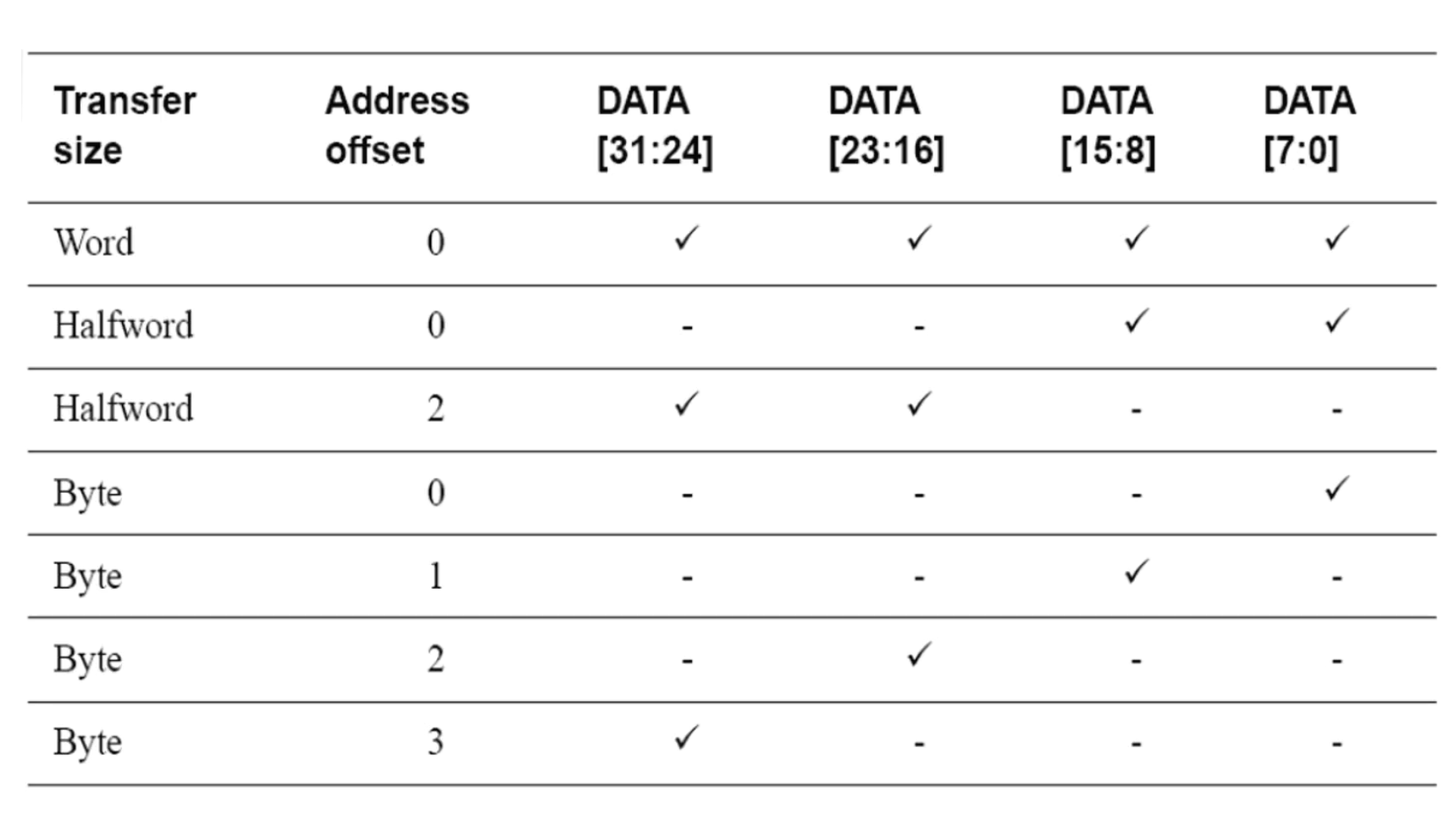

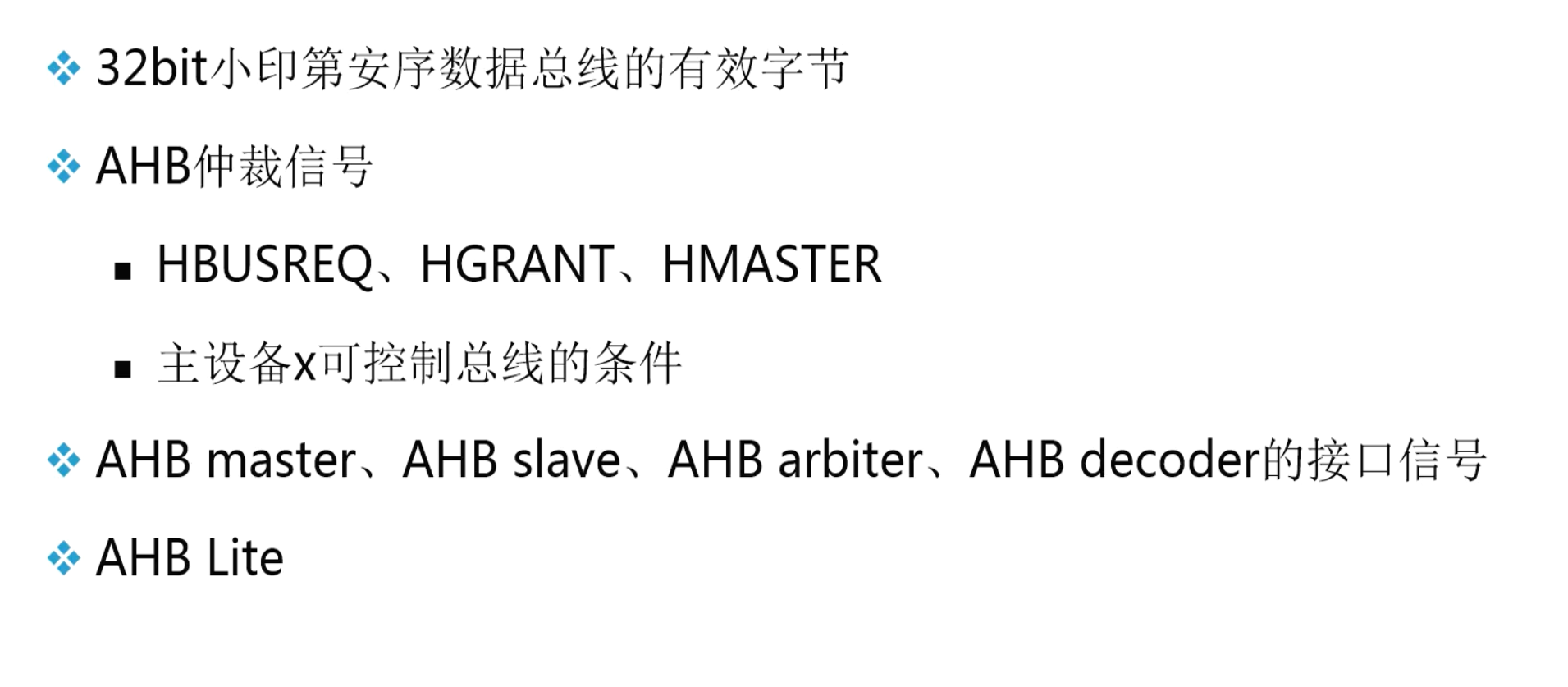

2)32bit小印第安数据总线的有效字节

- Word -> HSIZE=2

- Halfword -> HSIZE=1

- Byte -> HSIZE=0

大印第安序反过来,高位有效

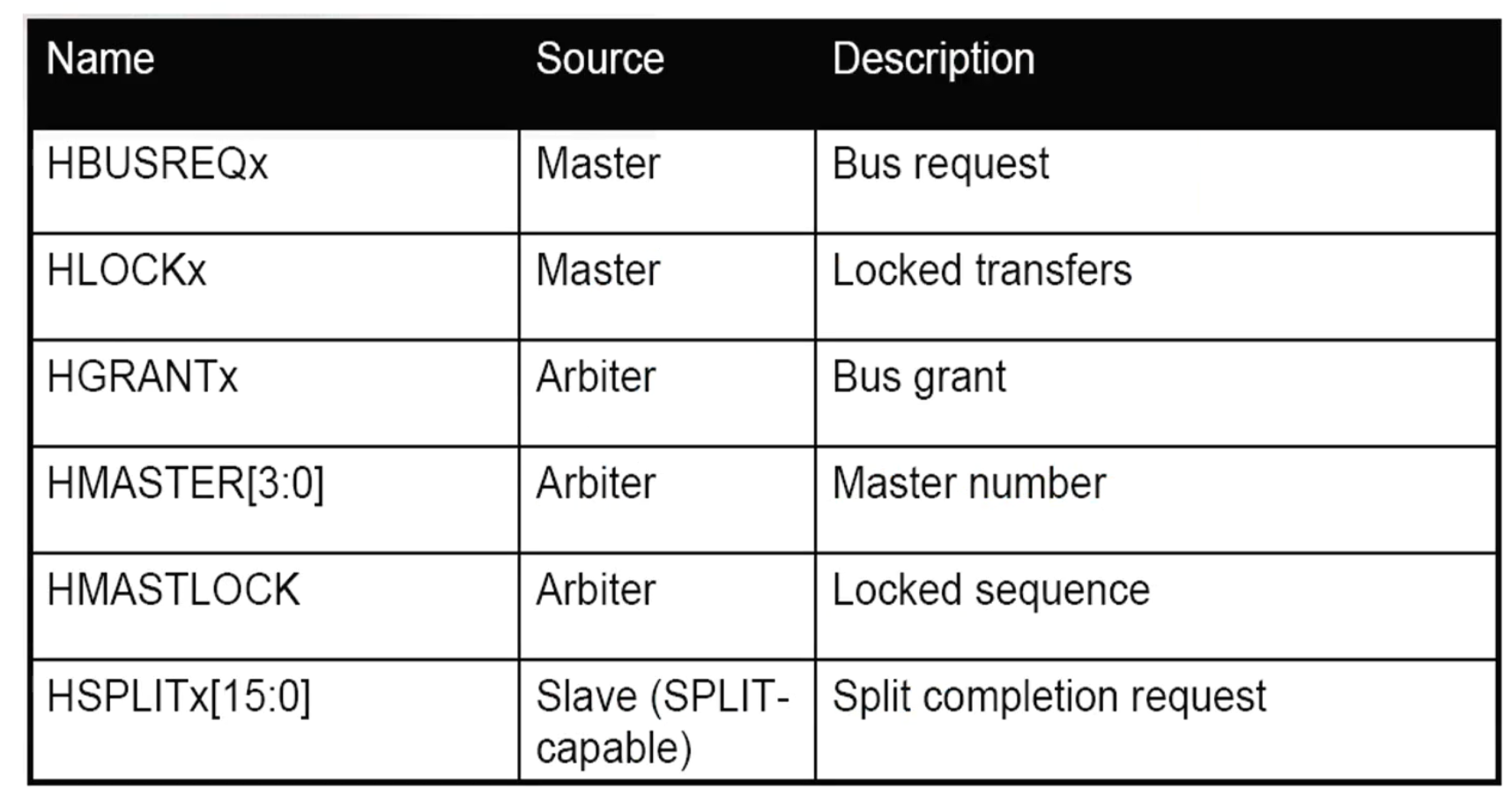

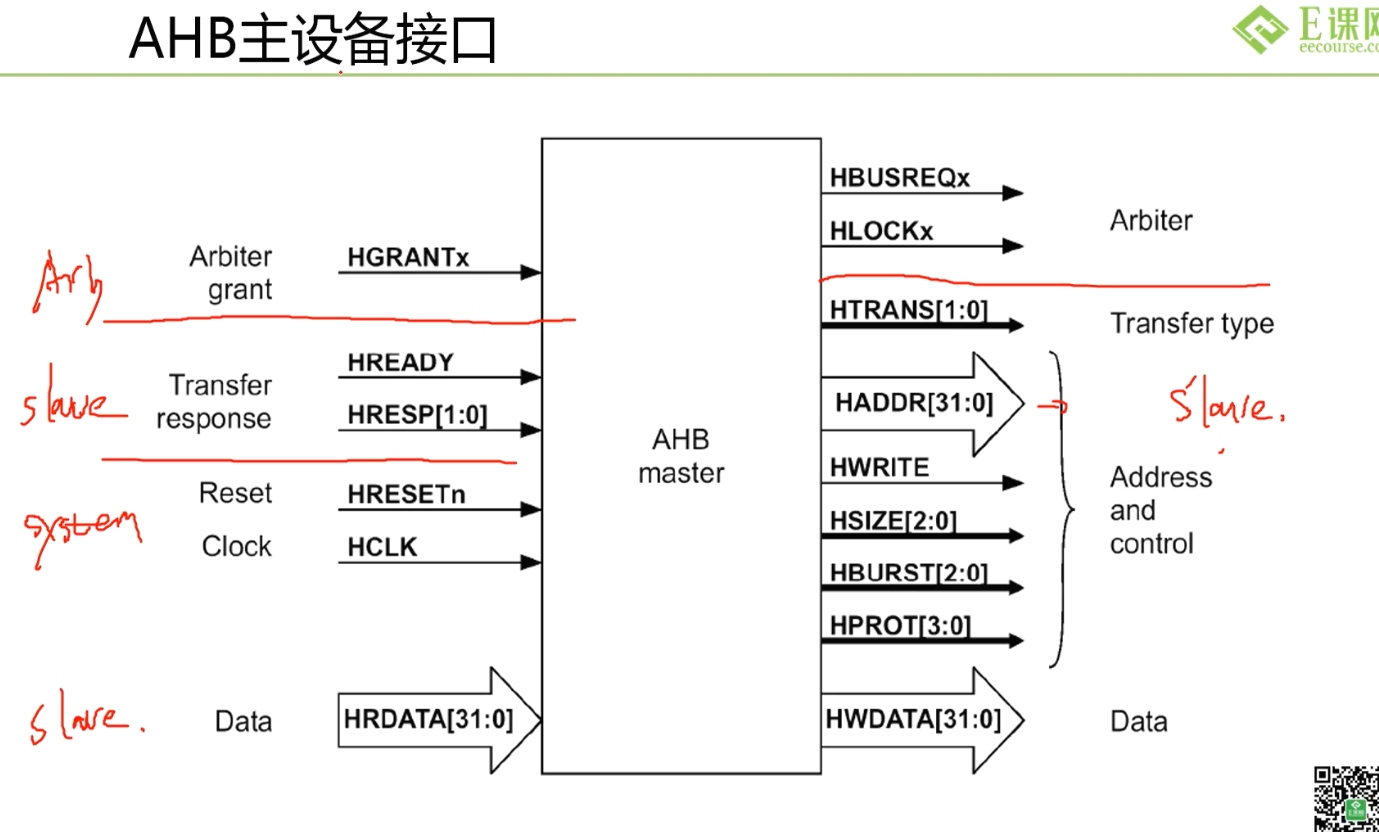

AHB仲裁信号

1)仲裁信号

HBUSREQ

- 总线请求

HLOCKx

- 高电平:主设备请求锁定总线

- 只有HBUSREQ拿掉arbiter才能停止GNT

HGRANTx

- 指出主设备x可访问总线

- 主设备x什么时候可以控制总线: HGRANTx=1且HREADY=1

补充:

slave会有一个hready_in 和 hready_out,hready_in是总线上所有hready_out的与信号(可包括自己),只有hready=1时slave才会工作

HMASTER[3 : 0]

- 指出哪个主设备正在进行传输

- 最多支持16个

HMASTLOCK

- 指出主设备正在进行一次锁定传输

HSPLITx[15 : 0]

- 从设备用这个信号告诉仲裁器哪个主设备允许重新尝试一次split传输

- 每一位对应一个主设备

- x表示哪一个slave

- [15 : 0]表示哪一个master

- 由slave给arbiter的split信号更可靠,因此使用这种数据方案

2)仲裁举例

没有等待的状态的grant

有等待状态

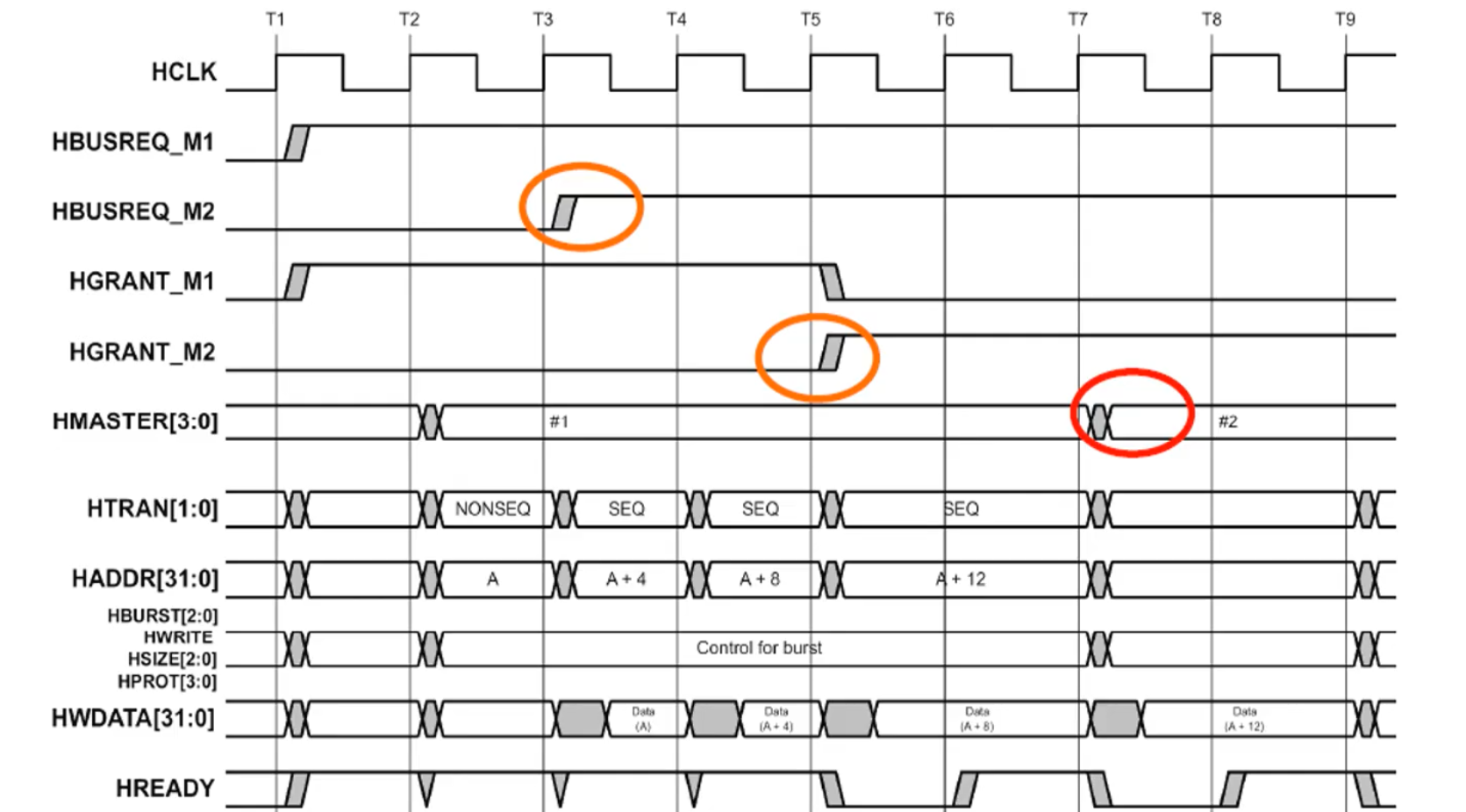

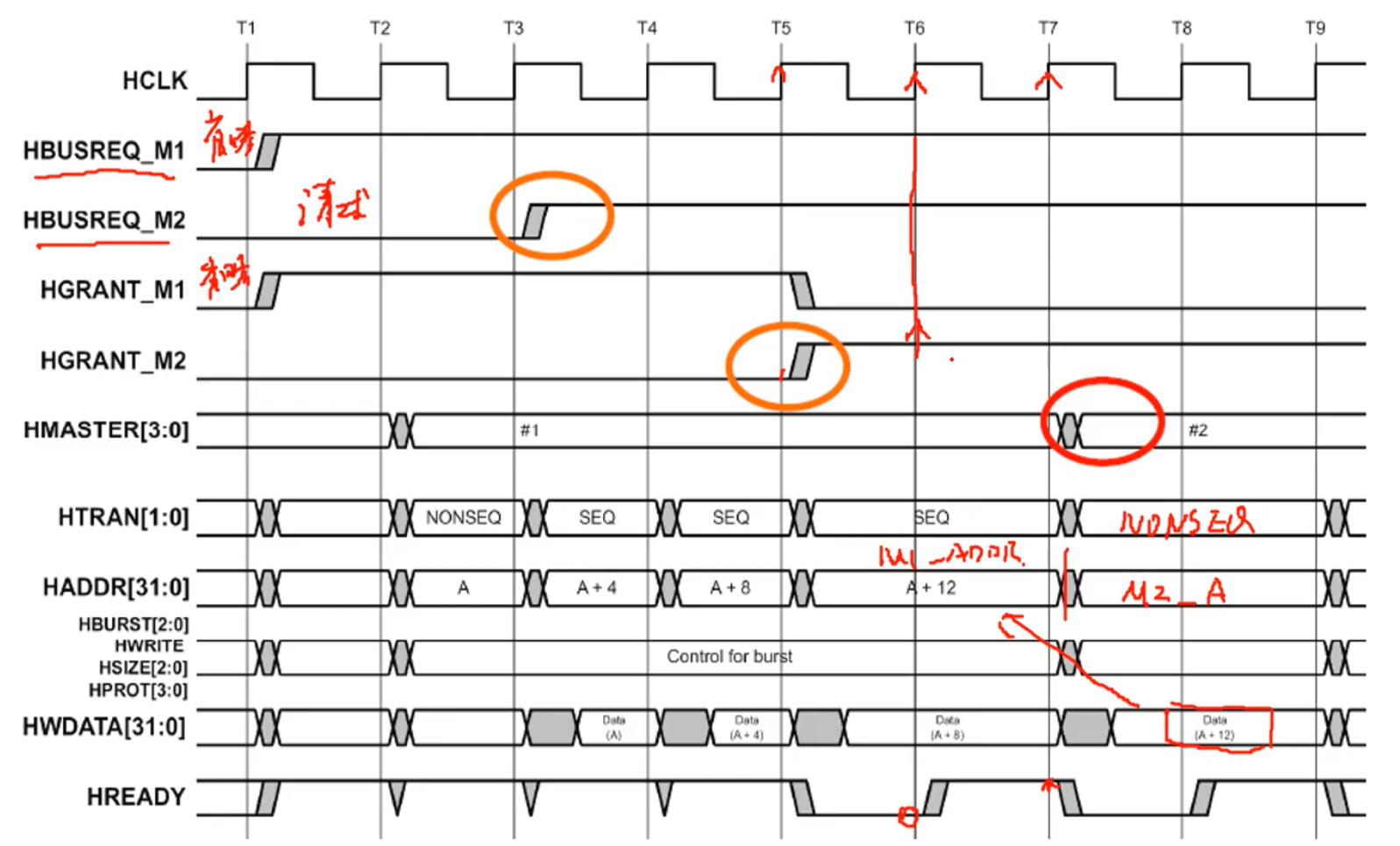

Burst传输之后移交总线

注意!由于pipeline的原因,失去GRANT后还能再发一个地址+数据

- 如果你是M1的设计者需要考虑这点

3)主设备GRANT信号

- HADDR to all slaves最后给了

- Decode进行解码

- 从设备

4)注意(IDLE)

- 对于固定长度的burst传输,不必持续请求总线

- 对于未定义长度的burst传输,主设备应该持续送出HBUSREQ信号,直到开始最后一次传输

- 如果没有主设备请求总线,则给缺省主设备GRANT信号,且HTRANS=IDLE

- 建议主设备在锁定总线传输结束之后插入IDLE传输,以重新仲裁优先级

Split传输过程

- 由主设备开始传输

- 如果从设备需要多个周期才能获取数据,则从设备给出一个SPLIT传输响应。从设备记录主设备号:HMASTER。接着仲裁器改变主设备的优先级

- 仲裁器grant其他的主设备,总线主设备移交

- 当从设备准备结束本次传输,将设置给仲裁器的HSPLITx信号的相应位

- 仲裁器恢复优先级

- 仲裁器grant主设备,这样主设备可以重新开始传输

- 结束

防止Deadlock(死锁)

- 当多个不同的主设备试图访问同一个从设备,这个从设备发出了SPLIT或RETRY信号,这时很可能发生deadlock

- 从设备最多可以接收系统中16个主设备的请求。只需要记录主设备号(忽略地址和控制信号)

- 给出RETRY响应的从设备在某一时刻只能由一个主设备访问

- 可以使用一些硬件保护机制,比如ERROR

AHB 设备接口

AHB-Master

AHB-Slave

AHB-Arbit

AHB-Decoder

叠加在一起的AMBA系统

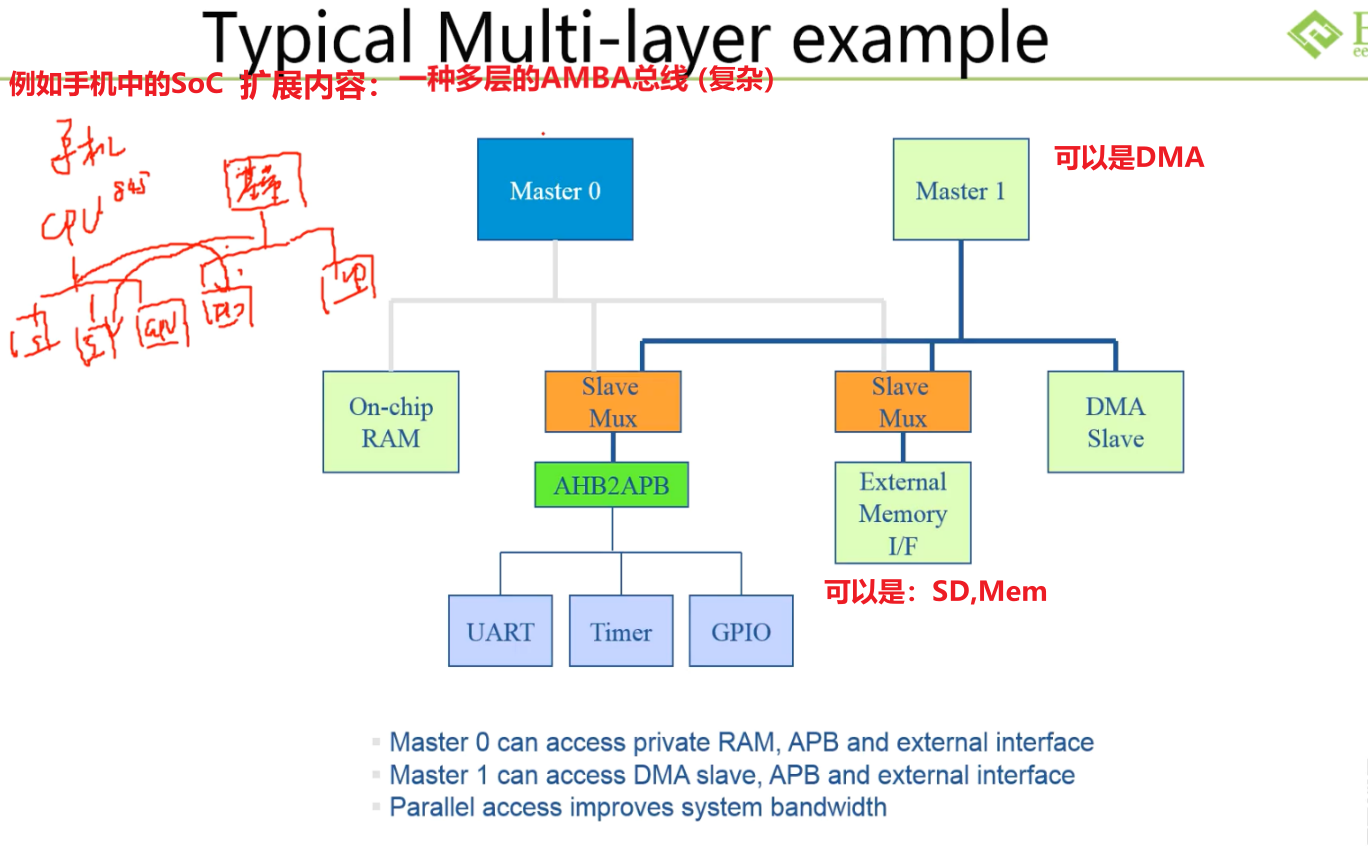

AHB-多层

- 重叠部分的Slave有两个AMBA接口

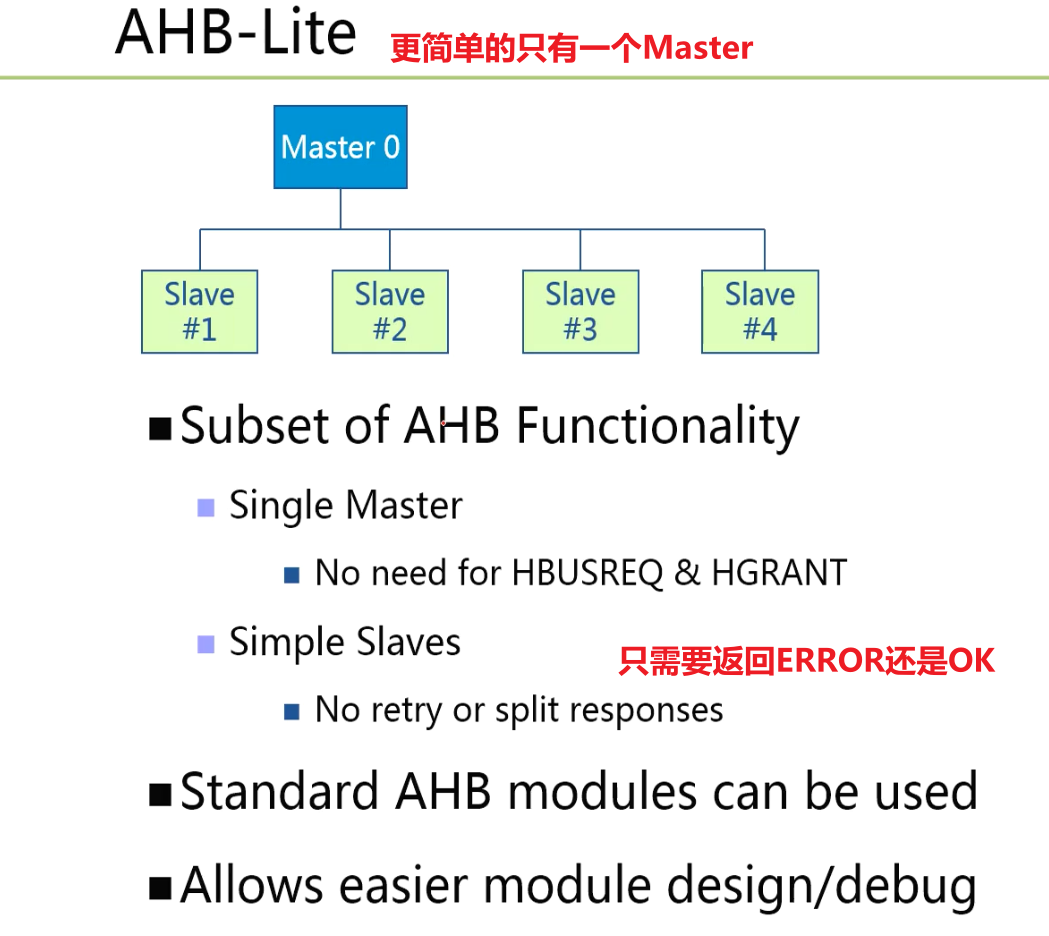

AHB-Lite

AHB-总结

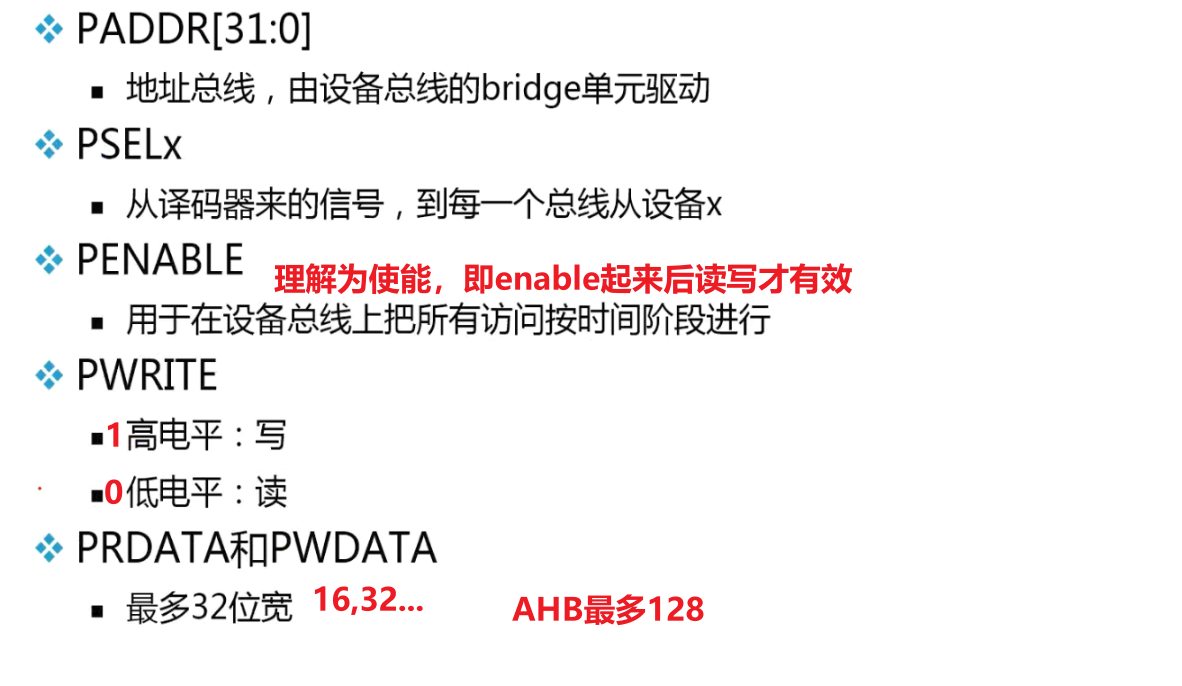

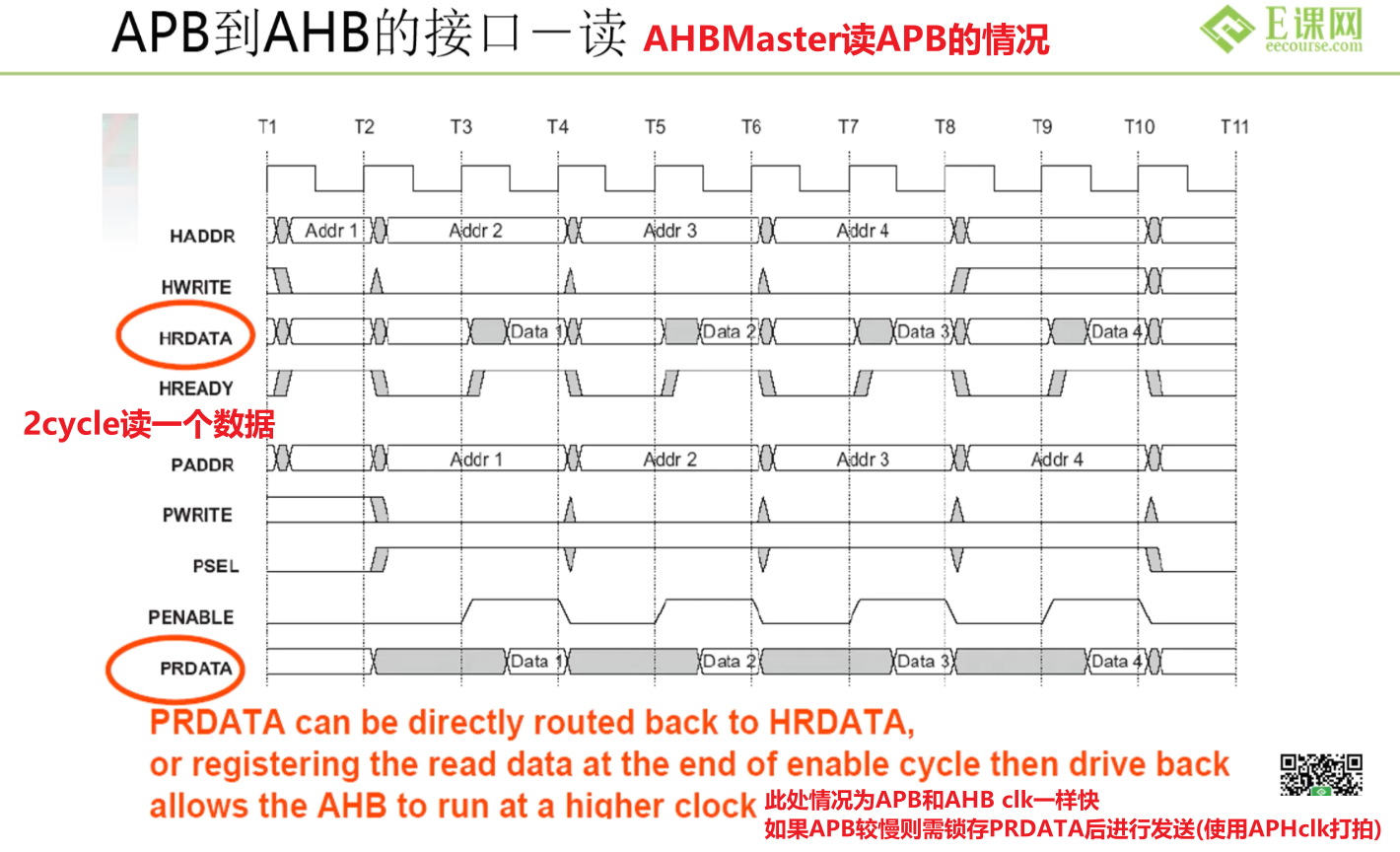

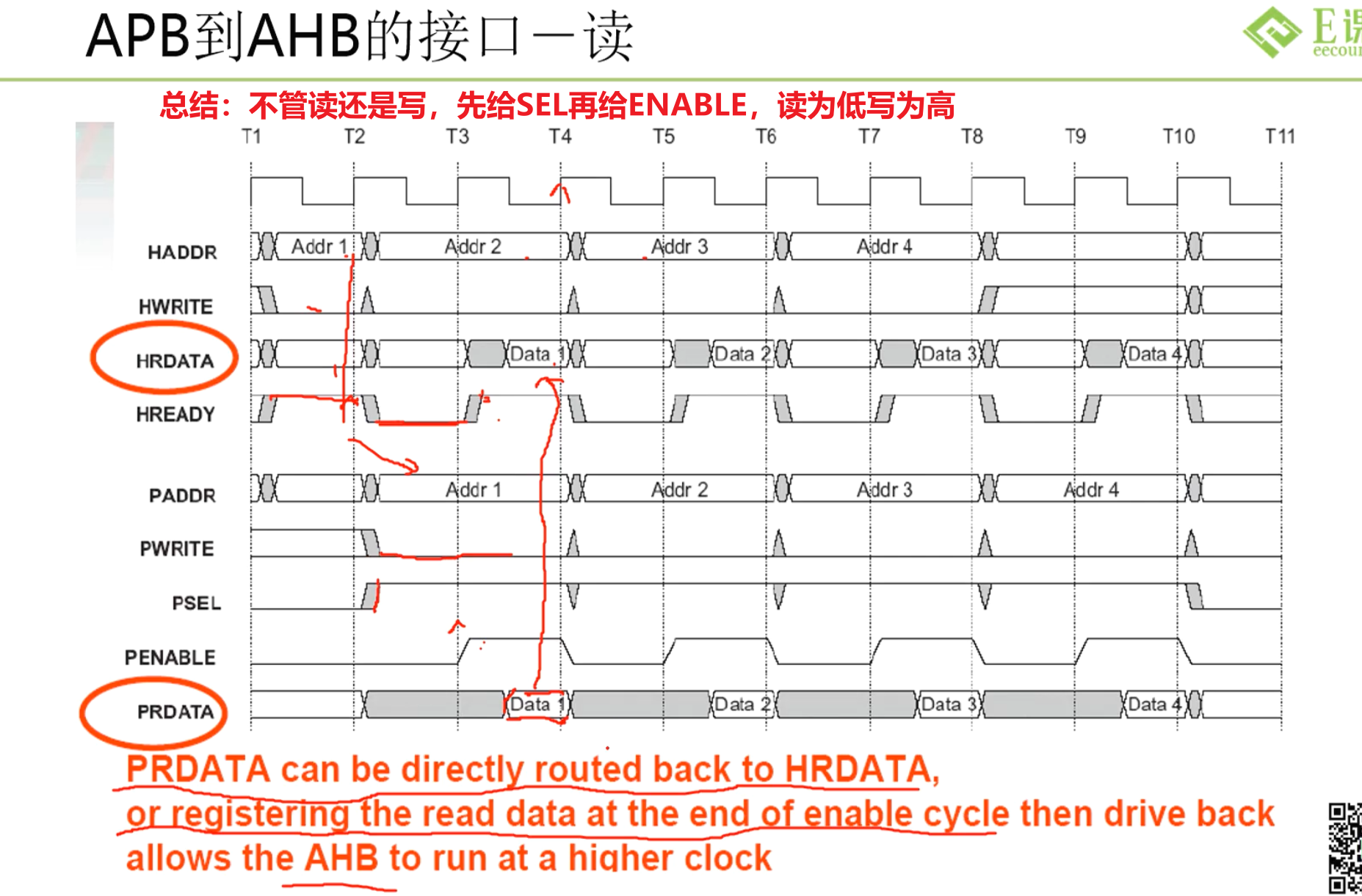

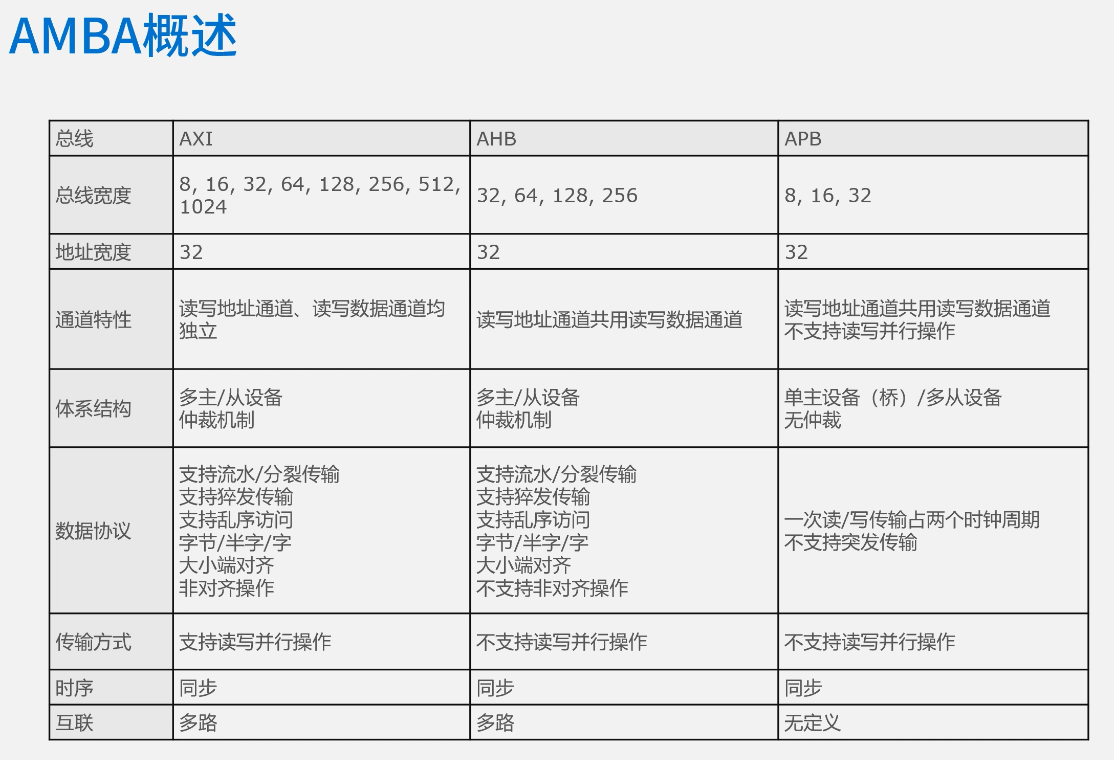

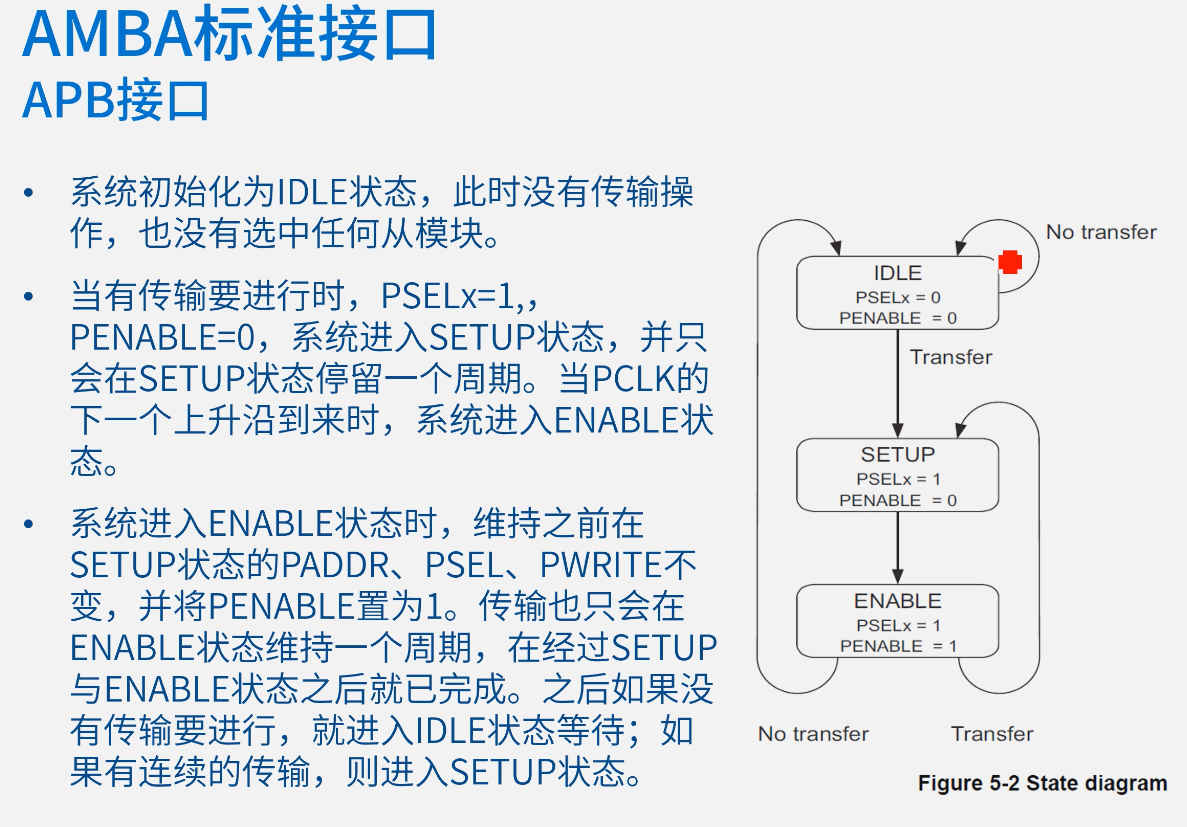

3 APB

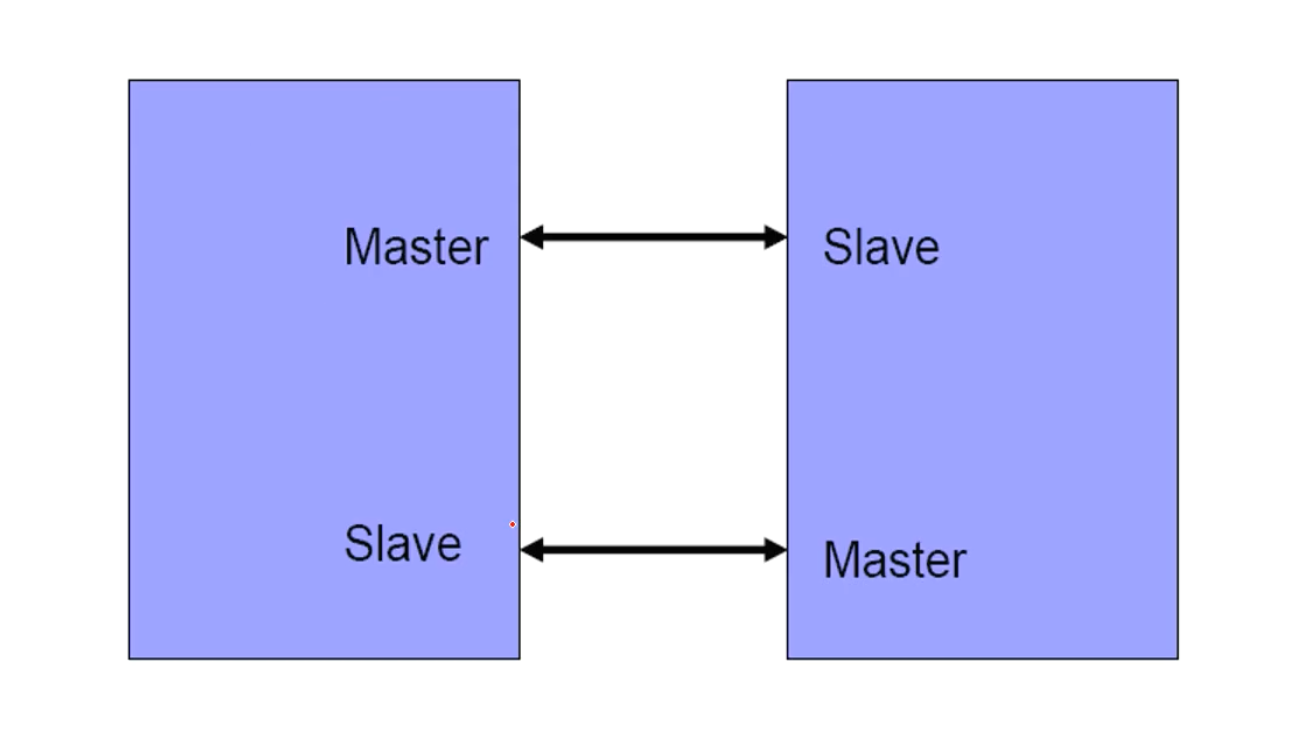

4 不同IP之间的互联

5 Review

路科

141-AMBA标准接口

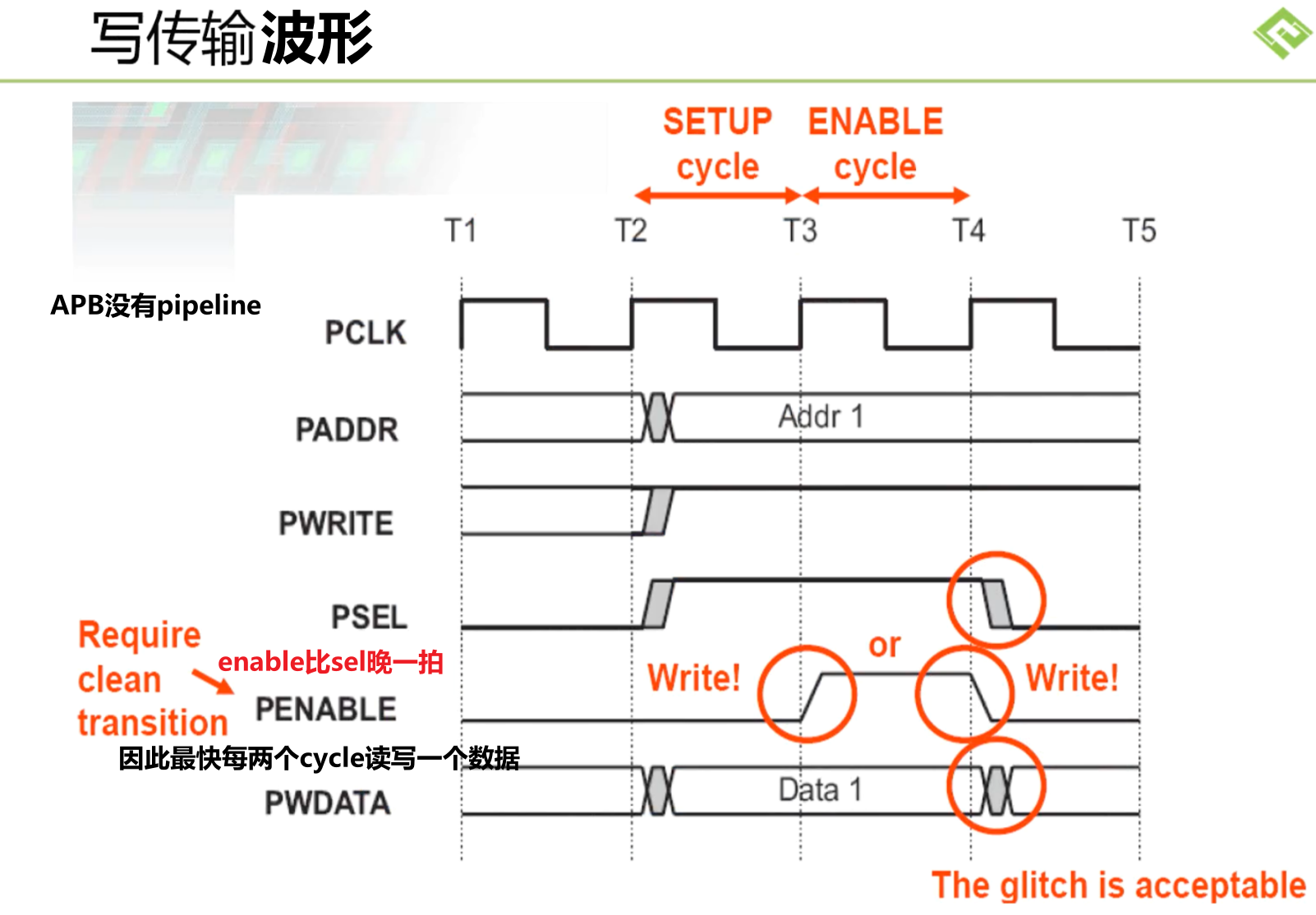

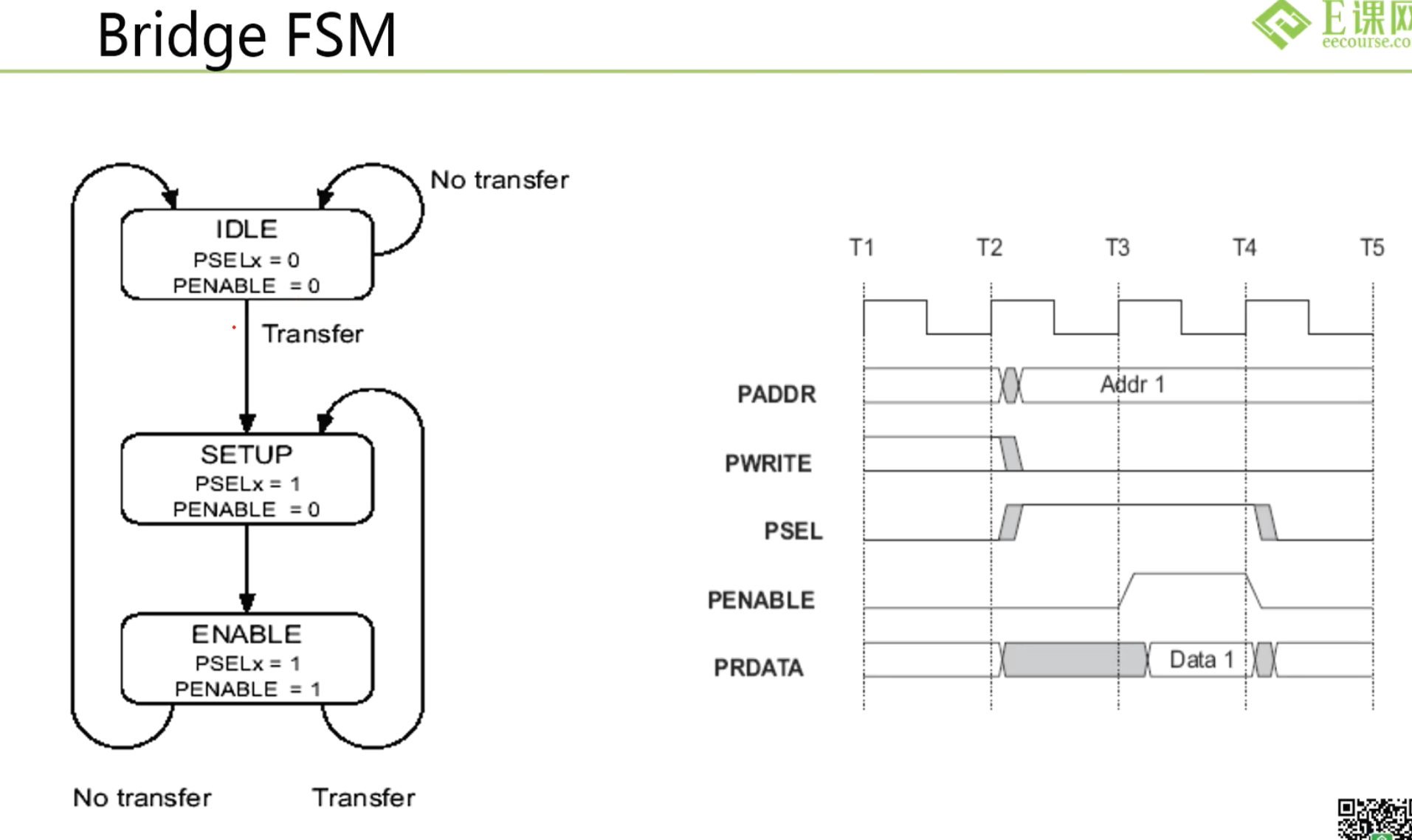

APB补充——一次事务结束不会跳变为了省电

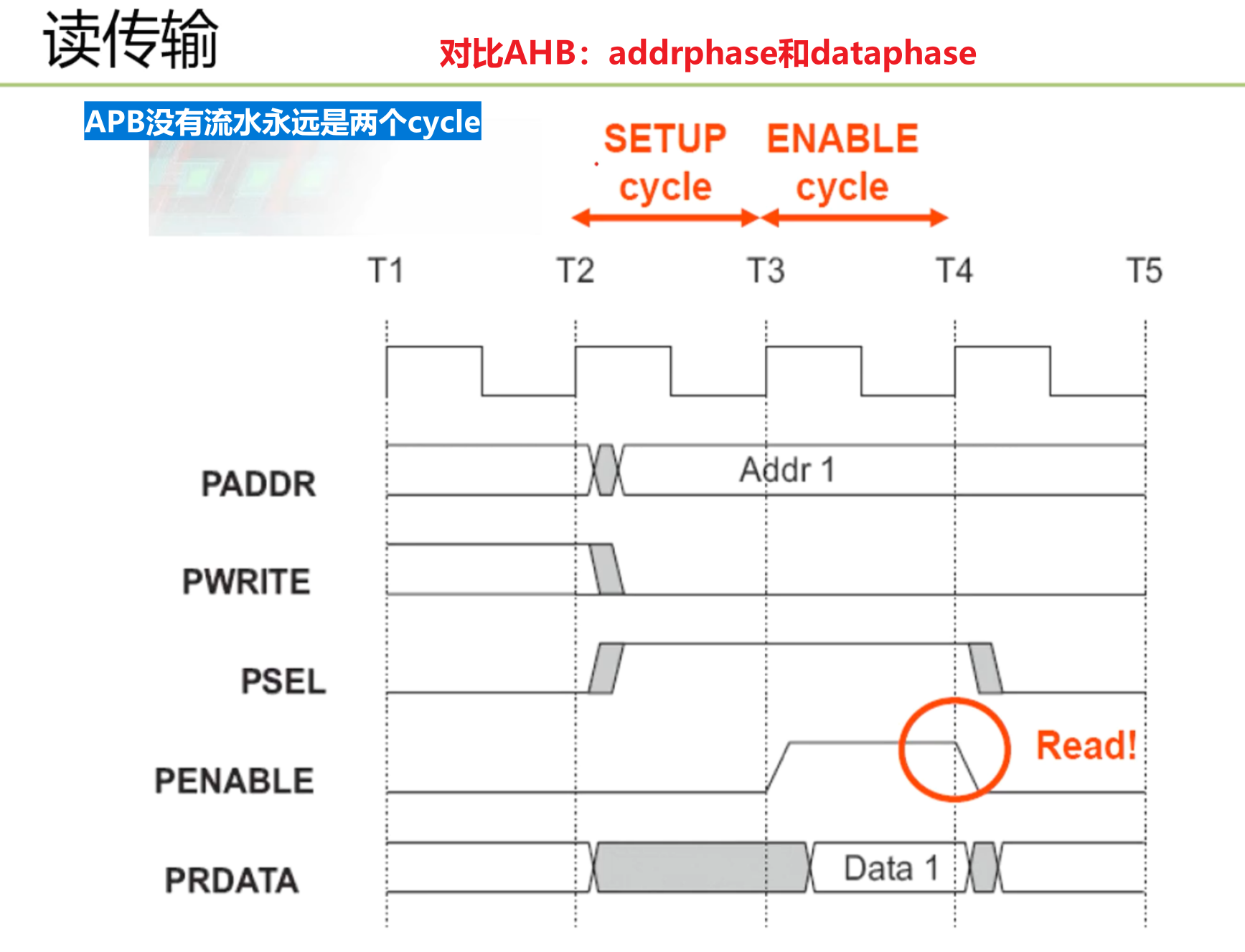

APB补充——读是在ENABLE阶段

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!