EDA入门

0 前言

世界三大EDA厂商一般指的是Cadence, Synopsys. Mentor Graphics

数字IC前端设计:

- 以RTL设计为起点,以生成可以布局布线的网表为终点;

- 主要是实现用设计的电路实现想法

前端设计主要包括:

- 基本的RTL编程和仿真

- C系统设计

- 功能验证

- 综合

- 静态时序分析

- 逻辑等值验证

做IC前端设计常用的是Synopsys家的EDA工具:

- 仿真使用的VCS(verilog compiled simulator)

- 综合使用的DC(Design Compiler)

- 时序分析使用的PT( PrimeTime)

其他EDA工具也有很多,如布线布局使用的ICC(IC Compiler),做物理验证的Herclues等

这里主要介绍下前面提到的VCS,DC,PT这三者

1 VCS(Verilog Compiled Simulator)

VCS是编译型Verilog模拟器,它完全⽀持OVI标准的Verilog HDL语言、PLI和SDF。 VCS具有目前行业中最高的模拟性能,其出色的内存管理能力足以支持千万门级的ASIC设计,而其模拟精度也完全满足深亚微米ASIC Sign-Off的要求。VCS结合了节拍式算法和事件驱动算法,具有高性能、⼤规模和高精度的特点,适⽤于从行为级、RTL到Sign-Off等各个阶段。VCS已经将CoverMeter中所有的覆盖率测试功能集成,并提供VeraLite、CycleC等智能验证方法。VCS和Scirocco也⽀持混合语言仿真。VCS和Scirocco都集成了Virsim图形用户界面,它提供了对模拟结果的交互和后处理分析。

2 DC

Design Compiler为Synopsys公司逻辑合成⼯具。DC得到全球60多个半导体⼚商、380多个⼯艺库的支持。据最新Dataquest的统计,Synopsys的逻辑综合工具占据91%的市场份额。DC是十多年来工业界标准的逻辑综合工具,也是Synopsys最核心的产品。它使IC设计者在最短的时间内最佳的利用硅片完成设计。它根据设计描述和约束条件并针对特定的工艺库自动综合出⼀个优化的门级电路。它可以接受多种输⼊格式,如硬件描述语言、原理图和网表等,并产生多种性能报告,在缩短设计时间的同时提⾼设计性能。Synopsys发布的最新版Design Compiler综合解决方案——Design Compiler。新版本扩展了拓扑技术,以加速采用先进低功耗和测试技术的设计收敛,帮助设计人员提高生产效率和IC性能。拓扑技术可帮助设计人员正确评估芯片在综合过程中的功耗,在设计早期解决所有功耗问题。此外,还支持Design Compiler中新的测试压缩技术,在实现⾼质量测试的同时,减少测试时间和测试数据量超过100倍,并减少后续物理实现阶段由于测试电路带来的可能的布线拥塞。新的Design Compiler采用了多项创新综合技术,如自适应retiming和功耗驱动门控时钟,性能较以前版本平均提⾼8%,⾯积减少4%,功耗降低5%。此外,Synopsys Formality等效检测解决⽅案得到了增强,能够独立、彻底地验证这些技术,因此设计者⽆需舍去验证就可以实现更高的性能。

3 PT

PrimeTime是针对复杂、百万门芯片进行全芯片、门级静态时序分析的工具。PrimeTime可以集成于逻辑综合和物理综合的流程,让设计者分析并解决复杂的时序问题,并提高时序收敛的速度。PrimeTime是众多半导体厂商认可的、业界标准的静态时序分析工具。Galaxy™ 设计平台中的时序验证核心工具—PrimeTime®的最新版本凭借其静态时序分析能力和对数百万门设计进行认可的能力,成为新的时序工具标准。从用户使用情况显示,最新发布的PrimeTime的运行速度比之前版本平均提高了2到7倍,从而提升了设计者的设计能力,并实现快速的时序认可。PrimeTime强大的性能得益于在生成报告和基于标准延迟文件(SDF)的时序分析方面的算法的改进。PrimeTime提供全芯片级的静态时序分析,同时整合了延迟计算和先进的建模功能,以实现有效而又精确的时序认可。PrimeTime SI是全芯片门级信号完整性分析工具。PrimeTime SI建立在成功流片验证过的PrimeTime平台之上的,提供精确的串扰延迟分析,IR drop(电压降落)分析和静态时序分析。PrimeTime SI业界领先的超快运⾏时间和处理容量让数百万门的复杂设计⼀次流片成功,让设计者取得极快的进⼊市场时间

总结

1 | |

安装

- SCL11.9 —— Synopsys官方的管理License文件的软件

- VCS2016 —— Verilog仿真软件

- Verdi2016 —— 一款可以生成仿真波形的软件,验证工程师必备

- Formality2015 —— 形式化验证软件

- SpyGlass2016 —— 有五大模块: lint,CDC,LP,Constraint,DFT,功能强大

- Primetime2016 —— 针对STA(静态时序分析)的软件

- Design complier2016 —— 用于做电路综合的核心工具

- Installer3.2 —— Synopsys官方的安装软件,以上软件除SpyGlass外,均用它安装

- License —— 用来生成license的文件

Ubuntu VCS安装

1.所有文件放到一个非中文目录!否则dve打开时swf文件会找不到

2.先安装installer

解压后,运行.run文件,之后会提示installer安装目录的指定

3.再安装scl进行破解

点就完了

4.生成破解文件(具体破解过程参考链接)

5.license生成、环境以及激活

启动scl_keygen生成器

这个需要在window下进行,双击运行scl_keygen.exe.

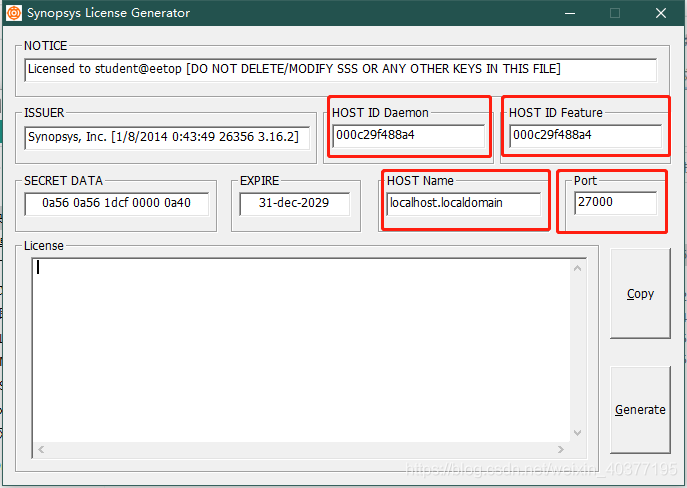

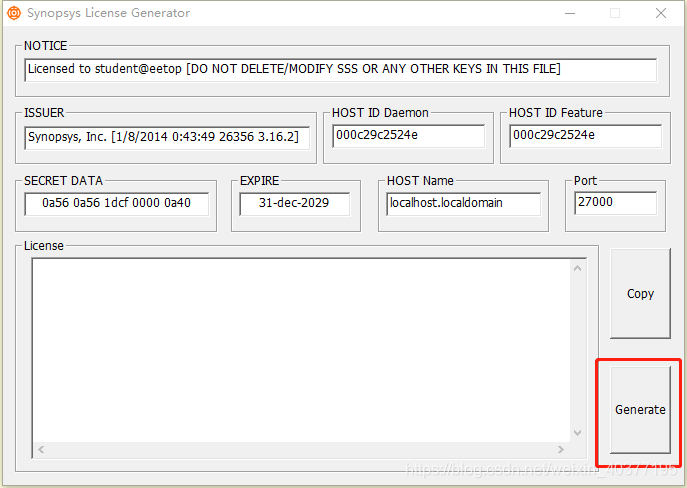

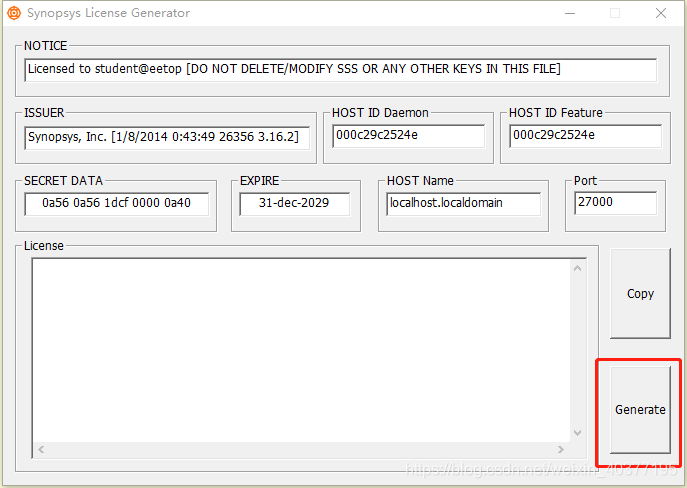

需要填写这4项信息,HOST ID Daemon 和HOST ID Feature填写一样的,Port选择27000。

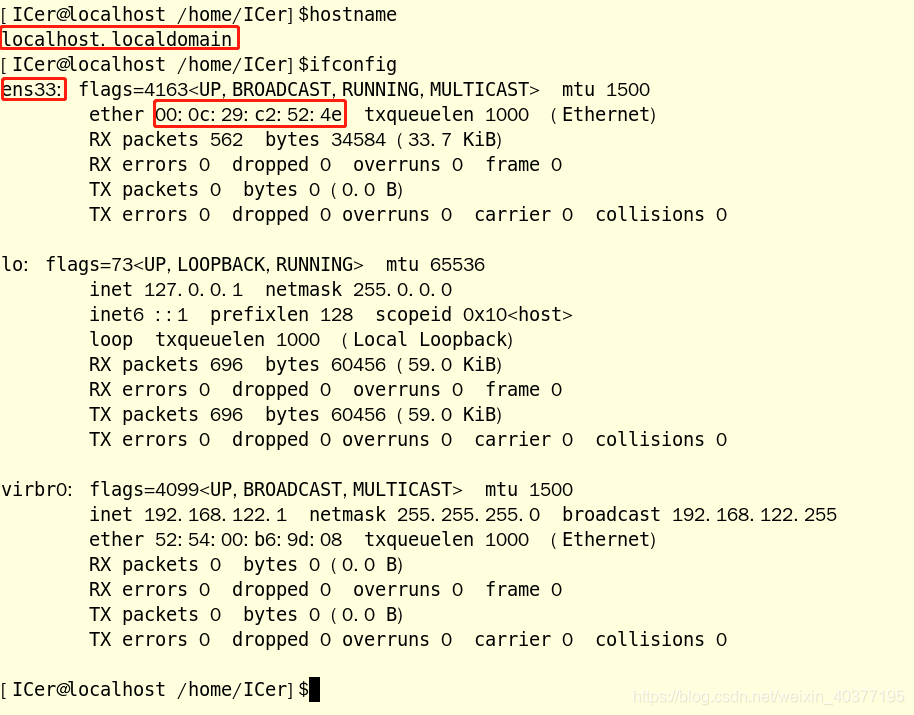

进入虚拟机,打开terminal使用以下命令查找

2hostname

ifconfig我的填写如下,然后点击Generate生成license

打开生成licens文件,修改第二行,这个需要与虚拟机里面scl路径一致,不然license无效。修改好后把这个文件复制到共享文件中。这个文件最后需要放到这个“scl/2018.06/admin/license/”目录下,要与环境里面设置的路径一致

5.设置bashrc

打开.bashrc环境文件,加入以下内容,对应自己安装路径。但是需要注意倒数第二行,需要确认主机名是否正确。保存退出,source一下

我的bashrc:

1 | |

6.激活(每次重启都要重新激活)

先使用以下命令设置开放端口:

1 | |

然后在输入“lmg_synopsys”进行激活,这个每次启动虚拟机都需要这样操作一下。但是这里提示缺少依赖库。输入以下命令进行安装:

1 | |

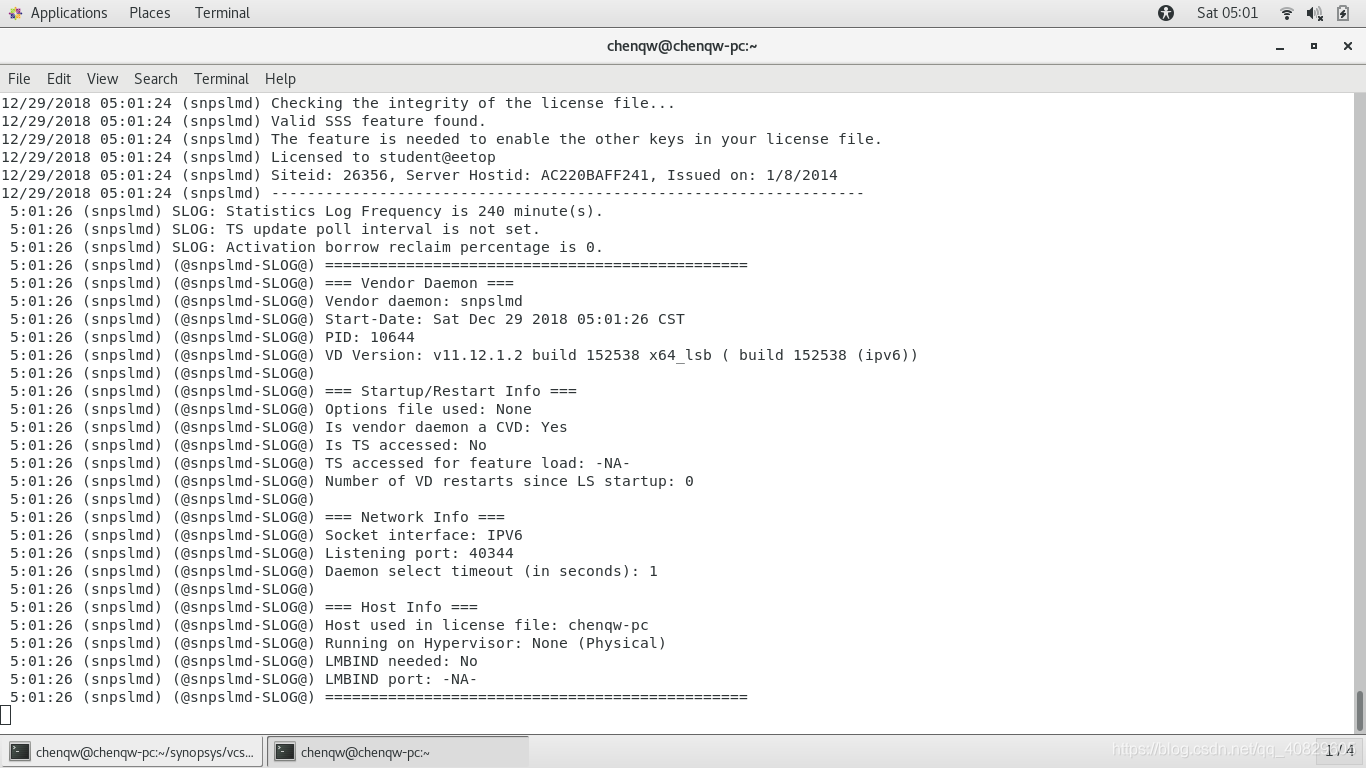

success图示:

几个推荐链接

- ubuntu18.04安装VCS+verdi错误集锦 https://blog.csdn.net/ciscomonkey/article/details/105119397

- VCS+verdi /dve 仿真环境搭建-问题汇总 https://blog.csdn.net/u010451780/article/details/121018902

- synopsys软件安装 https://blog.csdn.net/sinat_39901027/article/details/116094393

alias lmg_synopsys="lmgrd -c /home/tools/synopsys/license/license.dat"alias dve="dve -full64"

- CentOS下安装Synopsys Design Compiler软件避坑指南 https://blog.csdn.net/weixin_43249158/article/details/123406736

- dc打不开GUI界面的问题

- ubuntu 18.04 vcs2016 安装记录 https://blog.csdn.net/weixin_30405421/article/details/96531035

- 比较一般,可以不看

- 【强烈建议参考!】VCS+Verdi 安装及破解过程(Ubuntu)【1】 https://blog.csdn.net/huayangshiboqi/article/details/89525723

- 【强烈建议参考!】success图示,lsb_core安装,/usr/tmp/,以及其他很多问题的解决方案,gcc参数等 | VCS+Verdi 安装及破解过程(Ubuntu)【1】_huayangshiboqi的博客-CSDN博客_ubuntu vcs安装

- 【强烈推荐参考2!】数字IC设计的第一步——Synopsys EDA Tools的安装https://www.cxyzjd.com/article/qq_33589780/108720685

- 全部EDA的bashrc都有,而且DC的错误也有解决办法

- VCS2018在Ubuntu20 18安装步骤 https://blog.csdn.net/qq_41717683/article/details/122267191

- 比较详细

- export VCS_TARGET_ARCH=”amd64”

- lmgrd安装

- 更改License日期

- RISCV学习笔记5.2—ubuntu18.04安装芯片设计软件(vcs、verdi)的正式安装过程 https://blog.csdn.net/qq_41735476/article/details/125245329

- 一步一步来的,还可以

VCS Verdi安装问题

verdi缺少库

1 | |

解决指令:

1 | |

参考链接:

- https://www.linuxuprising.com/2018/05/fix-libpng12-0-missing-in-ubuntu-1804.html

- https://blog.eetop.cn/blog-1789771-6950474.html

lmgrd can’t make directory /usr/tmp/.flexlm when running server on Ubuntu问题:

这个问题,可以参考这个链接http://www.myir-tech.com/faq_list.asp?id=521

就是:

1 | |

生成fsdb时需要的链接

- 方法一,vcs编译的时候使用,进行手动链接

1 | |

- 方法而,vcs编译的时候使用如下参数,自动链接

1 | |

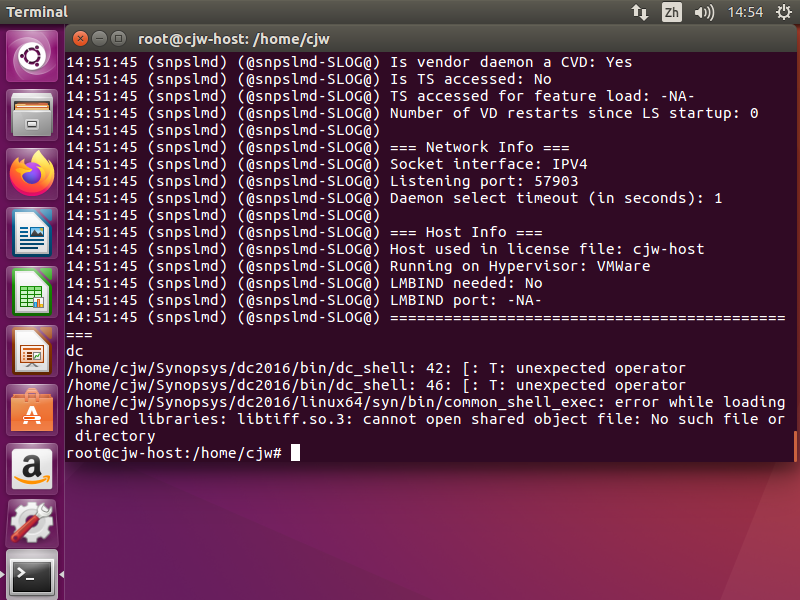

DC安装问题

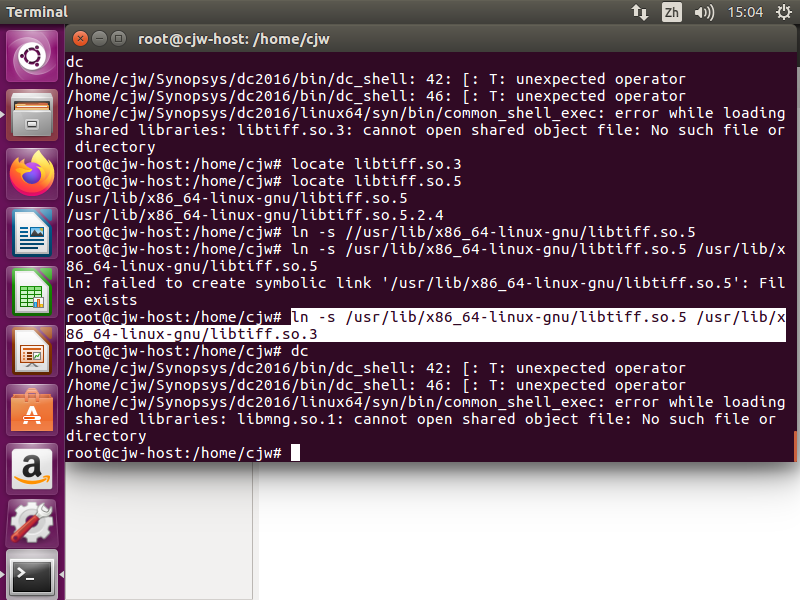

输入dc,会有以下的错误出现,关于libtiff.so.3

由于Ubuntu16.04已经安装了libtiff.so.5,这个文件可以在/usr/lib/x86_64-linux-gnu/下找到,输入locate libtiff.so.5即可找到它的路径

接下来直接做一个软链接即可

1 | |

接着输入dc,又出现一个错误,关于libmng.so.1

解决方案也和上面差不多

可以先安装libmng2,如果已存在,就直接软链接到libmng.so.1

1 | |

我的第一个VCS+VERDI联调

参考文章

- https://blog.csdn.net/qq_41717683/article/details/122267191

- https://blog.csdn.net/mu_guang_/article/details/109549444

VCS 各种参数

1 | |

主要内容

1 | |

写一个简单的加法器

add.v

1 | |

test.v

1 | |

Makefile

假设你已经装上的 make 和 gcc,且熟悉make编译规则

1 | |

生成.fsdb有两种方法,一种是在vcs编译时生成,需要在tb顶层添加下面两个系统函数,然后在用verdi加载波形文件

1 | |

第二种方法是通过verdi界面生成fsdb。编译完后通过输入下面命令

1 | |

打开verdi界面,然后在verdi命令行输入run,也可以生成.fsdb文件,但是这种方法比较麻烦,而且每加一个变量都得重新run,不然看不到这个变量的波形。所以一般采用第一种方式

也可以通过输入下面命令通过dve仿真

1 | |

其他问题

VCS

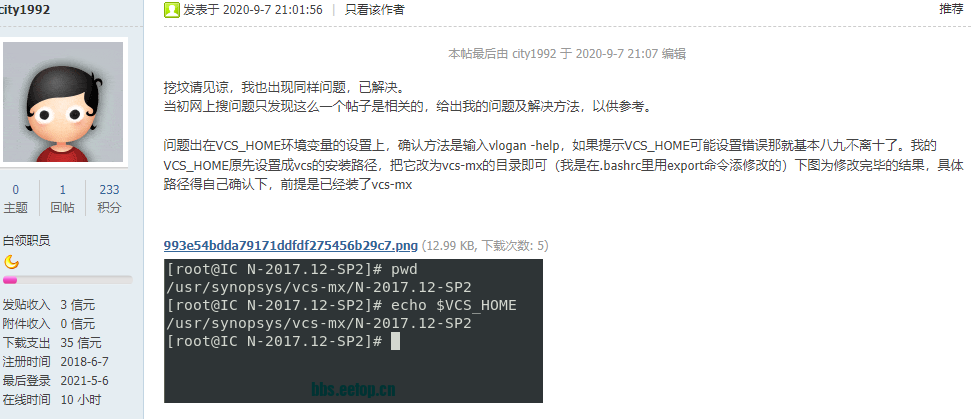

1 vlogan找不到

编译程序失败,打印消息如下

1 | |

解决方法:改VCS_HOME路径

参考链接:https://bbs.eetop.cn/thread-842862-1-1.html

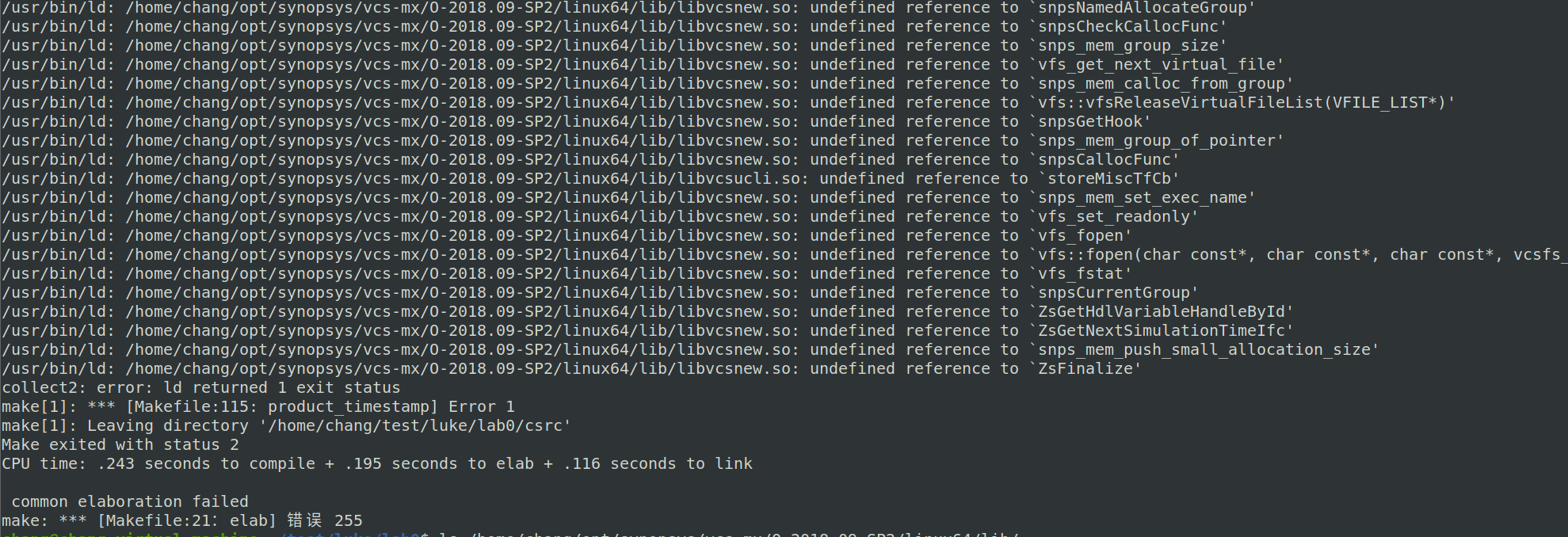

2.ubuntu进行vcs编译时:libvcsnew.so:underfined reference to xxx

ubuntu上进行vcs编译时报错libvcsnew.so:underfined reference to xxx,问题原因是默认情况下 gcc 在 Debian/Ubuntu 上使用的链接器选项与在 Fedora 上使用的链接器选项略有不同(这是测试 VCS 的平台)

解决方法:编译添加参数-LDFLAGS -Wl,--no-as-needed

参考链接:

① 解决方法链接:https://blog.csdn.net/kissdragan/article/details/128599150

② 原因链接:https://github.com/chipsalliance/rocket-chip/issues/21

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!