verilog代码风格——入门

代码风格——入门

A. 入门内容

总结于:https://www.bilibili.com/video/BV1uq4y1q7DJ

signal

- Use lower case for signal name, for example

- tx_fifo_rd √

- Tx_Fifo_Rd ×

- low activve reset

- rst_ √

- rst ×

- 全局信号应该被清晰地命名包括源信息的名称,例如一个由dma指向mem的requset_read信号可以命名为:

- dma_mem_req_rd √

- mem_req_rd ×

clock

- 所有不同模块的时钟信号应该直接来自同一个clk generation block

- 使用posedge clk而不是negedge clk

- 一个模块中只应该有一个clk(即同步处理)

- 如果涉及到异步(其他输入时钟),请在另外的前面的模块中同步好,不要在一个里面用好几个clk,如果用了好几个clk在后端做时序的时候做时钟树不太友好

模块分类

- put custom/semi=custom layout circuit into seqparate module. For ex.

- rom ram register+file …

- Put synthesis sensitive circuit which need to be finePut synthesis sensitive circuit which need to be fine tuned into separate modules.

- Put non-synthesizable circuit which need to bePut non-synthesizable circuit which need to be manually edited into separate modules. For ex. pad, PLL, clk driver, delay_cell, spare_gate. For ex.

- pad, PLL, clk driver, delay_cell, spare_gate

- 可以通过文件夹把这些类型分开

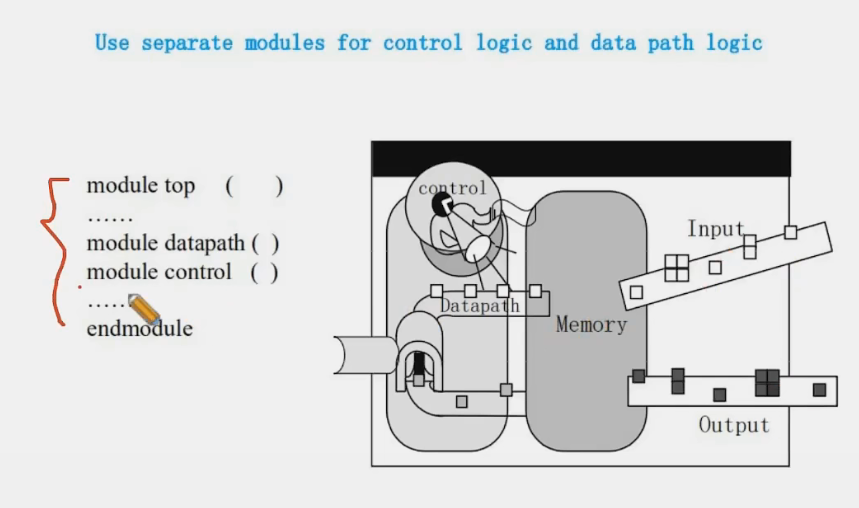

Use separate modules for control logic and data path logic

- 一开始模块划分时,高内聚,低耦合,模块之间的连接少一点,多一点模块内的连接

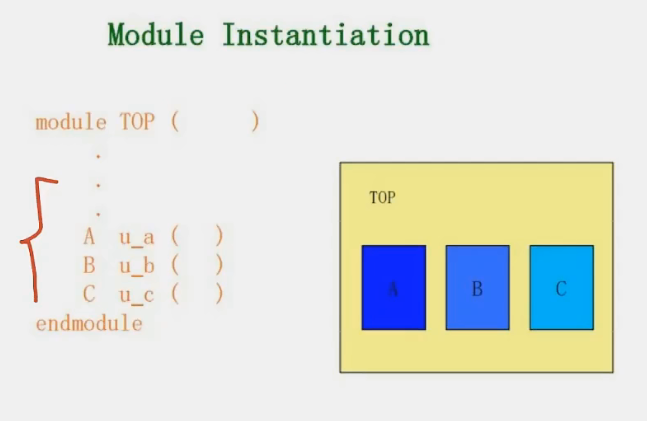

模块例化

- 没啥要强调的

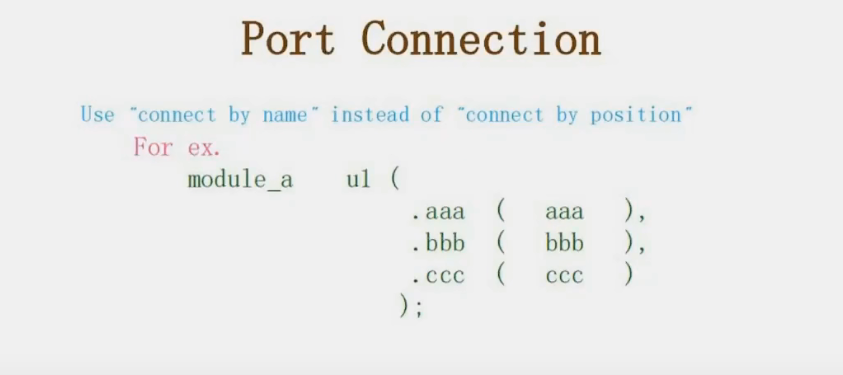

端口映射

- 尽量名字取一样

内部测试信号要引出来

- 引出来,不然Netlist标号后找不到

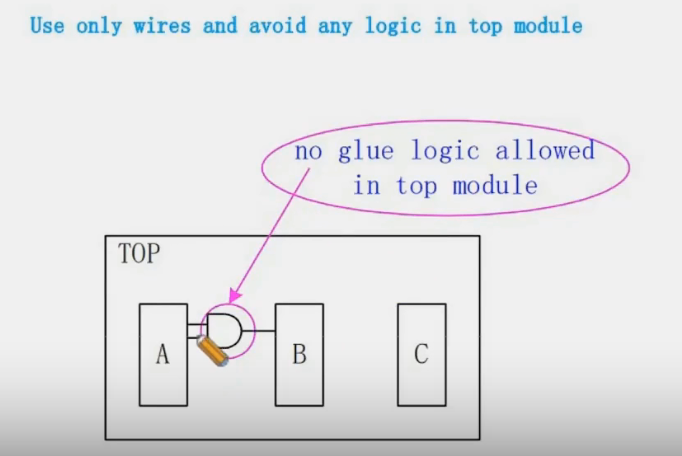

顶层模块直连就好

- 顶层模块直联就好,不要写逻辑

Delay

- 赋值时候插入delay模拟延迟

If Statement

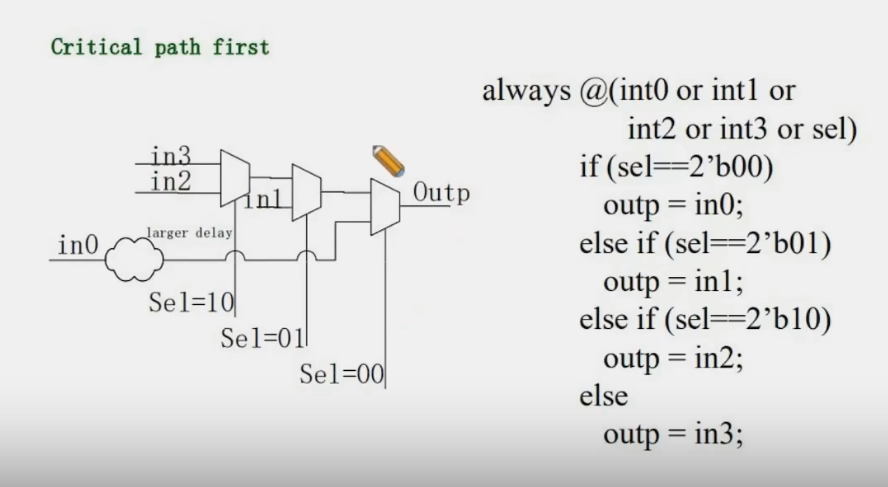

Critical path first关键路径优先

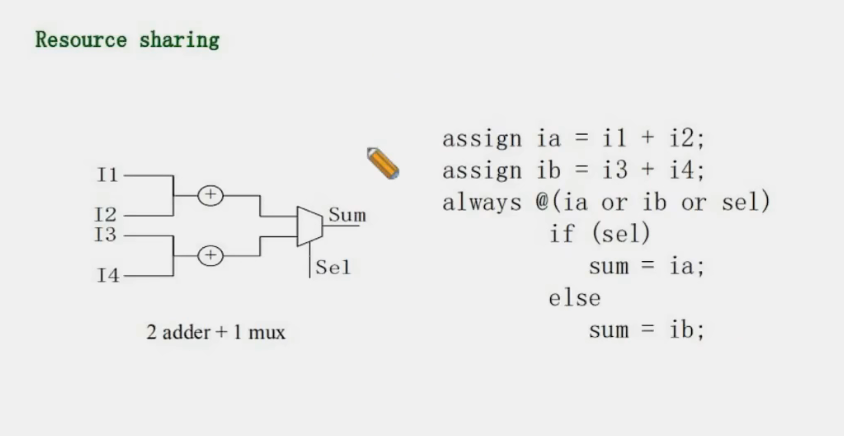

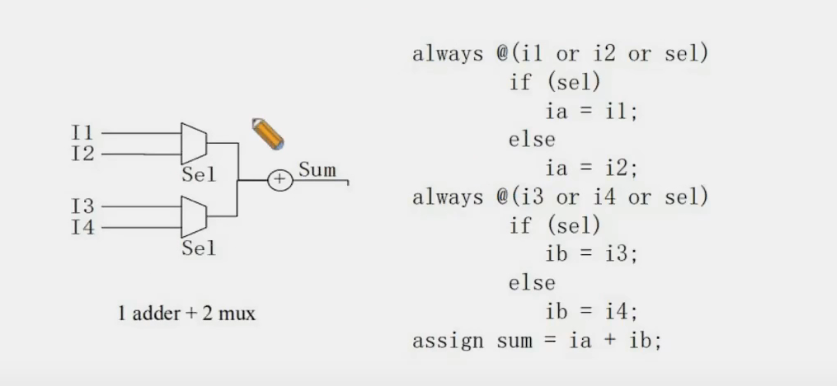

模块复用/资源共享

补齐else

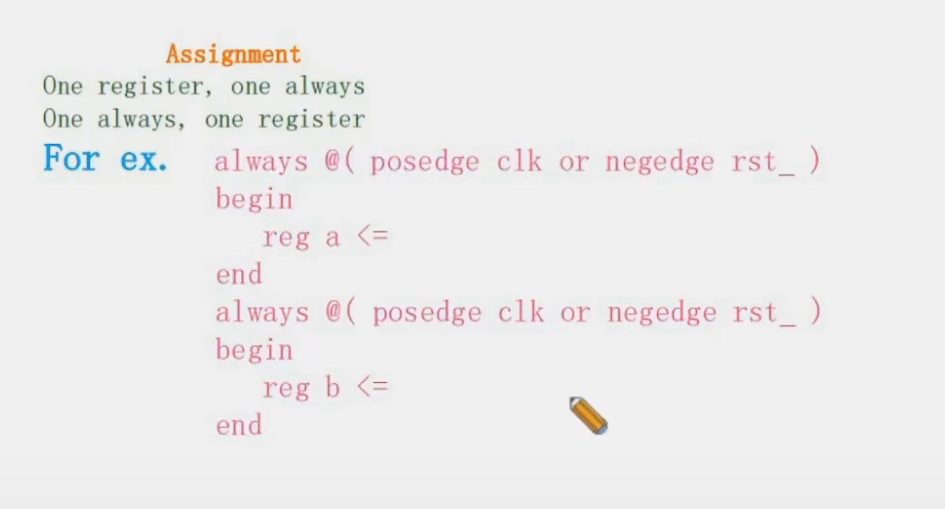

推荐一个always写一个reg

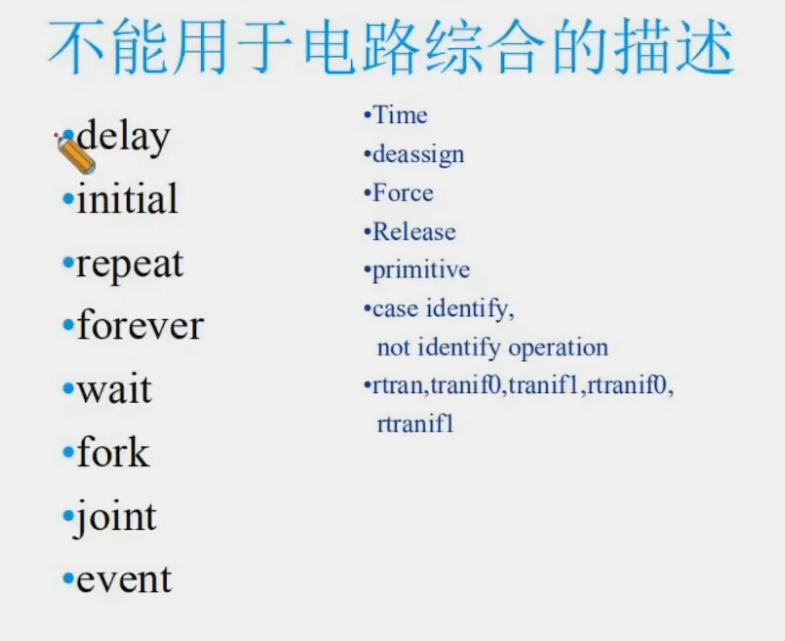

不能用于综合的语句

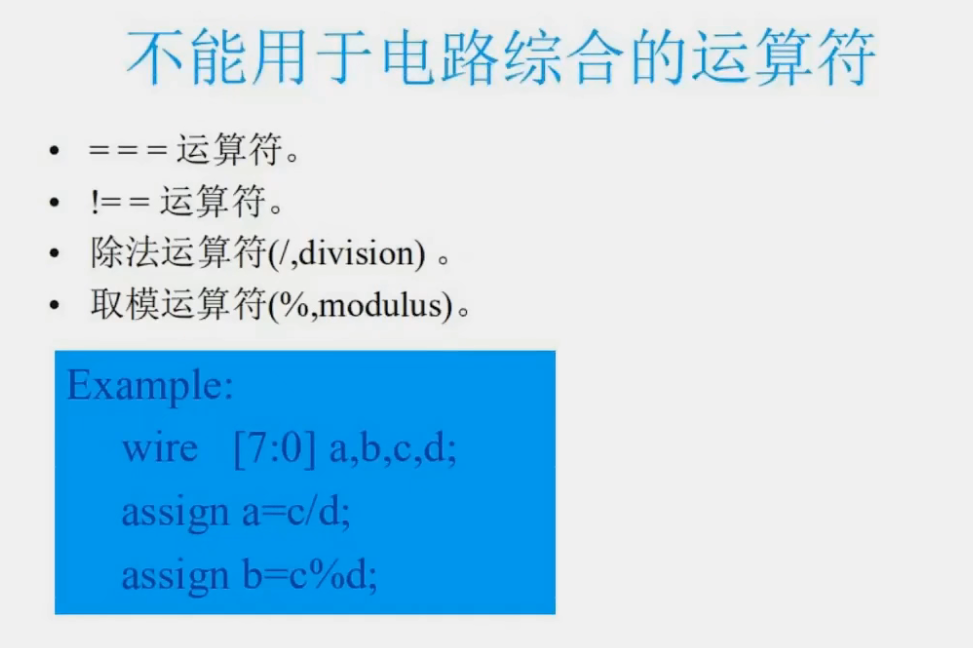

不能用于综合的运算符

- 设计里面两个==就好了

不能用于综合的基本单元

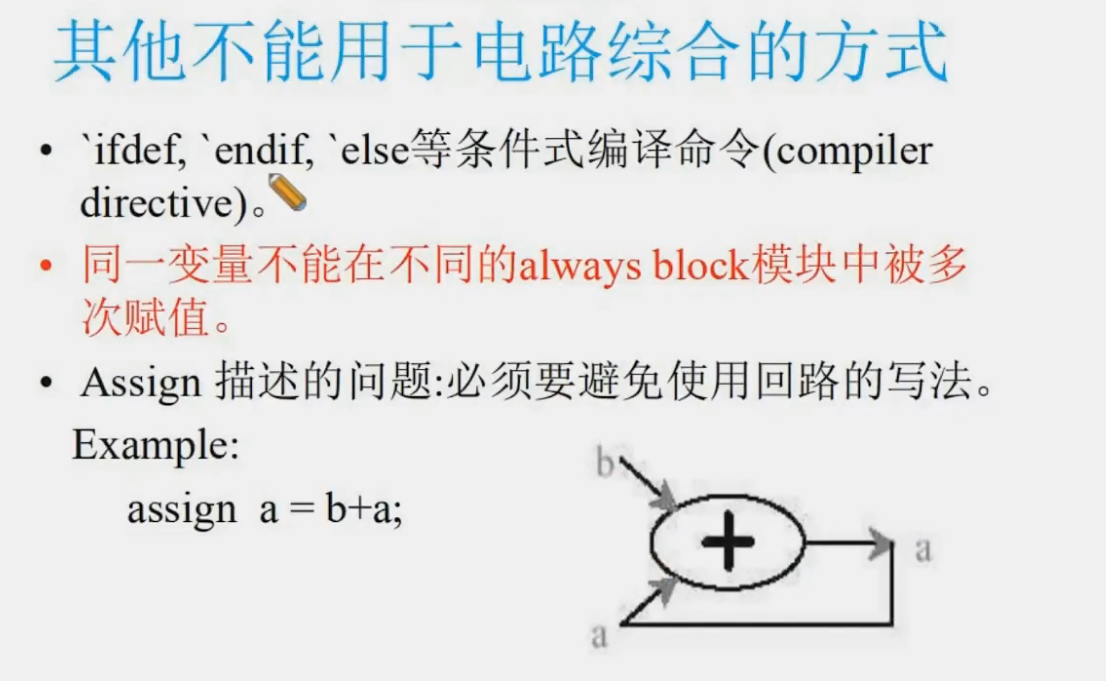

其他不能用于综合

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!