UVM入门进阶5(了解):TLM2与同步通信元件.md

参考文档链接:https://verificationacademy.com/verification-methodology-reference/uvm/docs_1.2/html/

本节目录:

- TLM2通信

- 同步通信元件

TLM2.0与UVM入门进阶5的双向通信都作为了解

1 TLM2.0通信(了解)

1.1 概述

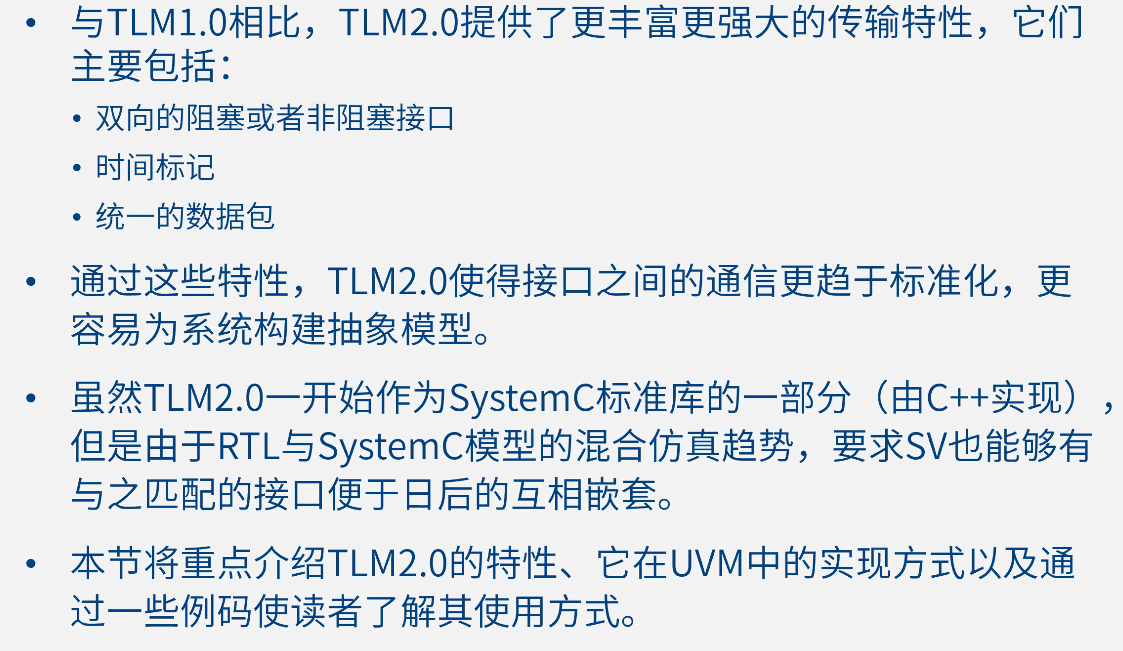

1.1.1 由TLM1.0到TLM2.0

- TLM1.0用UVM各个组件之间连接

- TLM2.0用于与SystemC进行连接

目前TLM开源包也是基于TLM2.0,且TLM2.0早于UVM成立的标准

1.1.2 对比、主要内容

什么时候用到TLM2.0,uvm与systemc做继承,把systemc作为reference model的时候

- 因为systemc是纯设计模型,没有时间概念

纯验证环境中不需要TLM2.0

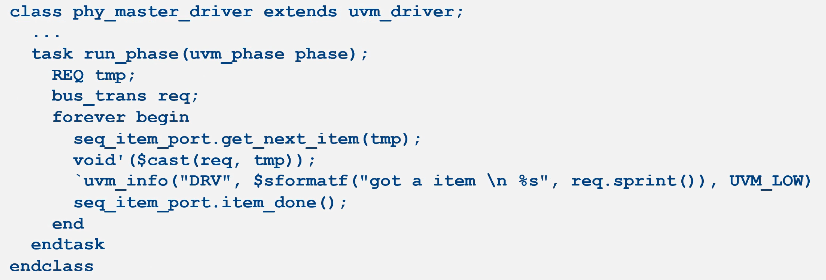

1.2 接口实现

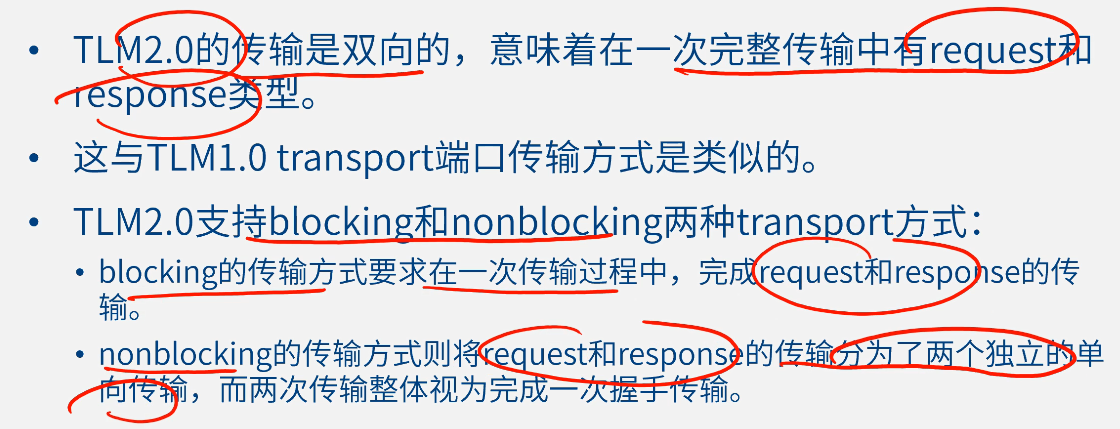

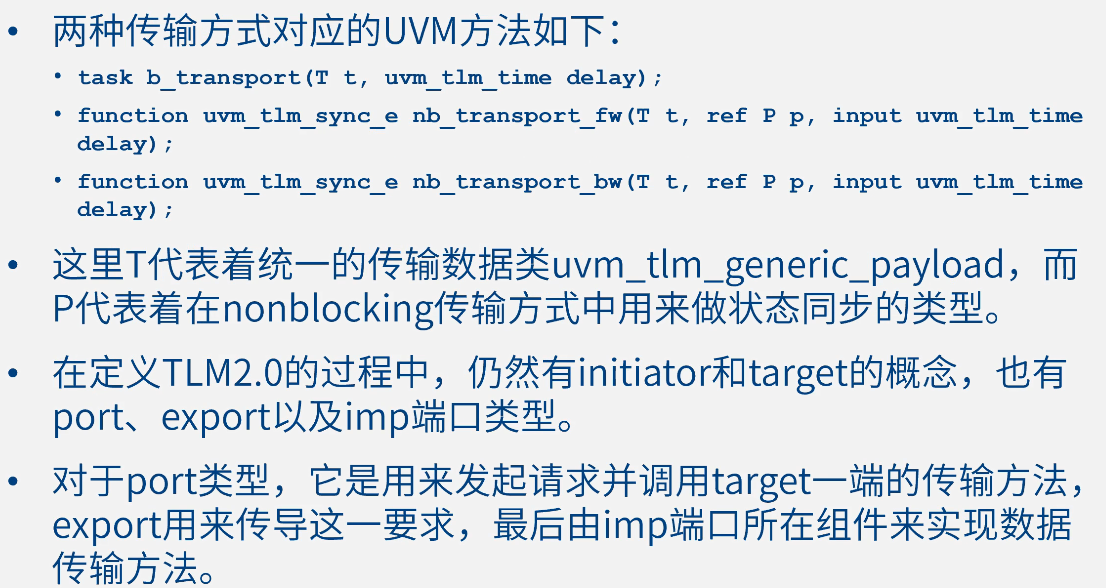

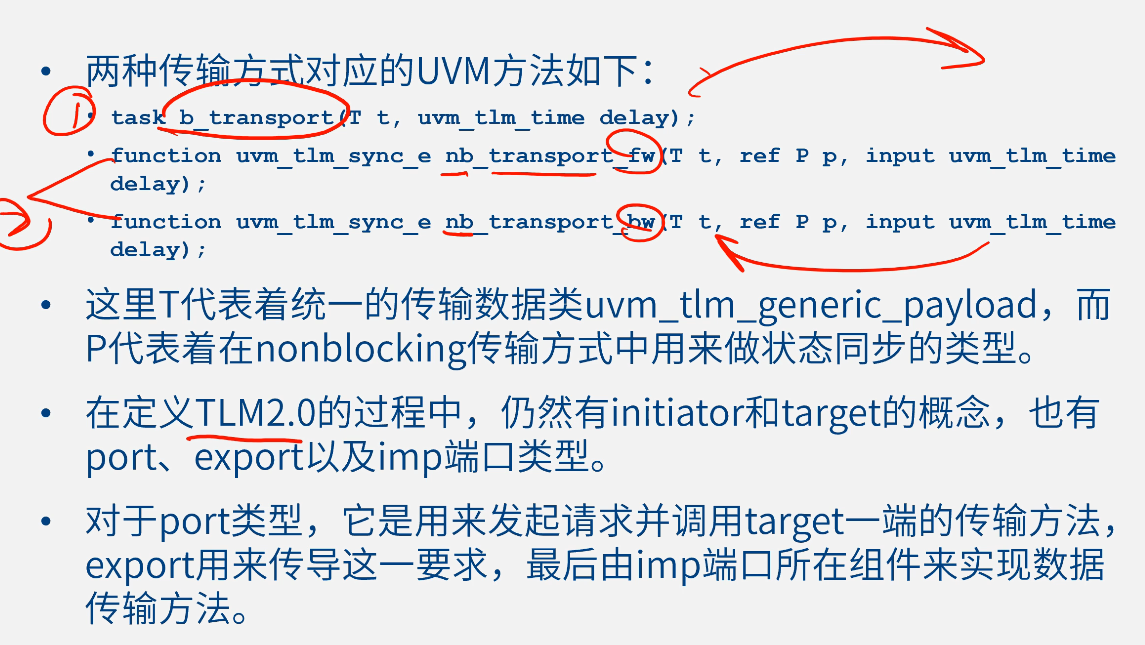

1.2.1 传输方法

两种方法:

- _fw:forward拿过来一个req

- _bw:backward拿过来一个rsp

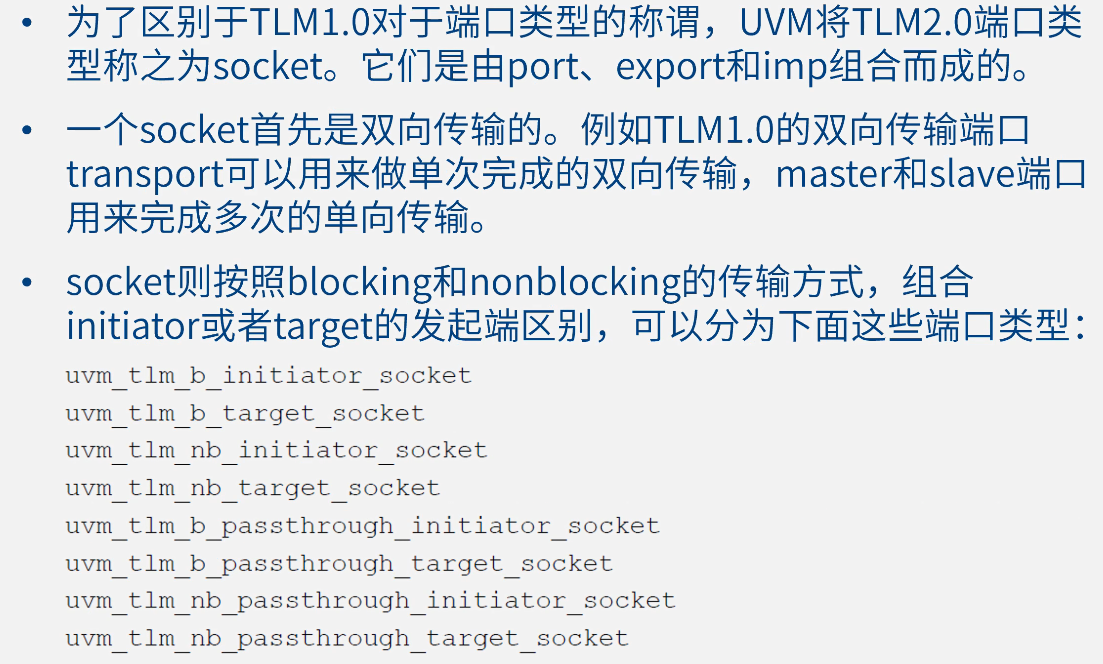

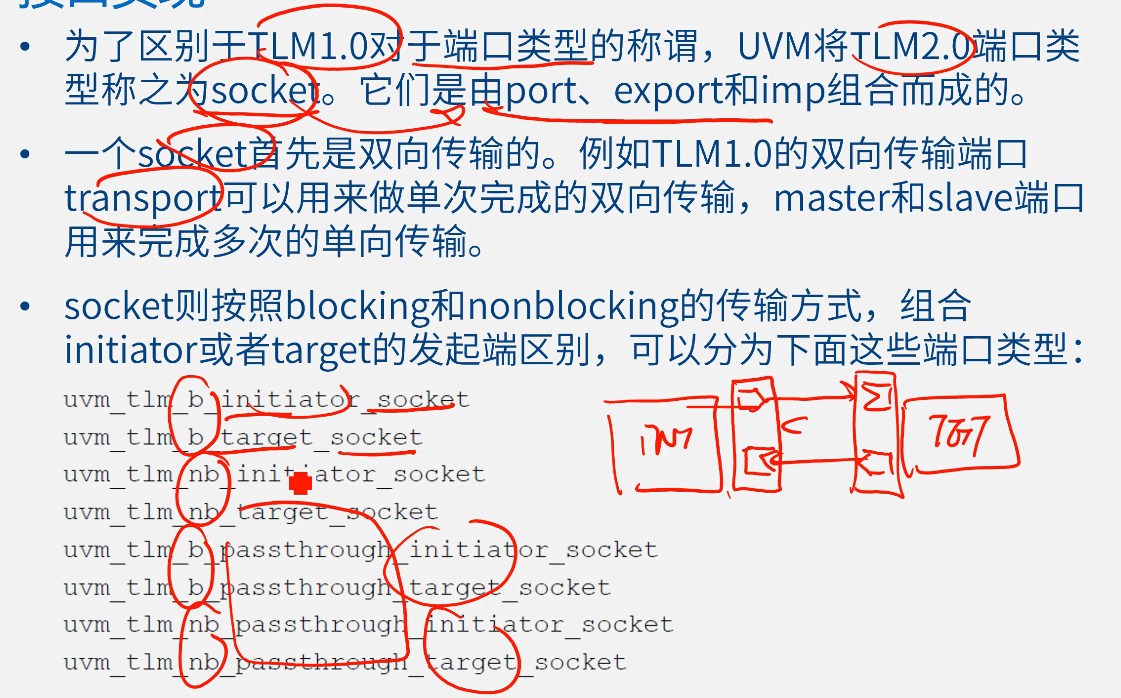

1.2.2 传输端口:端口类socket

socket由port,export和imp组合而成

1.2.3 端口类socket继承于uvm_port_base

1.3 传输数据

1.3.1 传输数据类型uvm_tlm_generic_payload

严格使用uvm_tlm_generic_payload类进行数据传输

这样才能与systemc无缝连接

1.3.2 uvm_tlm_generic_payload内部变量

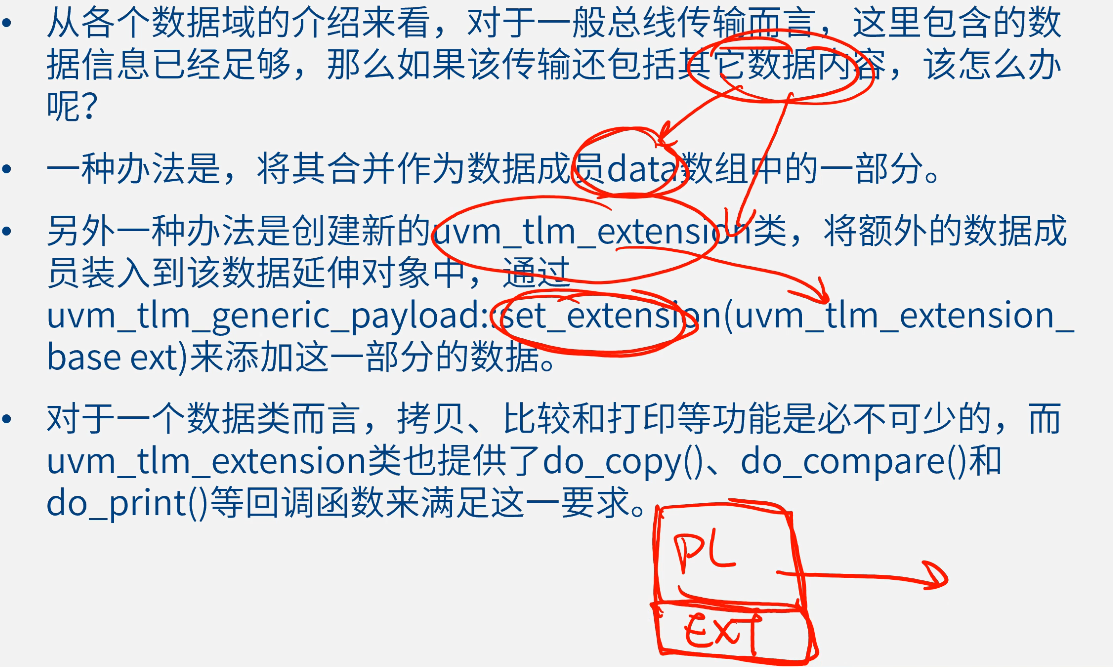

1.3.3 其他数据类型:两种解决方法

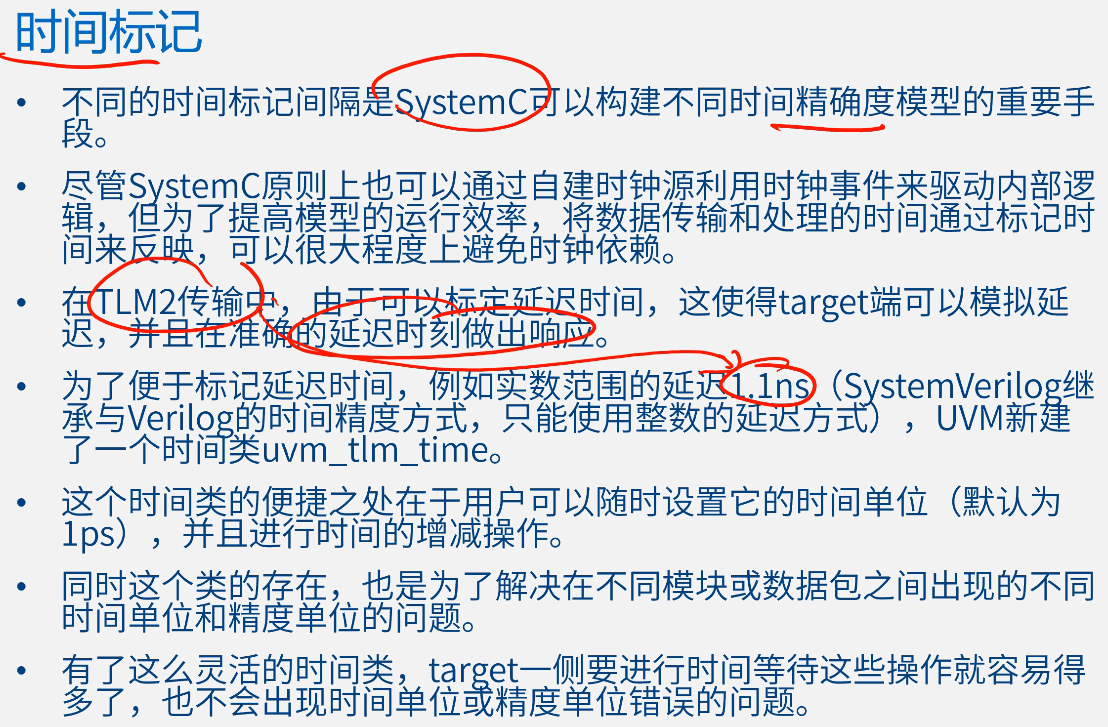

1.4 时间标记

1.4.1 uvm_tlm_tim

原则上systemc可以自己创建一些时钟,当我们很少这样做,因为会大幅度降低仿真效率

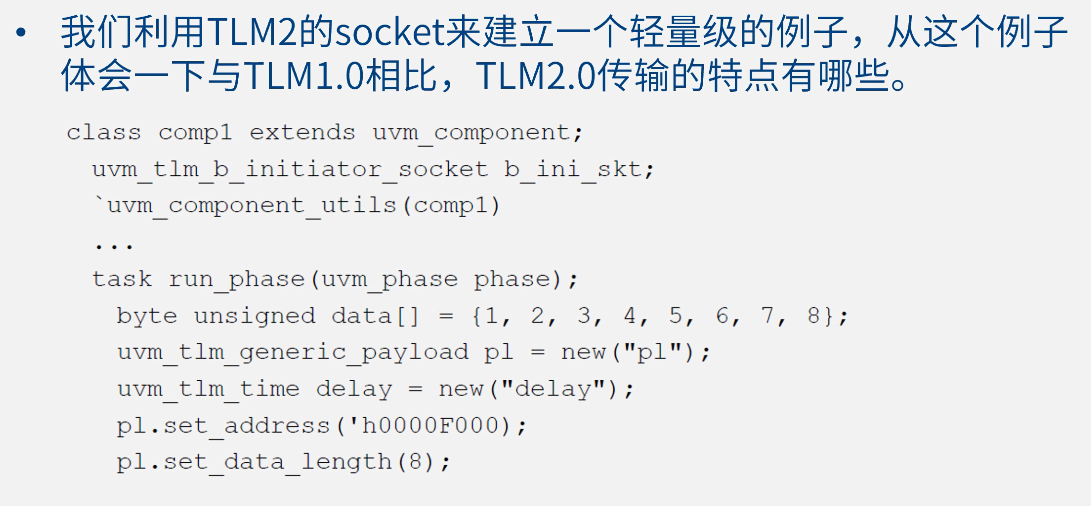

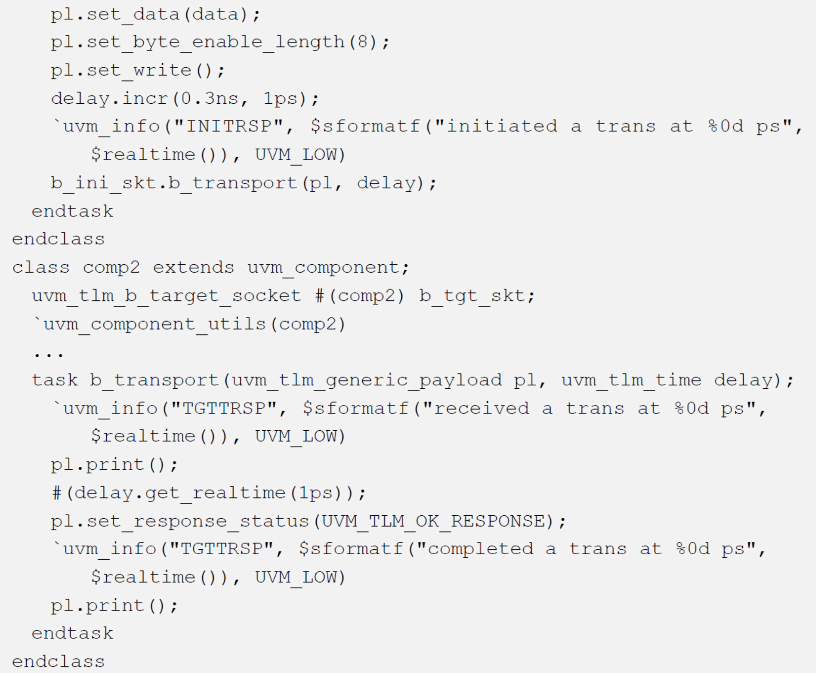

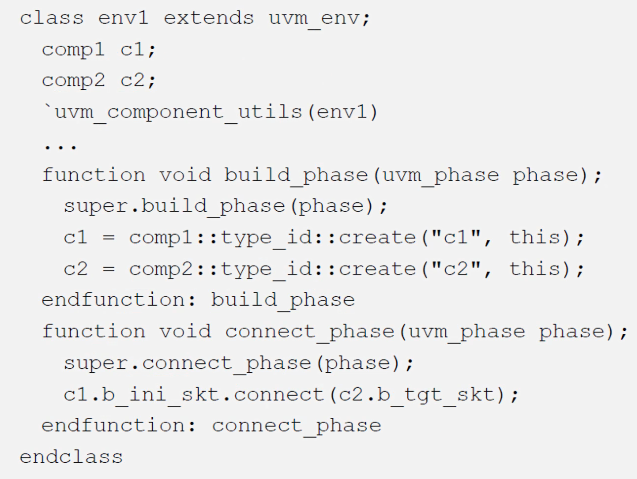

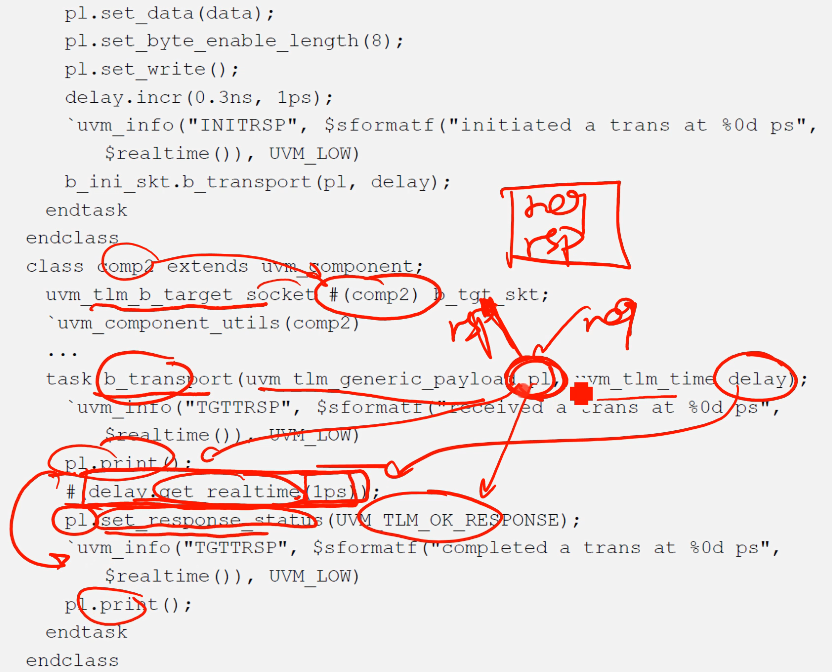

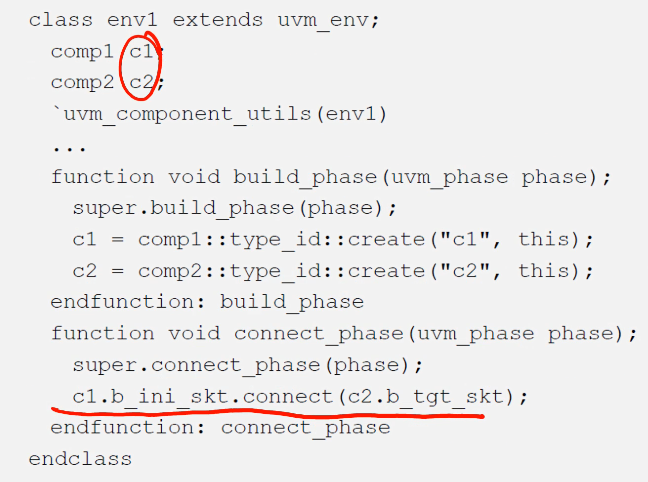

1.5 通信代码示例

- 数据类型固定所以不需要再指定数据传输类型

- 自始至终rsq与rsp都是一个对象

顶层代码:

1.6 通信代码示例(有标注版)

2 同步通信元件

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!